How the transistor is formed

A transistor and semiconductor technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of complex formation process and unstable transistor performance, and achieve the effect of simplifying process steps.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

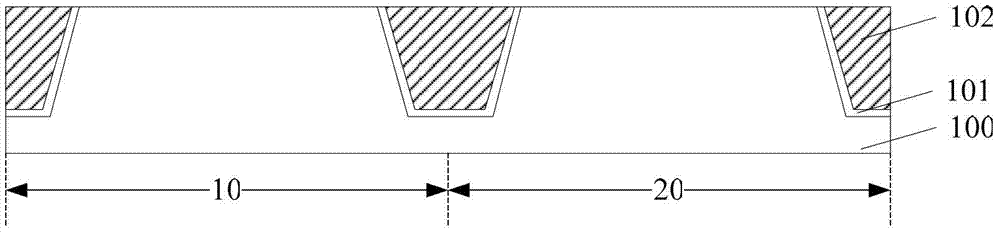

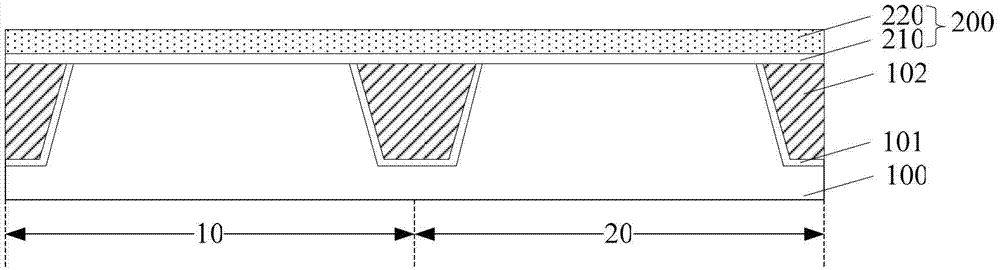

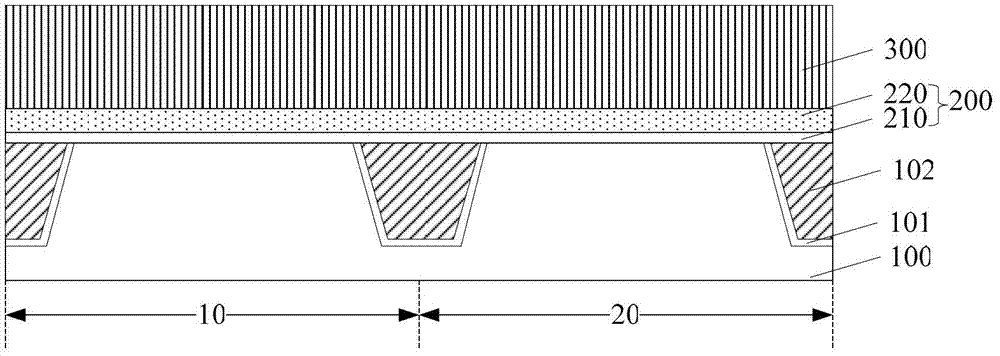

[0033] As mentioned in the background art, the process steps of forming transistors with gate dielectric layers of different thicknesses in the prior art are relatively complicated, and the performance of the formed transistors is not stable enough.

[0034] The inventors found that in the current process of forming a high-K metal gate transistor with a thinner gate dielectric layer by using the gate-last process, the process of removing the dummy gate dielectric layer generally adopts a wet etching process, because the dummy gate The materials of the dielectric layer and the dielectric layer are relatively close, and the material density of the dummy gate dielectric layer is generally greater than that of the dielectric layer, so in the wet etching process, the etching rate of the dielectric layer will be greater than that of the dummy gate dielectric layer. In the process of removing the dummy gate dielectric layer by wet etching process, a large loss will be caused to the di...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More