Passivation layer deposition method of high-voltage LED chip

A technology of LED chips and deposition methods, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems affecting the yield rate of high-voltage LED chips, broken bridges, etc., to reduce the tilt angle, avoid bridge breakage, and improve yield. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to enable those skilled in the art to better understand the technical solution of the present invention, the method for etching isolation grooves of GaN-based LED chips provided by the present invention will be described in detail below with reference to the accompanying drawings.

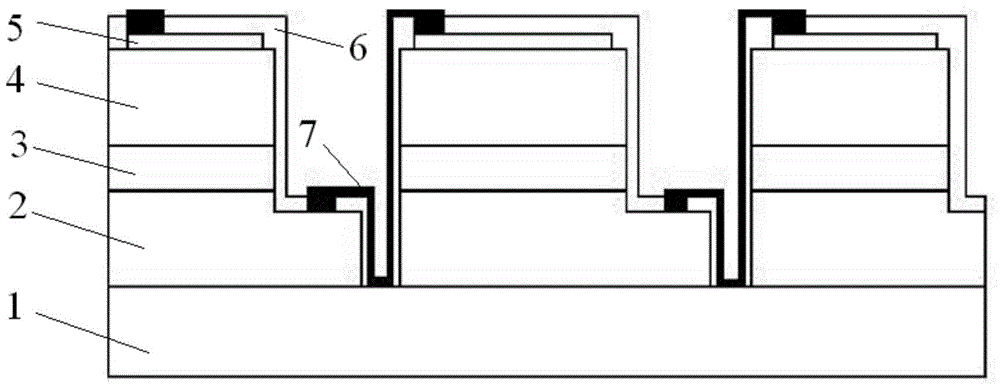

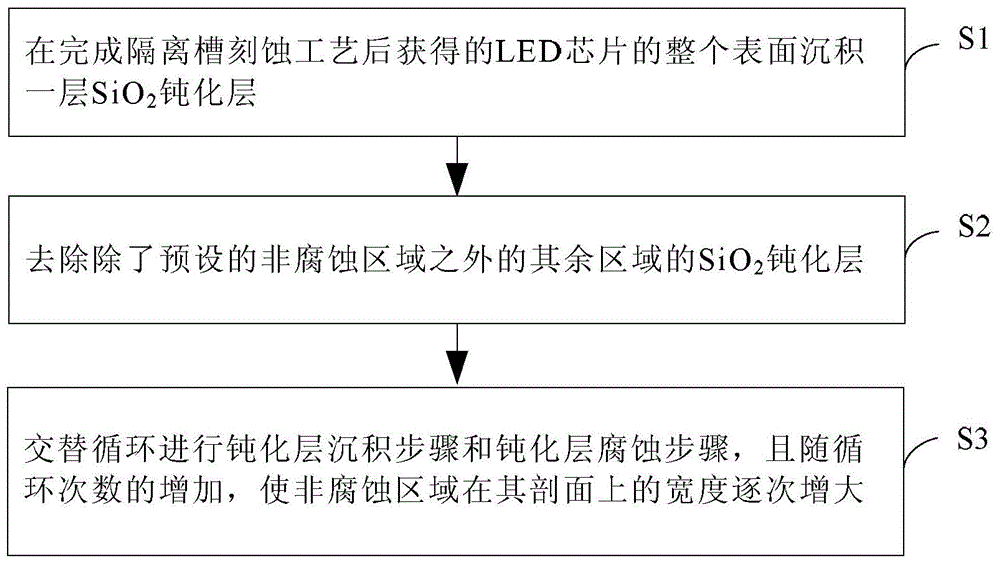

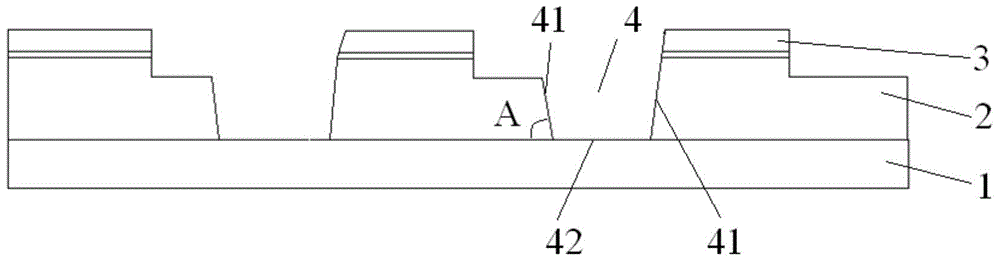

[0036] The passivation layer deposition method of the high-voltage LED chip provided by the present invention is carried out after the etching process of the isolation groove and before the evaporation process of the electrode connecting bridge, so as to deposit SiO on the surface of the LED chip. 2 passivation layer. After the etching process of the isolation groove is completed, the side wall of the isolation groove obtained is relatively steep, which makes it impossible for the electrode connection bridge to "climb" to the P electrode with a slightly higher height during the process of evaporating the electrode connection bridge, so that it is often There is a broken bridge. Thi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More