A planar grid igbt and its manufacturing method

A technology of planar gate and gate electrode, which is applied in the field of planar gate insulated gate bipolar transistors and insulated gate bipolar transistors, and can solve the problems of reducing device switching speed, device oscillation, electromagnetic radiation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

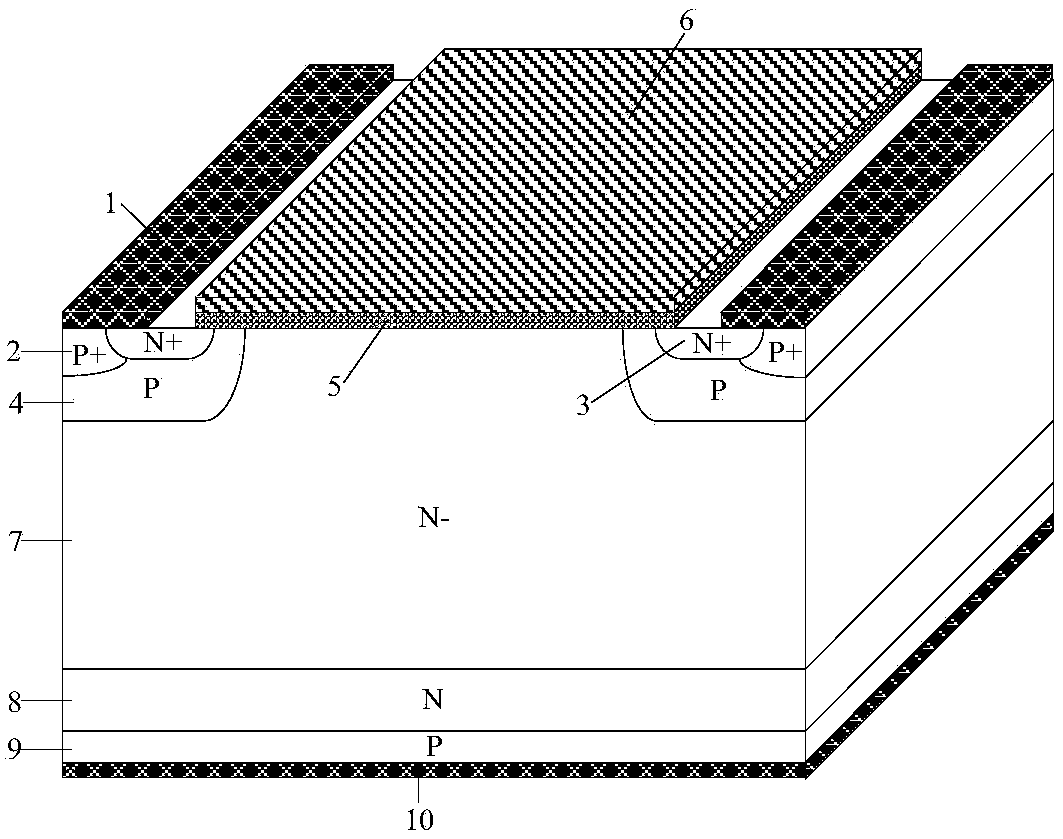

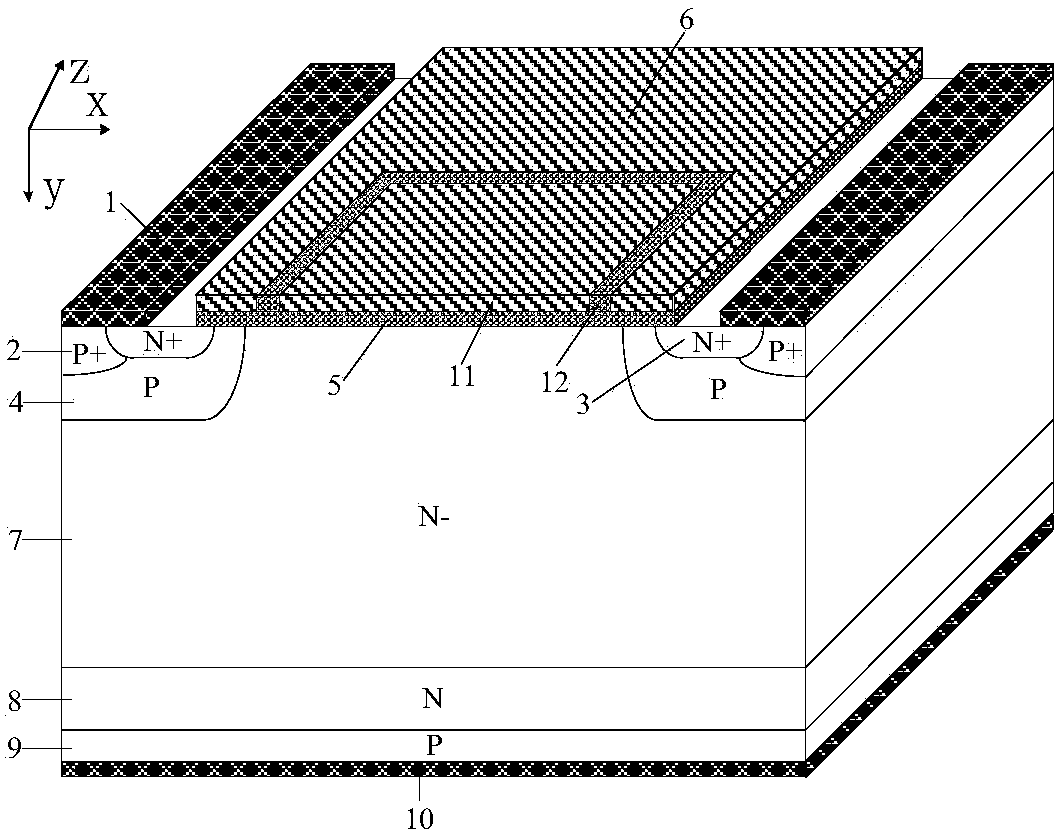

[0045] A planar gate IGBT with a half-cell structure such as figure 2 As shown, it includes: the back collector metal 10, the P-type collector region 9 located on the back collector metal 10 and connected to it, the N-type field stop layer 8 located on the P-type collector region 9 and connected to it, The N-drift region 7 located on the N-type field stop layer 8 and connected to it; the p-type base region 4 located on both sides of the upper part of the N-drift region 7 and connected to it, and the upper part of the p-type base region 4 and connected to each other Independent N+ emitter region 3 and P+ emitter region 2; emitter metal 1 located on the upper surface of N+ emitter region 3 and P+ emitter region 2; composite gate structure located on the semiconductor surface between emitter metal 1; characterized in that: The composite gate structure includes a dielectric layer 5 and a gate electrode 6, an electrode 11, and a dielectric layer 12 located on the dielectric layer ...

Embodiment 2

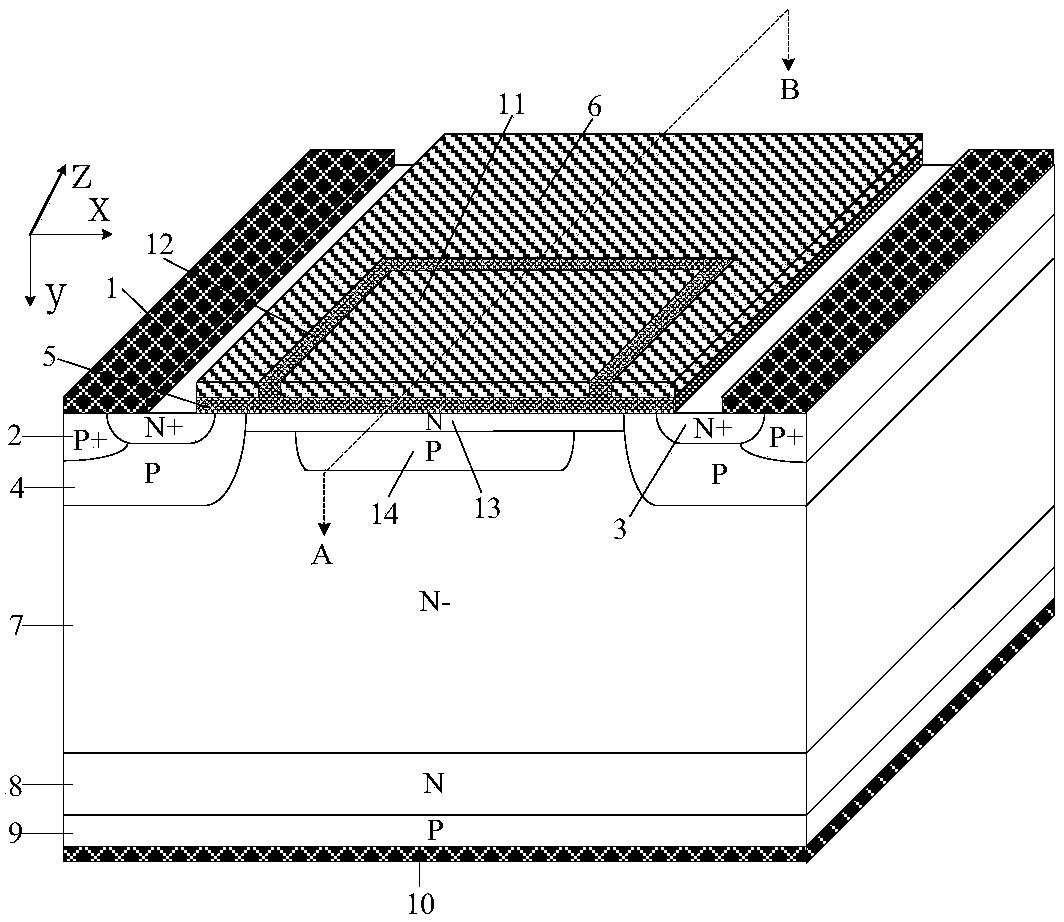

[0047] A planar gate IGBT, its semi-cellular structure and the section along the AB line are as follows image 3 and Figure 4 As shown, on the basis of Example 1, there is also an N-type layer 13 between the dielectric layer 5 and the N-drift region 7, and the doping concentration of the N-type layer 13 is equal to that of the N-drift region 7 10-100 times the doping concentration, the junction depth is 0.1-0.2 microns; and there is also a p-type buried layer 14 in the N-drift region 7 between the p-type base regions 4 in the lateral direction of the device, the The p-type buried layer 14 is 2-10 microns away from the p-type base region 4, and the p-type buried layer 14 is discontinuous and uniformly distributed in the N-drift region 7 in the longitudinal direction of the device, with a width of 1-5 microns and a spacing of 1-5 microns, the p-type buried layer 14 is in contact with the n-type layer 13 through the upper surface, and the junction depth of the p-type buried lay...

Embodiment 3

[0049] A planar gate IGBT, its semi-cellular structure and the section along the AB line are as follows Figure 5 and Figure 6As shown, on the basis of Example 2, there is also a layer of N in the N-drift region 7 between the p-type buried layer 14 and between both sides of the p-type buried layer 14 and the p-type base region 4 Type buried layer 15, the N-type buried layer 15 is in contact with the N-type layer 13 through the upper surface and its junction depth is 0.2-0.5 micron, the doping concentration of the N-type buried layer 15 is N-drift region 7 doped 10-100 times the impurity concentration. The introduction of the N-type buried layer 15 further improves the forward conduction characteristics of the device. When the device breaks down, the N-type buried layer 15 is fully depleted.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More