Virtual-channel low-power circuit applied to network-on-chip

An on-chip network and virtual channel technology, which is applied in the field of low-power design circuits for virtual channels, and can solve problems such as large cache requirements and uneven cache allocation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

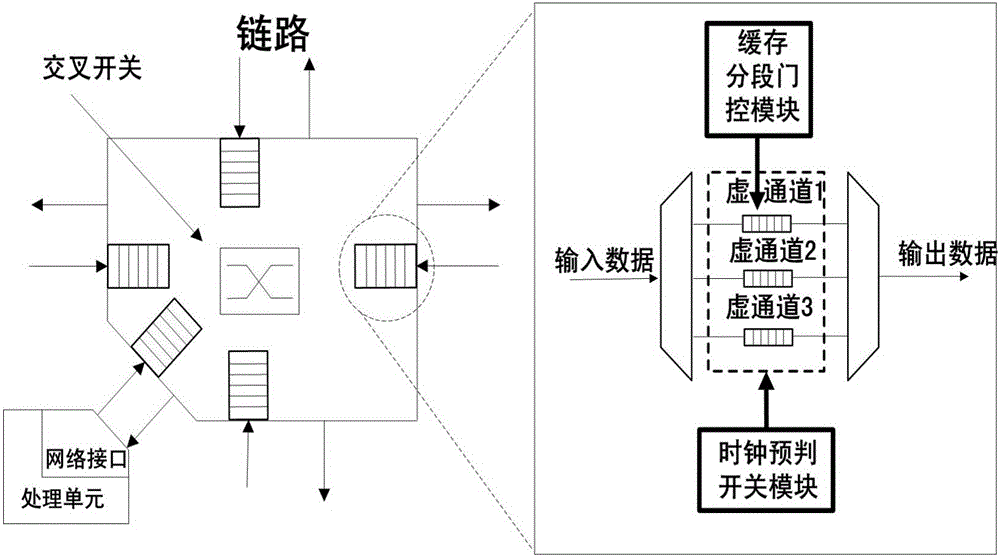

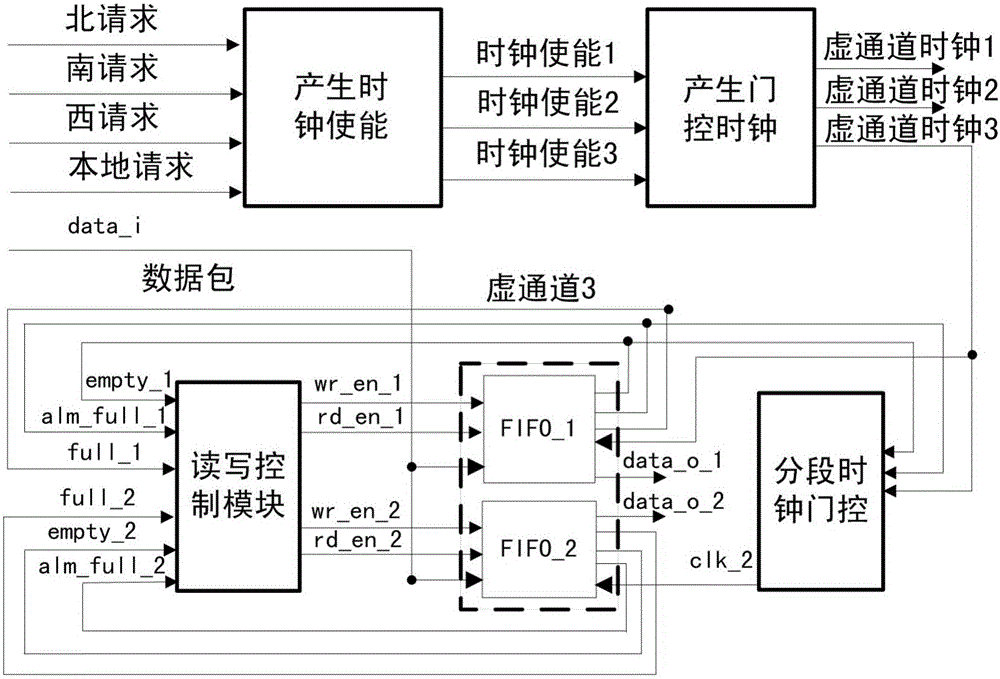

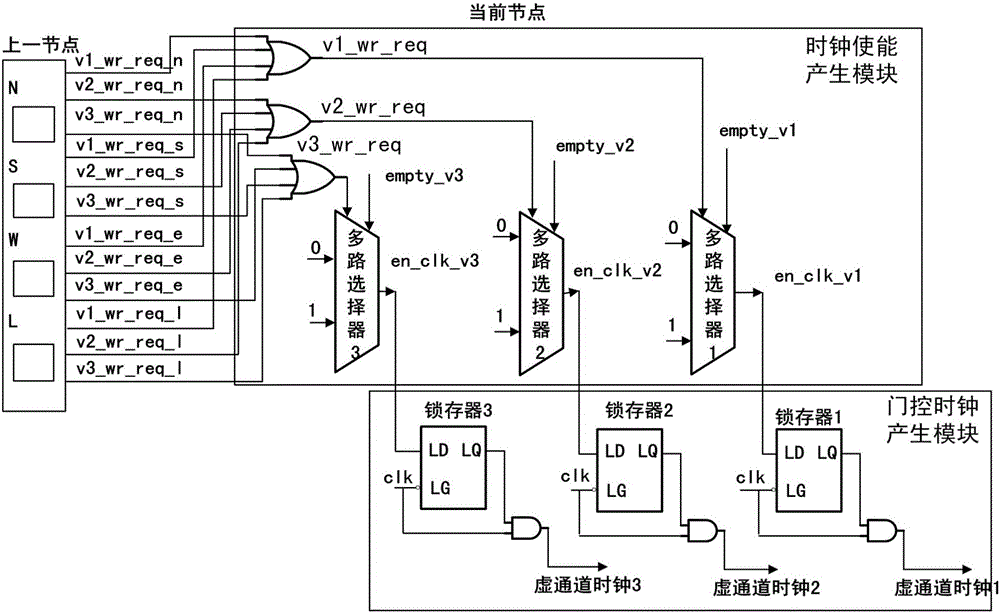

[0062] In this embodiment, the network-on-chip is a hierarchical 6×6 two-dimensional network, which is mainly used in hybrid multicast routing, and is divided into upper-layer routers and lower-layer routers, and is composed of 40 routing nodes; the network-on-chip uses 3 ×3 sub-network is divided into four multicast areas; the intermediate router in each area is connected to the upper router through an extra port; each routing node has several channels, and each routing node includes input state machine, translation coder, arbiter and crossbar; the input state machine has three virtual channels and is controlled by the virtual channel management circuit, such as figure 1 As shown, these three virtual channels are unicast virtual channels, named virtual channel 1, which mainly transmit unicast data packets; Data packets in the direction of north transmission; multicast data non-north transmission virtual channel, named virtual channel 3, mainly transmits data packets whose dat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More