Three-dimensional power VDMOS device and integration method thereof

A three-dimensional power and integration method technology, applied in the fields of semiconductor devices, electric solid-state devices, semiconductor/solid-state device manufacturing, etc., can solve the problems affecting the integration of power systems, signal delay time, and the power consumption ratio of interconnect lines, and achieve shortening The effect of signal delay time, shortening the length of global interconnection lines, and reducing the proportion of power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

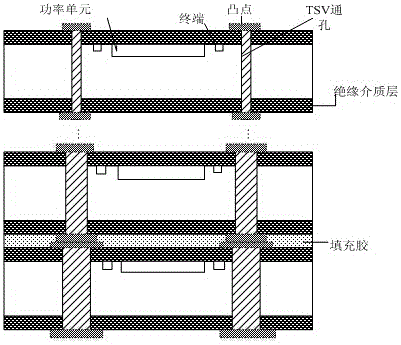

[0034] A three-dimensional power VDMOS device, which includes a power unit and a chip layer, the chip layer has more than two, each chip layer is evenly distributed with more than two power units, and each power unit is provided with an independent terminal on the periphery, The periphery of each power unit is provided with TSV through holes for interlayer conductive interconnection, and each chip layer is stacked together to form a three-dimensional power VDMOS device.

[0035] TSV through holes for heat dissipation are arranged on the periphery of the power unit. Embed heat-dissipating TSV vias around the periphery of each power unit, the number of which is related to the power loss of each power unit, the aspect ratio of the TSV vias, and the thickness of the insulating layer in the TSV vias;

[0036] Since the drain current of the VDMOS power unit of each chip layer passes through the TSV through hole of the interlayer conductive interconnection and finally gathers on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More