Real-time dynamic testing circuit for anti-fuse FPGA microprobe

A dynamic testing, real-time dynamic technology, applied in the field of integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

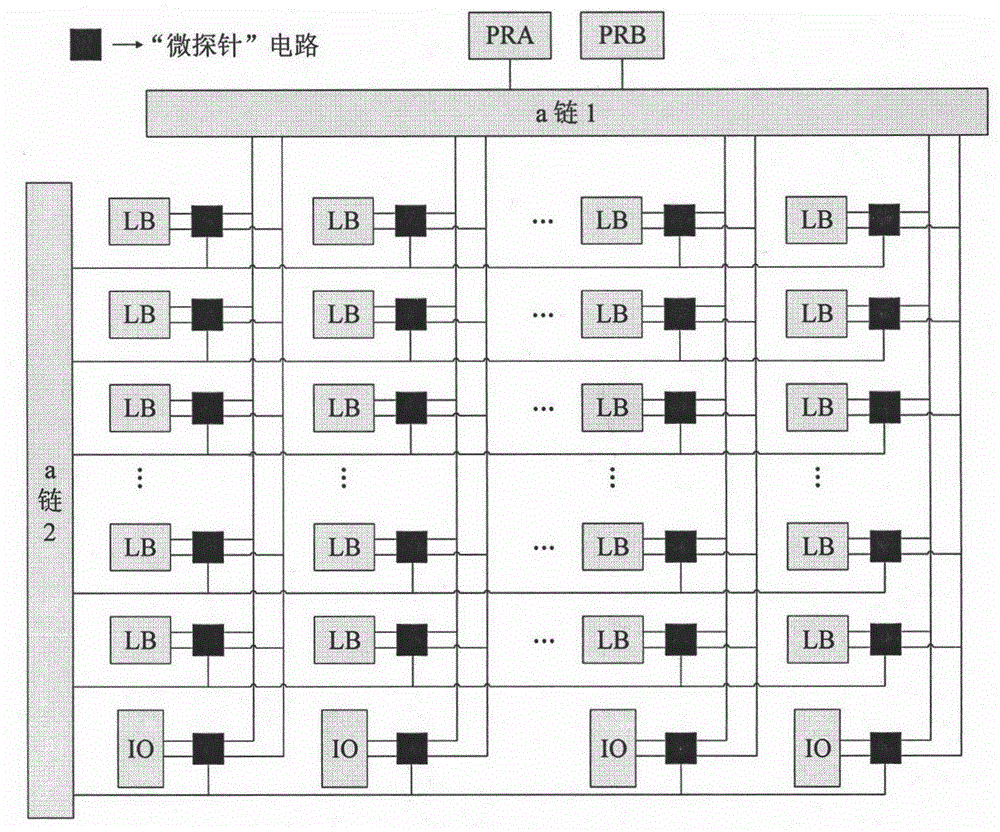

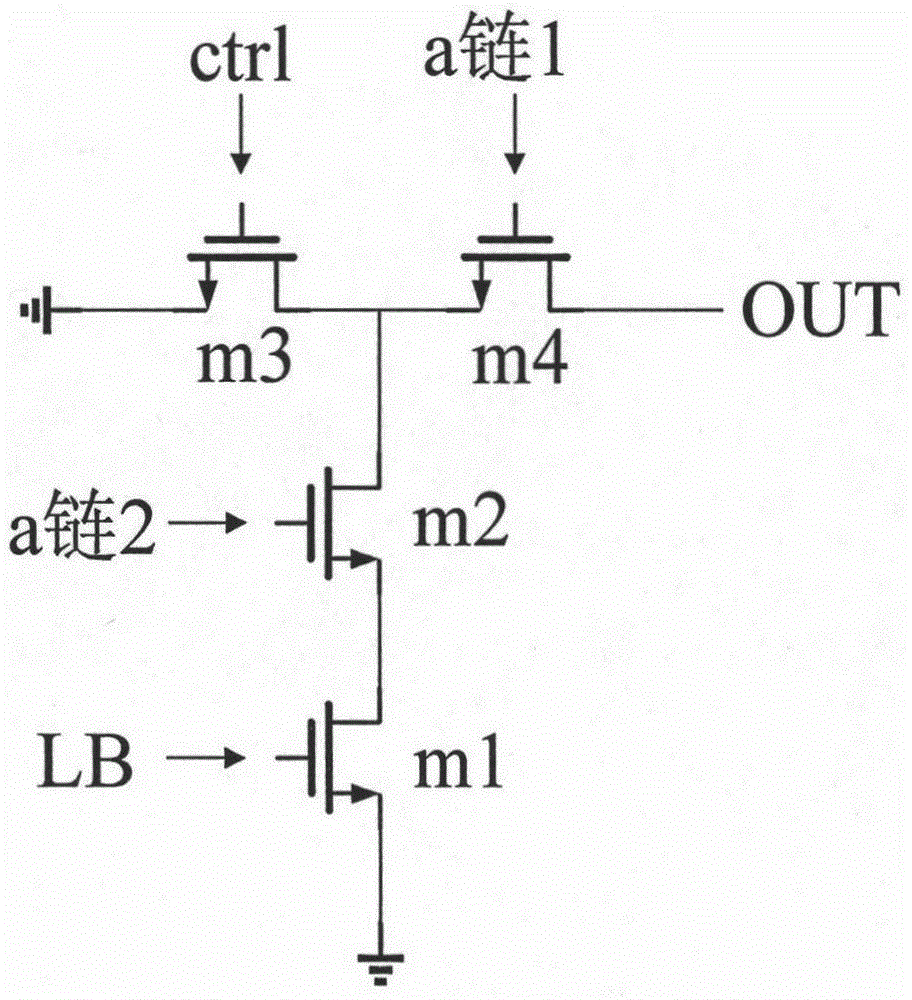

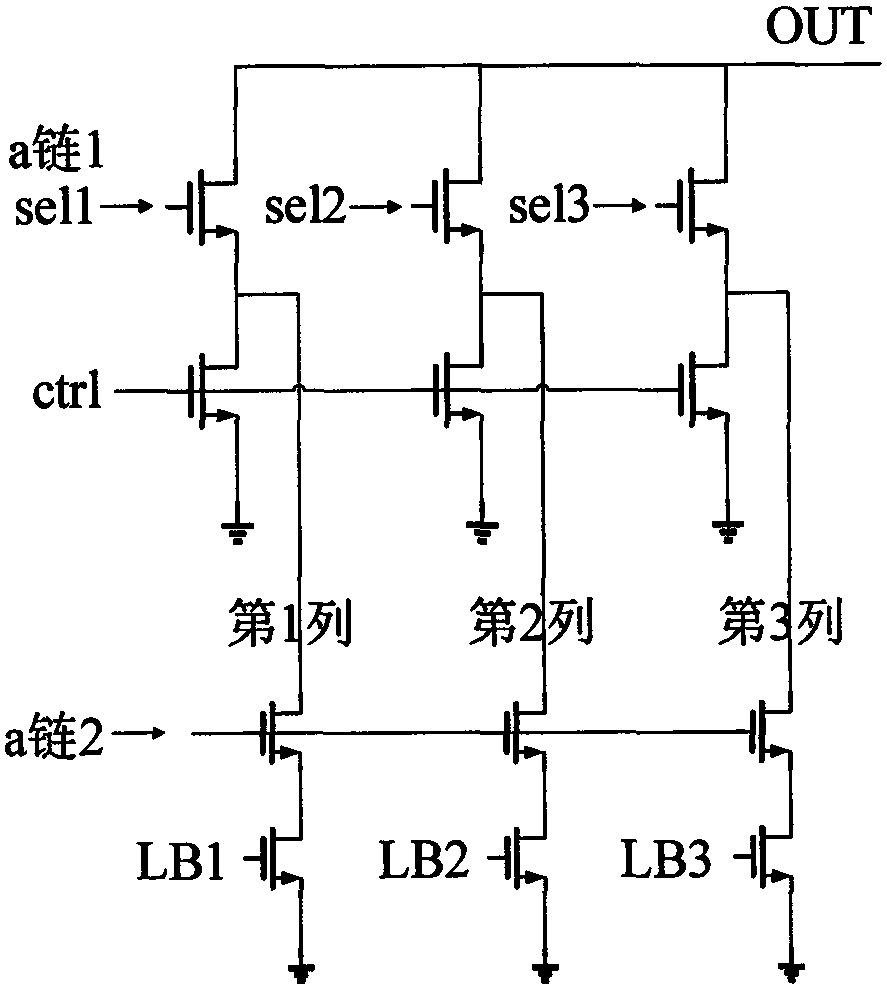

[0014] figure 1 It is a block diagram of the dynamic test circuit system array of the present invention. In the logic array of the antifuse FPGA, the output terminal of each logic module LB has a detection circuit structure for detecting the output signal of the logic module, which is represented by a black square pattern in the figure. Since th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More