Forming method of ring gate field effect transistor

A technology of field effect transistors and ring gates, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems that the electrical performance of ring gate field effect tubes needs to be improved, so as to avoid graphic transmission deviation, improve shape accuracy, and improve The effect of electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] It can be known from the background art that there is an urgent need to provide a new method for forming a GALL field effect transistor to solve the problem of poor electrical performance of the GALL field effect transistor in the prior art.

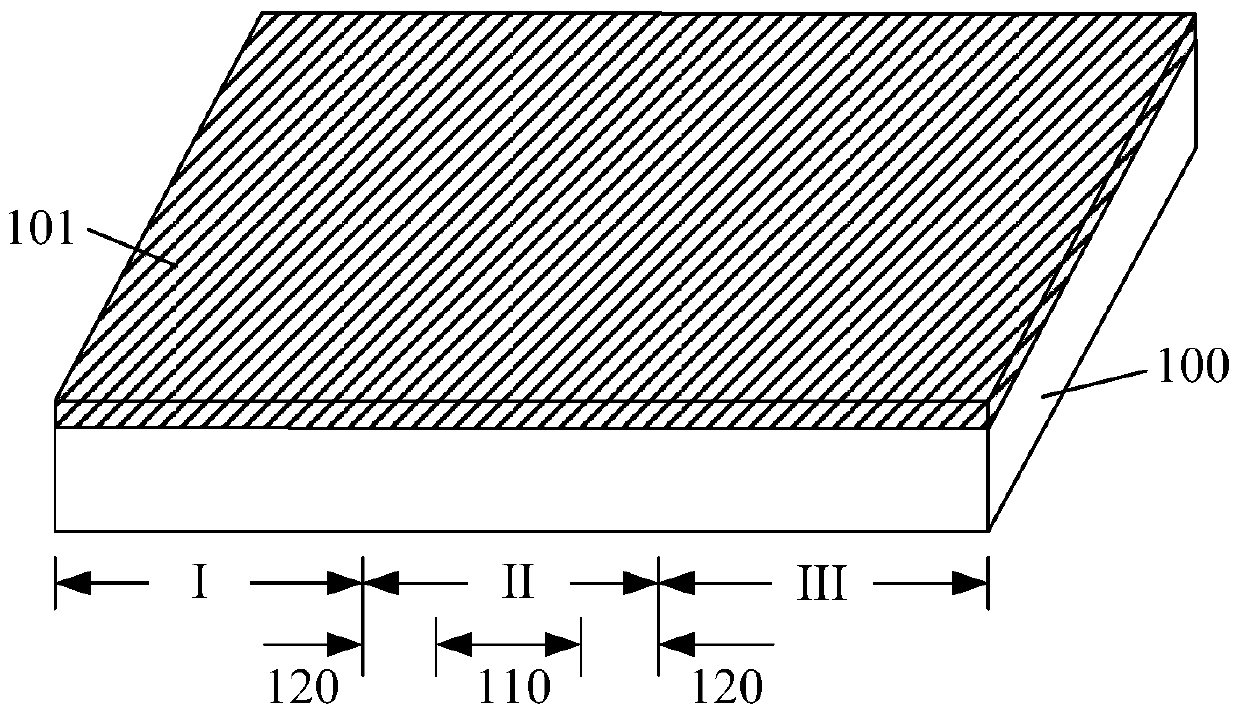

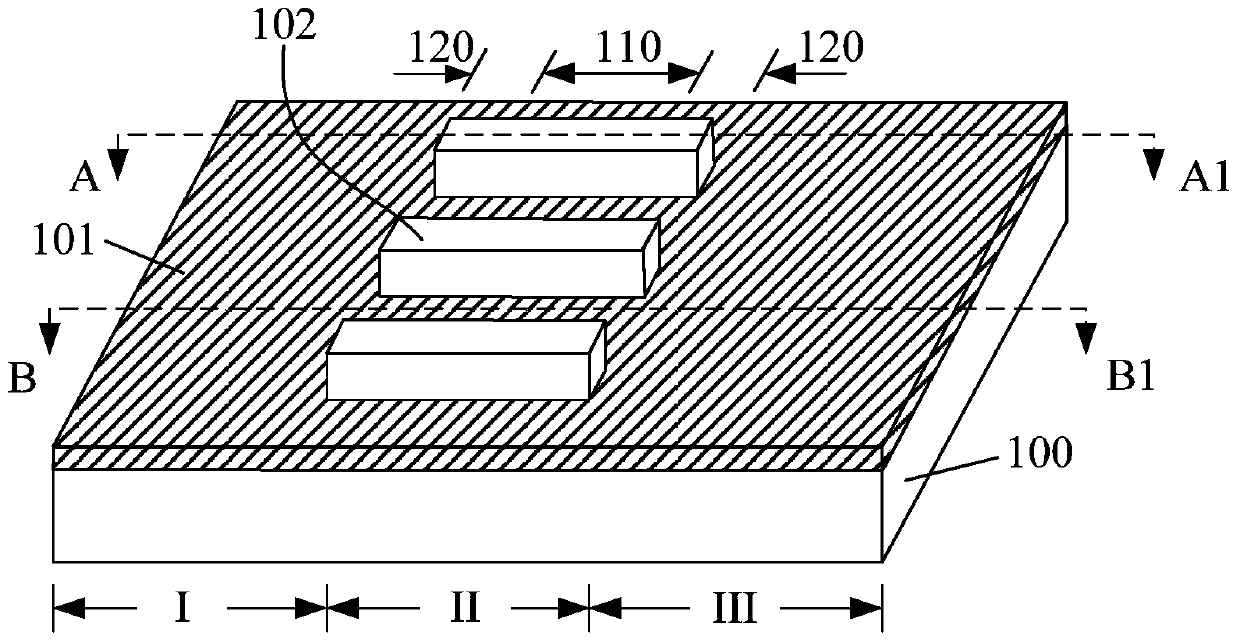

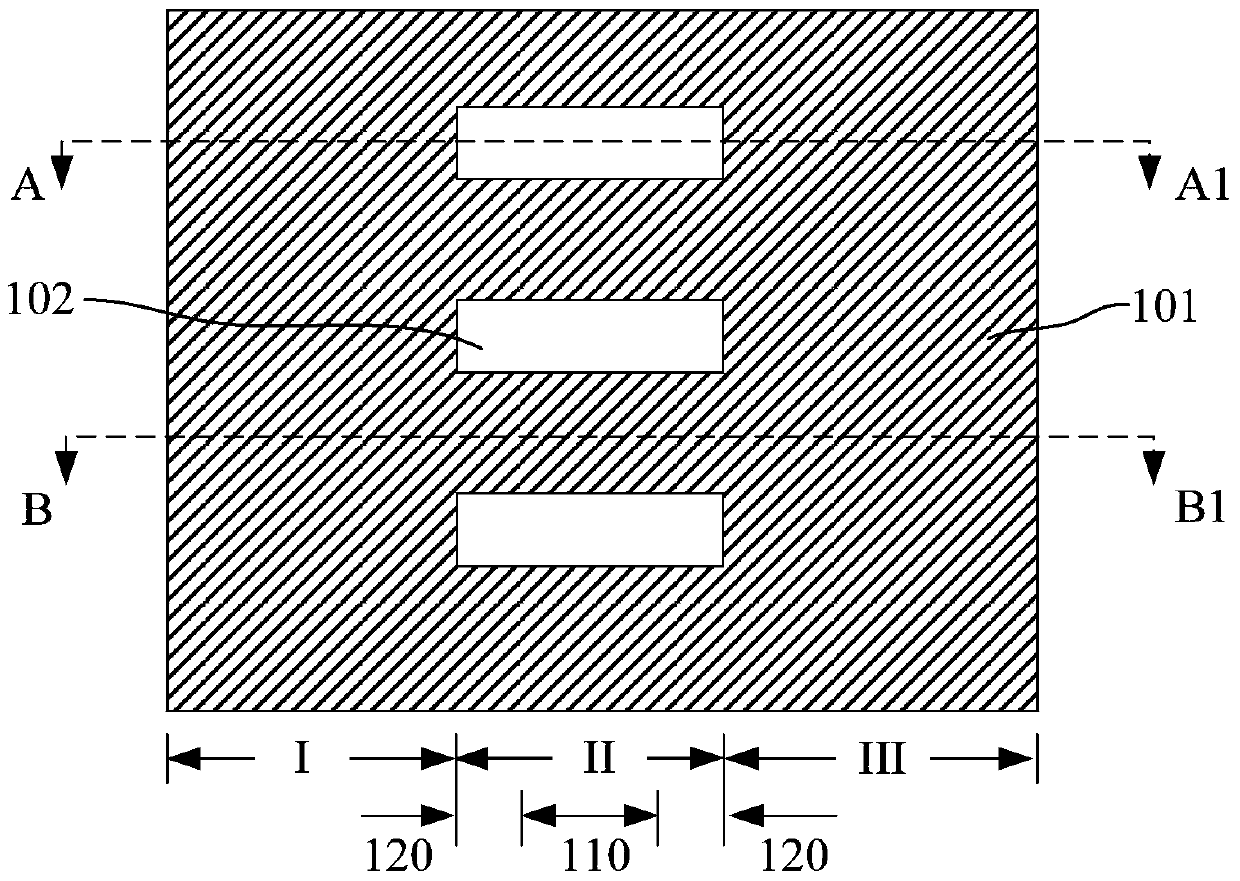

[0035] It has been found through research that the formation of the channel region in the gate-all-around field effect transistor usually undergoes an etching process, and the pattern in the mask layer is transferred to the channel region. During the pattern transfer process, it is limited by the etching process. The pattern transfer is prone to deviation, resulting in poor morphology of the formed channel region, which in turn leads to poor electrical performance of the gate-all-around field effect transistor. Moreover, since the formation of the channel region has undergone an etching process, the etching process may easily cause the performance of the channel region to deteriorate, thereby further causing the electrical performa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More