LED vertical chip structure and manufacturing method thereof

A technology of chip structure and manufacturing method, applied in semiconductor devices, electrical components, circuits, etc., can solve problems affecting chip reliability, leakage, splashing of metal layers, etc., so as to reduce the risk of leakage, avoid metal splashing, and improve reliability. sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

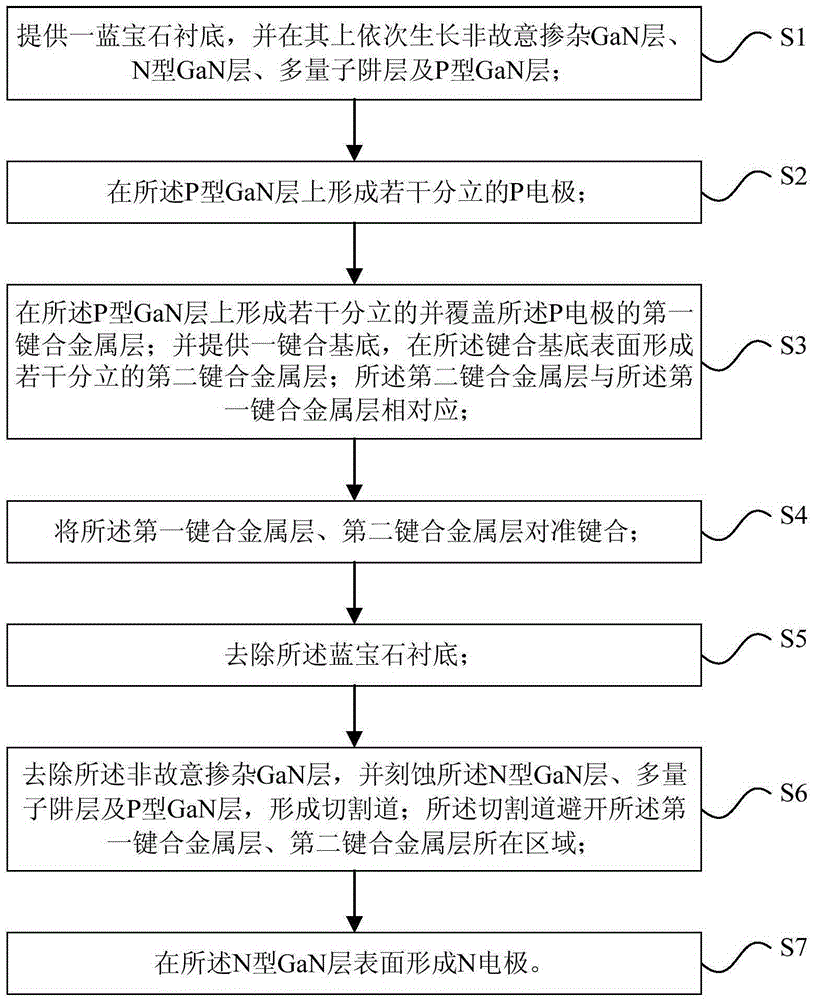

[0063] The present invention provides a method for manufacturing an LED vertical chip structure, please refer to figure 2 , shown as a process flow diagram of the method, comprising the following steps:

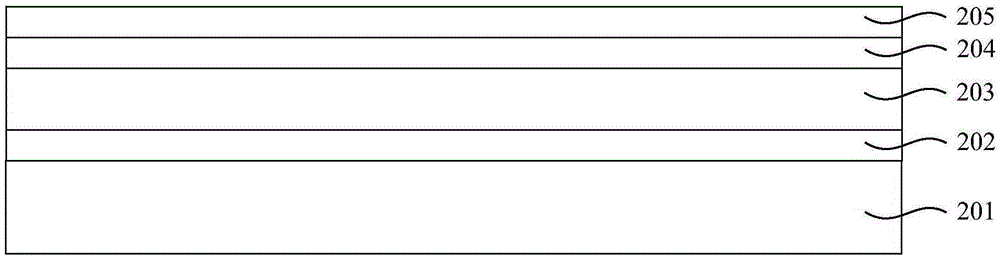

[0064] S1: Provide a sapphire substrate, and sequentially grow an unintentionally doped GaN layer, an N-type GaN layer, a multi-quantum well layer and a P-type GaN layer on it;

[0065] S2: forming several discrete P electrodes on the P-type GaN layer;

[0066] S3: forming several discrete first bonding metal layers on the P-type GaN layer and covering the P electrode; and providing a bonding substrate, forming several discrete second bonding layers on the surface of the bonding substrate a metal layer; the second bonding metal layer corresponds to the first bonding metal layer;

[0067] S4: Align and bond the first bonding metal layer and the second bonding metal layer;

[0068] S5: removing the sapphire substrate;

[0069] S6: removing the unintentionally doped GaN lay...

Embodiment 2

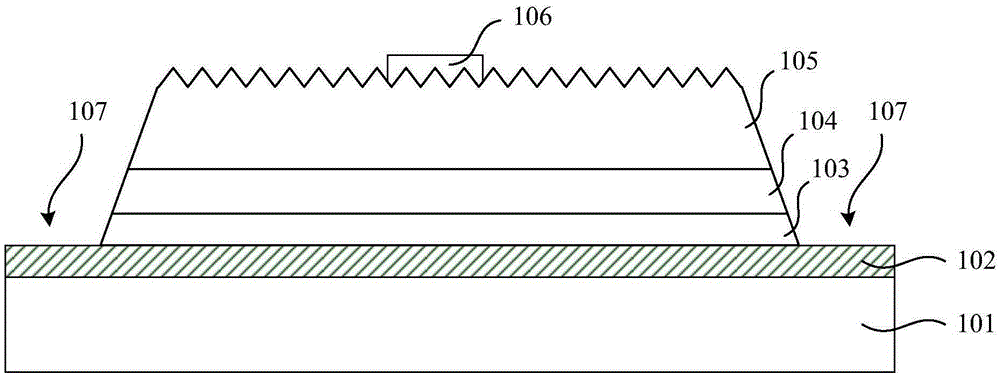

[0094] The present invention also provides a LED vertical chip structure, such as Figure 12 As shown, the chip structure includes:

[0095] Bonding substrate 208;

[0096] a bonding metal layer formed on the surface of the bonding substrate 208;

[0097] a P electrode 206 embedded in the surface of the bonding metal layer;

[0098] A P-type GaN layer 205, a multi-quantum well layer 204, an N-type GaN layer 203, and an N-electrode 211 are sequentially formed on the surface of the P-electrode 206;

[0099] in:

[0100] The projected area of the bonding metal layer and the P electrode 206 on the horizontal plane is smaller than the projected area of the P-type GaN layer 205 on the horizontal plane.

[0101] As an example, the bonding metal layer is composed of a first bonding metal layer 207 and a second bonding metal layer 209 , and the first bonding metal layer 207 and the second bonding metal layer 209 are bonded to form a whole.

[0102] In the LED vertical chip str...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More