Method of forming a fin field effect transistor

A fin field effect and transistor technology, which is applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem that the performance of transistors needs to be improved, and achieve the effect of improving punch-through, accurate position, and increasing hot carriers. The effect of the injection effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

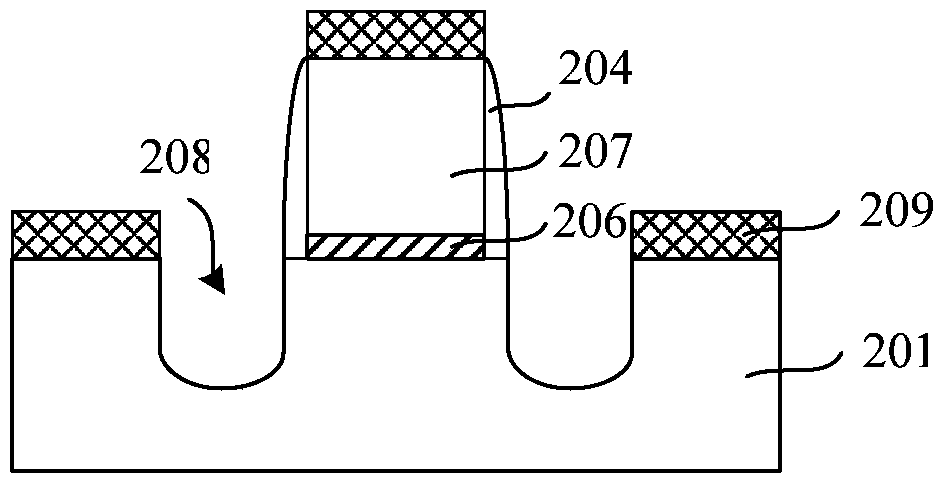

[0042] The performance of the fin field effect transistor formed by the prior art still needs to be improved, for example, the fin field effect transistor formed by the prior art will still be affected by the hot carrier injection effect.

[0043] The study found that the prior art uses ion implantation to form shallowly doped source and drain regions. Due to the three-dimensional structure of the fin, it is affected by the shadow effect, and some positions in the fin may not be implanted with impurity ions or the implanted impurity ions may be affected. Rarely, the concentration distribution of the impurity ions forming the shallowly doped source and drain regions in the fin will be uneven. In addition, the same problem also exists when forming the anti-puncture doping region. The concentration of impurity ions in the anti-puncture doping region is not uniform, so that the anti-puncture performance of the FinFET is also affected.

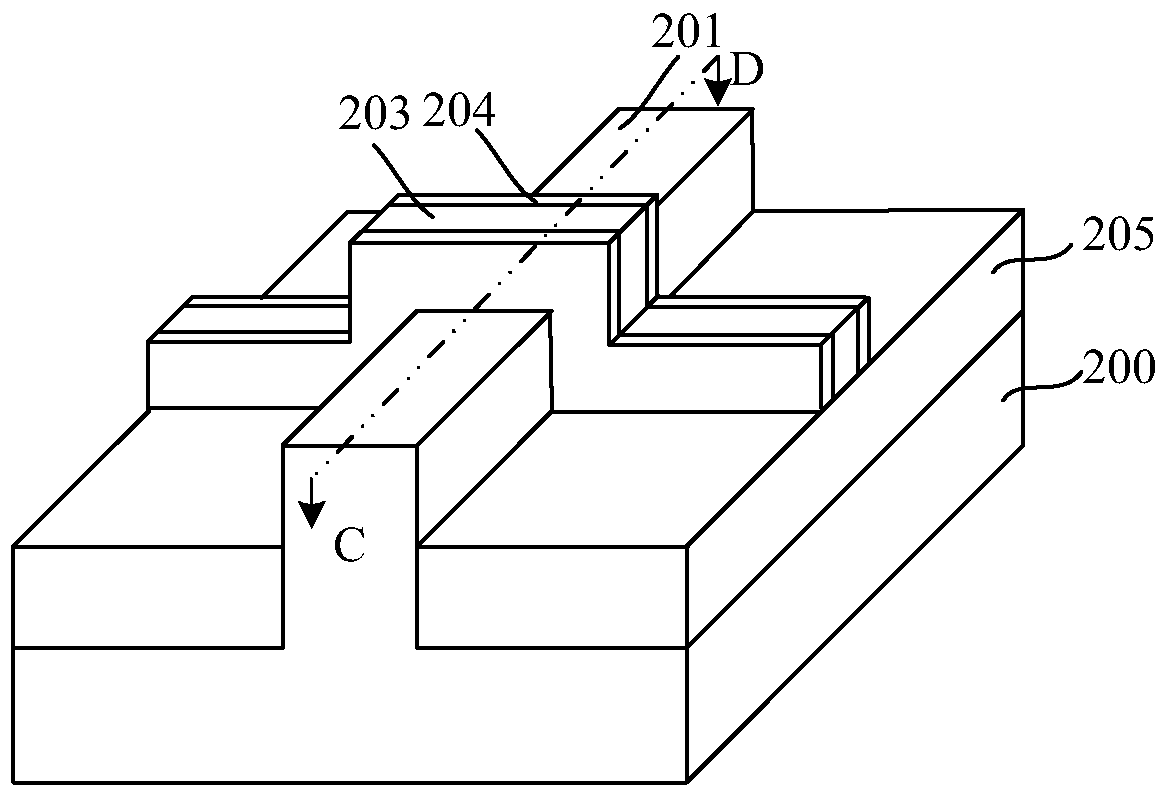

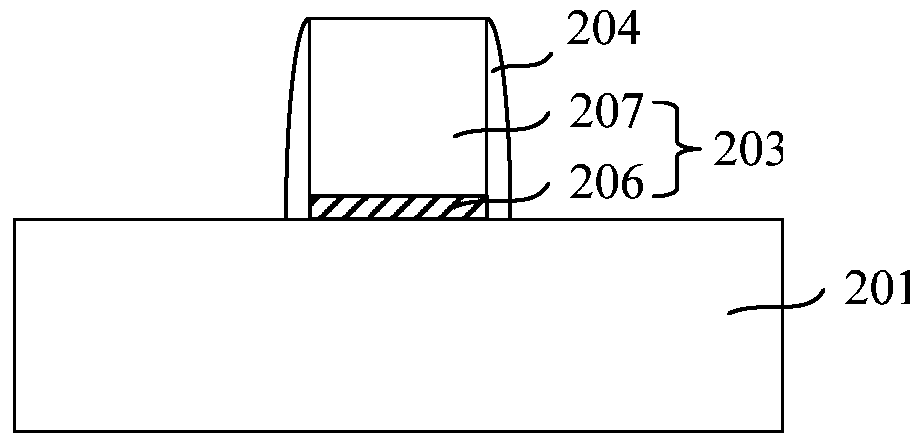

[0044] An embodiment of the present inventio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More