Low-power-consumption, adjustable-frequency and adjustable-duty-ratio clock generation circuit

A clock generation circuit and frequency modulation technology, which is applied in the direction of electric pulse generation, pulse generation, multiple input and output pulse circuits, etc., can solve the problems of unfavorable overall system miniaturization, large overall power consumption, and difficulty in modifying traditional crystal oscillator circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

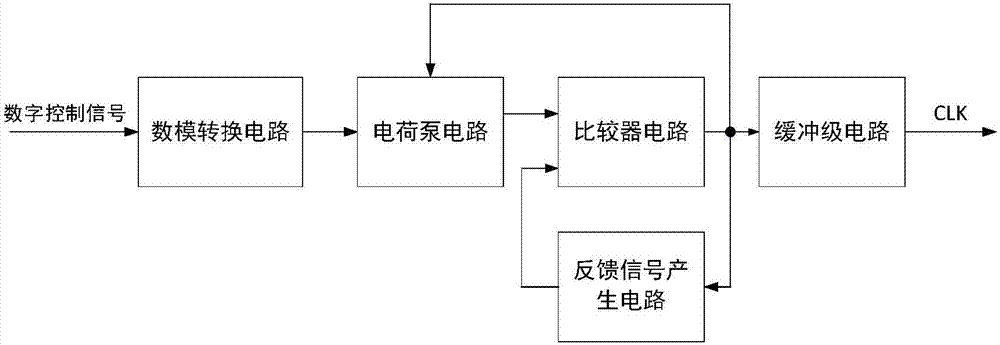

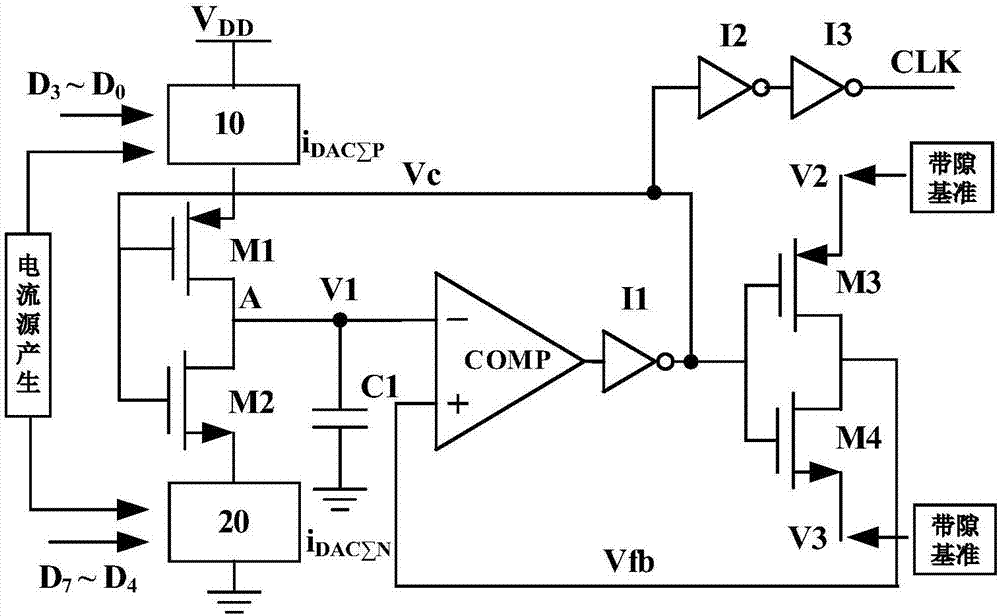

[0033] Please refer to figure 1 , figure 2 , figure 1 A structural block diagram of a clock generation circuit with low power consumption, adjustable frequency, and adjustable duty cycle provided by an embodiment of the present invention; figure 2 A schematic structural diagram of a low power consumption adjustable frequency and adjustable duty cycle clock generation circuit provided by an embodiment of the present invention; the low power consumption adjustable frequency and adjustable duty cycle clock generation circuit includes: digital-analog A conversion circuit, a charge pump circuit, a comparator circuit, a feedback signal generation circuit and a buffer stage circuit, the digital-to-analog conversion circuit receives a digital control signal and is electrically connected to the charge pump circuit, and the charge pump circuit is electrically connected to the comparator circuit, the comparator circuit is electrically connected to the feedback signal generating circu...

Embodiment 2

[0050] In this embodiment, on the basis of the above-mentioned embodiments, the working principle and connection relationship thereof will be further described with emphasis.

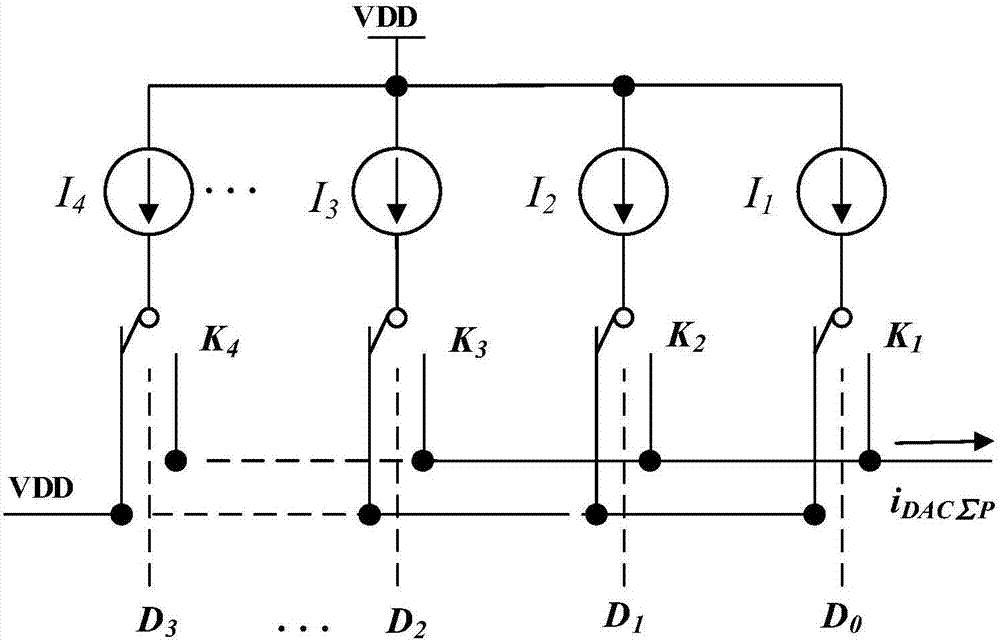

[0051] see again figure 1 , the digital-to-analog converter 10 adopts a binary-weighted current-source-steering DAC (current-steering DAC). It receives an external digital control signal (binary code), which is used to adjust the current i of the P-type current steering DAC DACΣP and the current i of the N-type current steering DAC DACΣN The size of the charge pump can be adjusted to adjust the charge and discharge current of the charge pump, and the duty cycle adjustment function of the clock generation circuit can be realized. This digital control signal is the duty ratio setting value. The current steering DAC in the digital-to-analog converter has fast switching speed and strong driving capability, and can obtain high output current precision.

[0052] The current source generating circuit recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More