Message analysis method and device based on FPGA hardware parallel pipelines

A message parsing and pipeline technology, applied in the field of network communication, can solve the problems of dynamic adjustment of inability to transmit messages, waste of resources and power, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the purpose, technical solution and advantages of the present invention more clear and understandable, the present invention will be further described in detail below in conjunction with the accompanying drawings and technical solutions. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

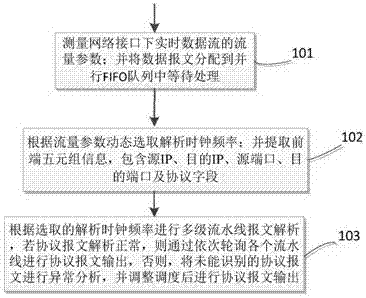

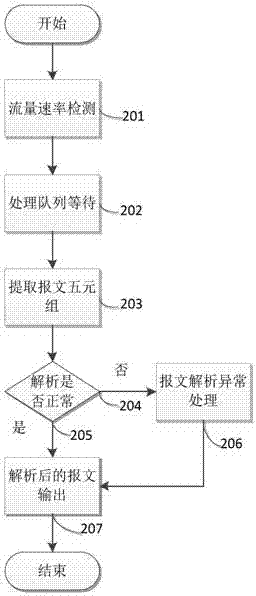

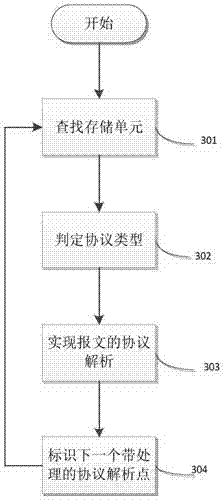

[0035] Examples, see figure 1 and 2 As shown, a message parsing method based on the FPGA hardware parallel pipeline, the FPGA hardware parallel pipeline includes a multi-stage FPGA programmable hardware pipeline, and each stage of the FPGA programmable hardware pipeline includes a storage unit and a logic processing unit, and the storage unit is used to store the A standardized protocol analysis tree node with protocol analysis capability, the logical processing unit is used to control the search of the data message sequence and complete the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More