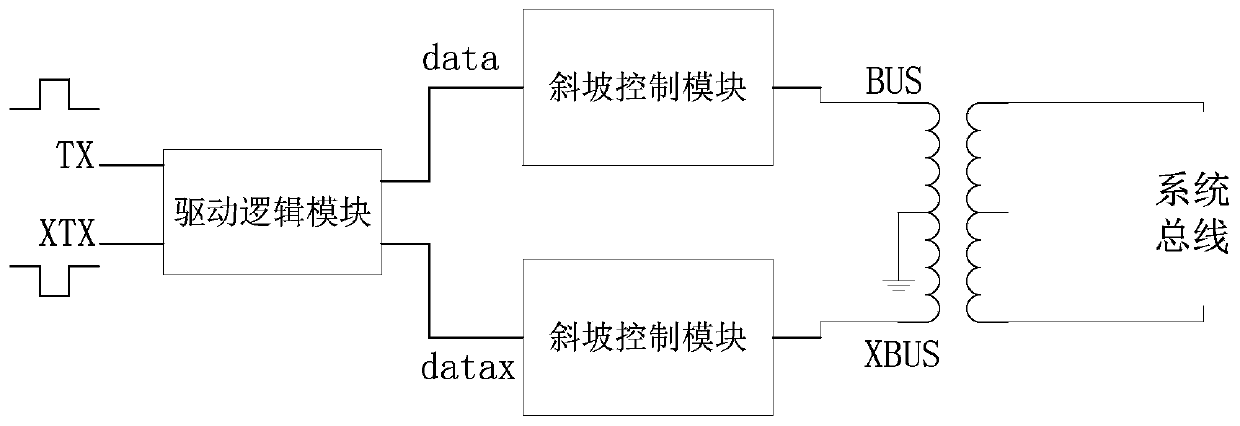

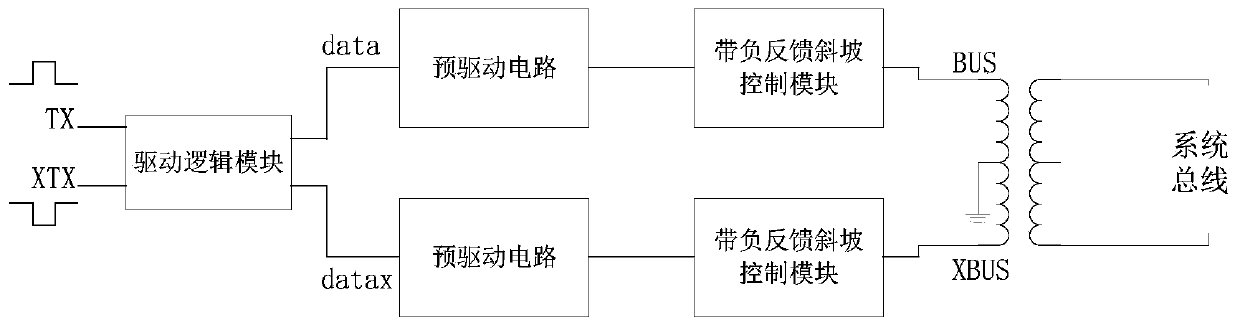

A low-voltage high-speed inductive load drive circuit

A technology for driving circuits and inductive loads, applied in electrical digital data processing, instruments, etc., can solve the problems of reduced output amplitude of the driving circuit, out-of-tolerance parameters of high-frequency data zero-crossing interval, large difference in gate-source voltage, etc. The effect of reducing signal transmission delay, preventing oscillation, and meeting communication requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

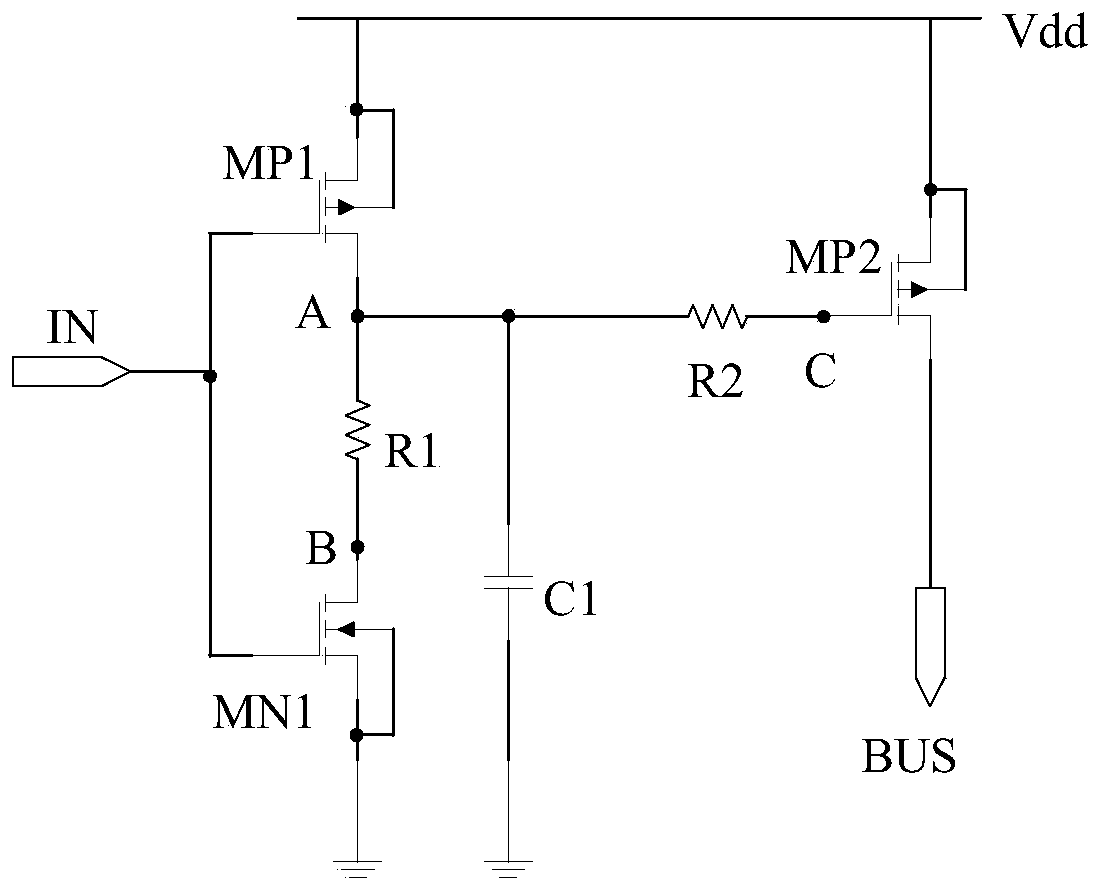

Method used

Image

Examples

Embodiment 1

[0044] Based on 0.5um BCD digital-analog mixed-signal process technology, input low level is less than or equal to 0.33V, input high level is greater than or equal to 2.97V, 3.15V≤VDD≤3.45V, can realize normal communication of 32 nodes, at 3.3V power supply voltage Next, the differential amplitude of the near-end node is greater than or equal to 20V, the differential amplitude of the middle-end node is equal to 5V, and the differential amplitude of the remote node is greater than or equal to 0.86V.

[0045] According to the inventive scheme, under the condition that the electrical connection characteristics of the drive circuit are correct, the communication network can be constructed according to the relevant standards of the 4M 1553 bus. When the 4M 1553 signal drives the bus, when low-frequency data and high-frequency data are transmitted, the gate voltage of the high-voltage PMOS transistor MP4 Both are close to 0V, which ensures that the high-amplitude output of the drive ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More