Manufacturing method of flash memory

A manufacturing method and memory technology, which are applied to semiconductor devices, electric solid-state devices, electrical components, etc., can solve the problem of poor step coverage of sidewall materials, decreased ability of the second sidewall 17 to isolate the floating gate FG and source lines, and rapid weakening. Flash and other problems, to achieve the effect of enhancing the density and improving the data retention ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

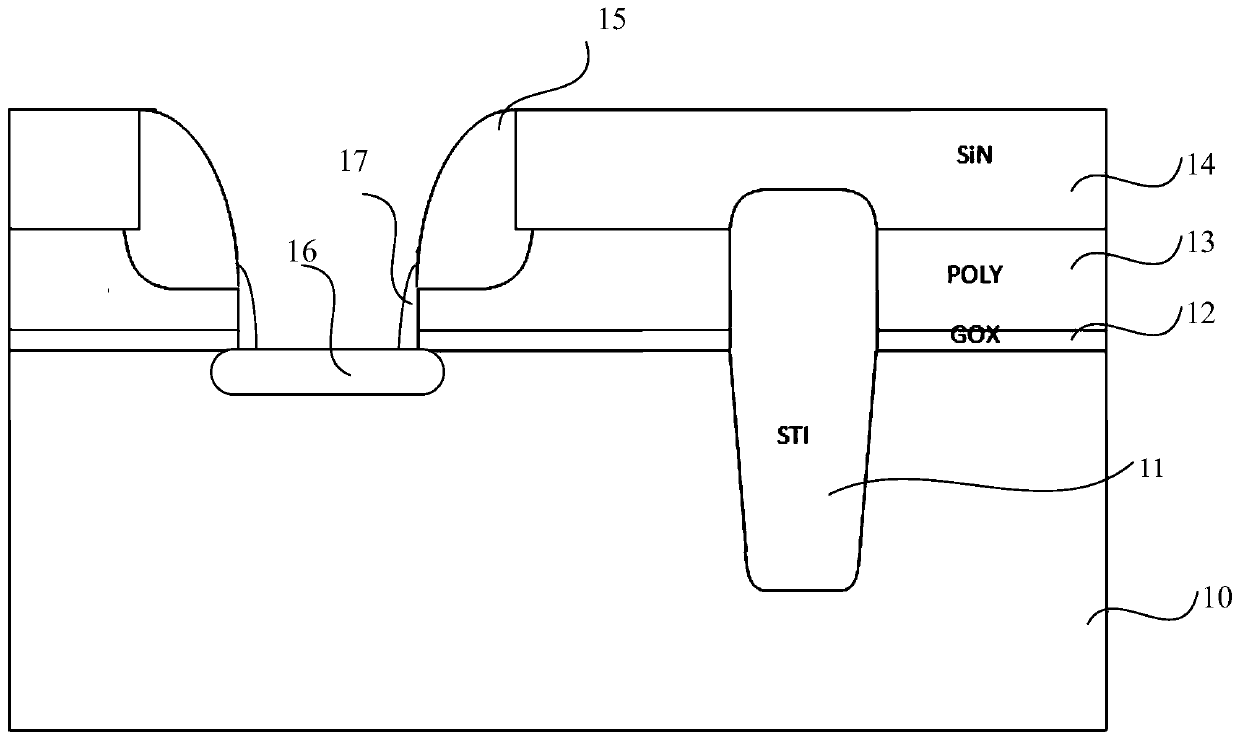

[0044] In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

[0045] Please refer to figure 2 , the present invention proposes a kind of manufacturing method of flash memory, comprising:

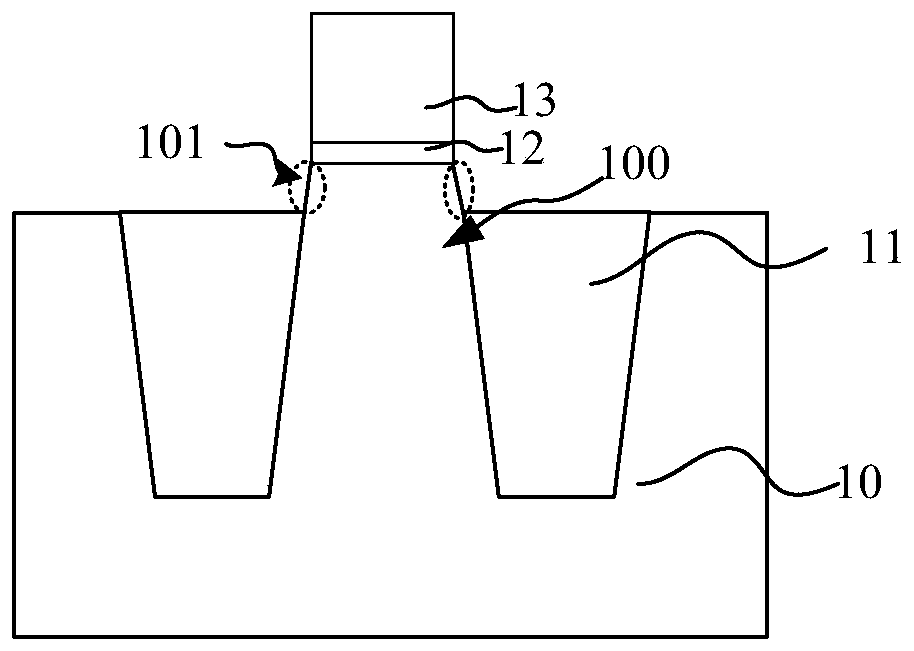

[0046] S1, providing a semiconductor substrate, sequentially forming a floating gate oxide layer, a floating gate layer, and an interlayer dielectric layer on the surface of the semiconductor substrate;

[0047] S2, etching the interlayer dielectric layer, and stopping to the surface of the floating gate layer, to form an opening;

[0048] S3, forming a first side wall on the side wall of the opening;

[0049] S4. Using the first sidewall as a mask, continue to etch the floating gate layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com