Md5 brute force cracking system and method based on fpga

A kind of MD5 and brute force technology, applied in the field of FPGA-based MD5 brute force cracking system, can solve the problems of limiting FPGA clock frequency, limiting clock frequency, low efficiency, etc., and achieve the effects of strong cracking timeliness performance, high cracking rate, and improved throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] This embodiment is based on FPGA MD5 brute-force cracking design and implementation, using FPGA hardware technology, single-step operation operation multi-level pipeline design idea, multi-core MD5 brute force cracking operation unit parallel processing mechanism; for brute force cracking, it is to increase the cracking rate per unit time, improve There are two main schemes for the cracking rate, one is to increase the operating speed of the MD5 brute force cracking operation unit, and the other is to process the multi-core MD5 brute force cracking operation unit in parallel; based on these two design ideas, the limit of the MD5 algorithm operation on the FPGA operating clock frequency is minimized , that is, the clock frequency of the FPGA to realize MD5 brute-force cracking algorithm operation is improved, and the design idea of multi-core parallel processing mechanism is adopted, so that the rate of MD5 brute-force cracking is doubled, and the efficiency of MD5 brute...

Embodiment 2

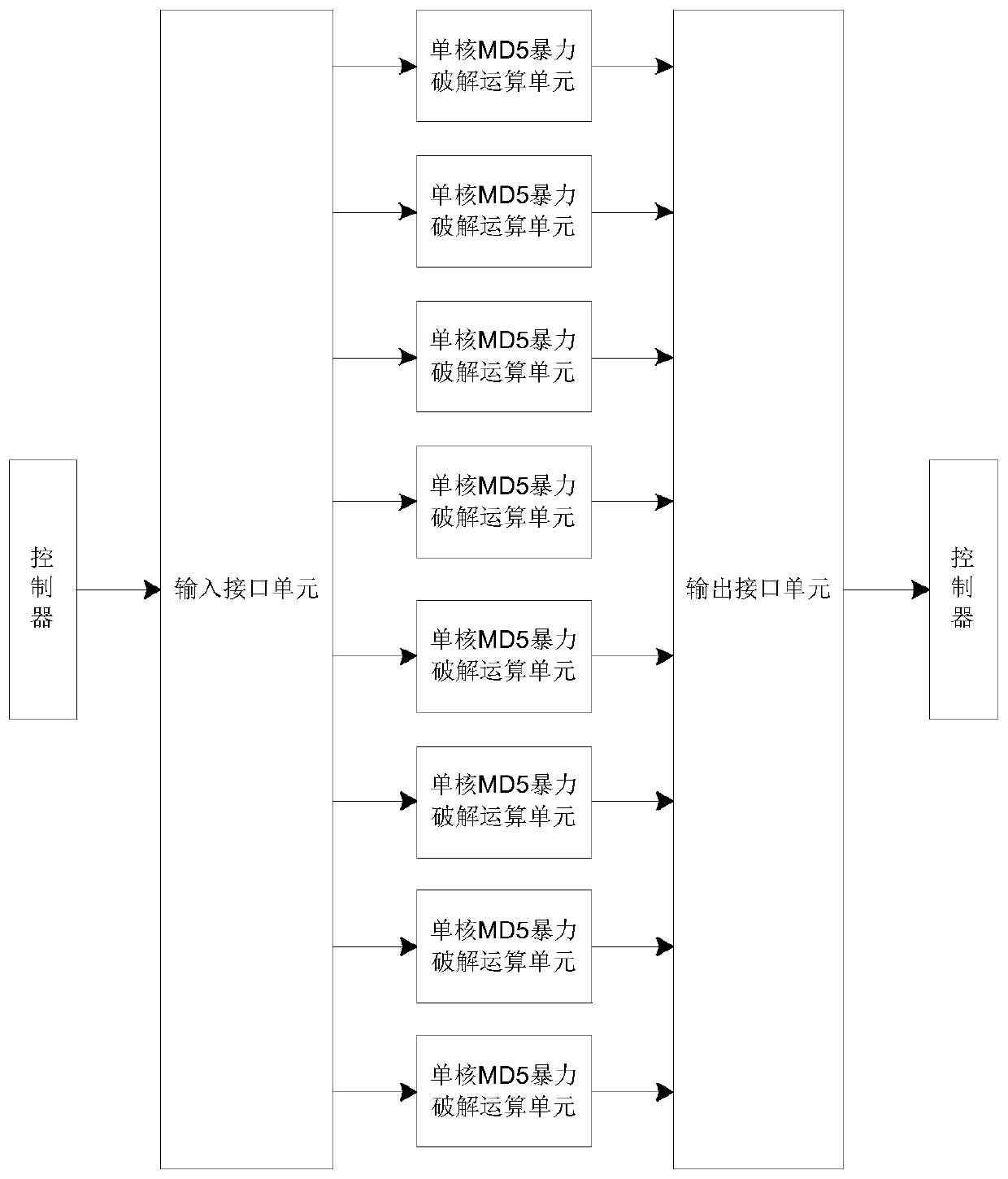

[0043] This embodiment discloses an FPGA-based MD5 brute force cracking system, including: an input interface unit, an 8-core MD5 brute force cracking operation unit, and an output interface unit.

[0044] The 8-core MD5 brute-force cracking operation unit is composed of 8 single-core MD5 brute-force cracking calculation units connected in parallel. Among them, the single-core MD5 brute-force cracking calculation unit is the core to realize the MD5 brute-force cracking system operation, and the most important thing is to design and realize the MD5 algorithm operation.

[0045] In this embodiment, the FPGA-based MD5 brute force cracking adopts the pipeline design idea, and the single-core MD5 brute force cracking operation unit is connected to all pipeline designs in parallel, and the single-step MD5 calculation operation adopts a multi-stage pipeline design to improve the running clock frequency of the FPGA to realize the MD5 algorithm operation. The clock frequency of the inve...

Embodiment 3

[0053] This embodiment is based on the FPGA-based MD5 brute-force cracking system disclosed in the foregoing embodiments, and proposes a FPGA-based MD5 brute-force cracking method. The MD5 brute-force cracking method includes the following steps:

[0054] The input interface unit is connected with the external controller device to realize the communication between the FPGA and the controller, and analyze and distribute the message sent by the controller to the N-core MD5 brute force cracking operation unit;

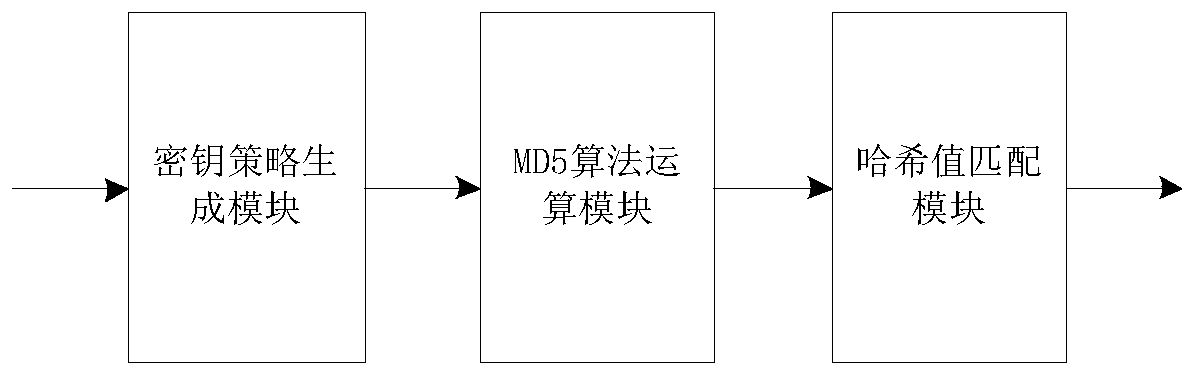

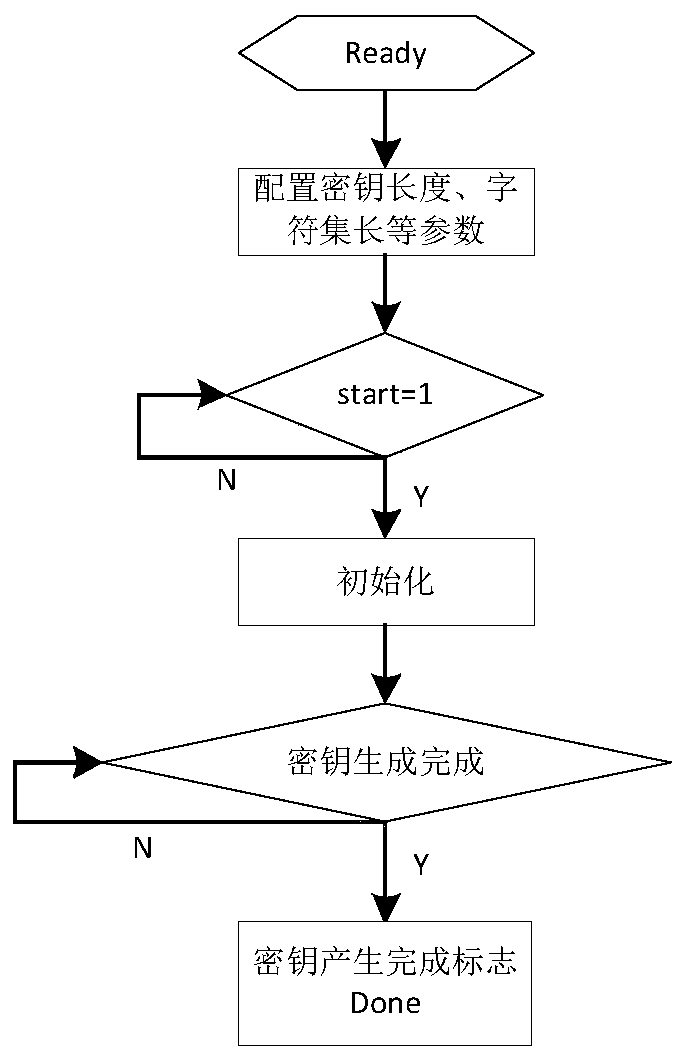

[0055] The N-core MD5 brute-force cracking operation unit is composed of N single-core MD5 brute-force cracking calculation units connected in parallel. Among them, the key policy generation module in the single-core MD5 brute-force cracking calculation unit implements the key policy of limited length according to the strategy issued by the controller. combination generation;

[0056] The MD5 algorithm operation module in the single-core MD5 brute force cracking operation...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More