Novel resistive random access memory and manufacturing method therefor

A resistive memory and resistive switching technology, applied in electrical components and other directions, can solve the problems of improving the performance regulation of resistive memory, affecting the stability of resistive memory cells, and complicating the resistance switching mechanism, and achieving excellent resistance transition characteristics. , the effect of abundant reserves and stable resistance transformation characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

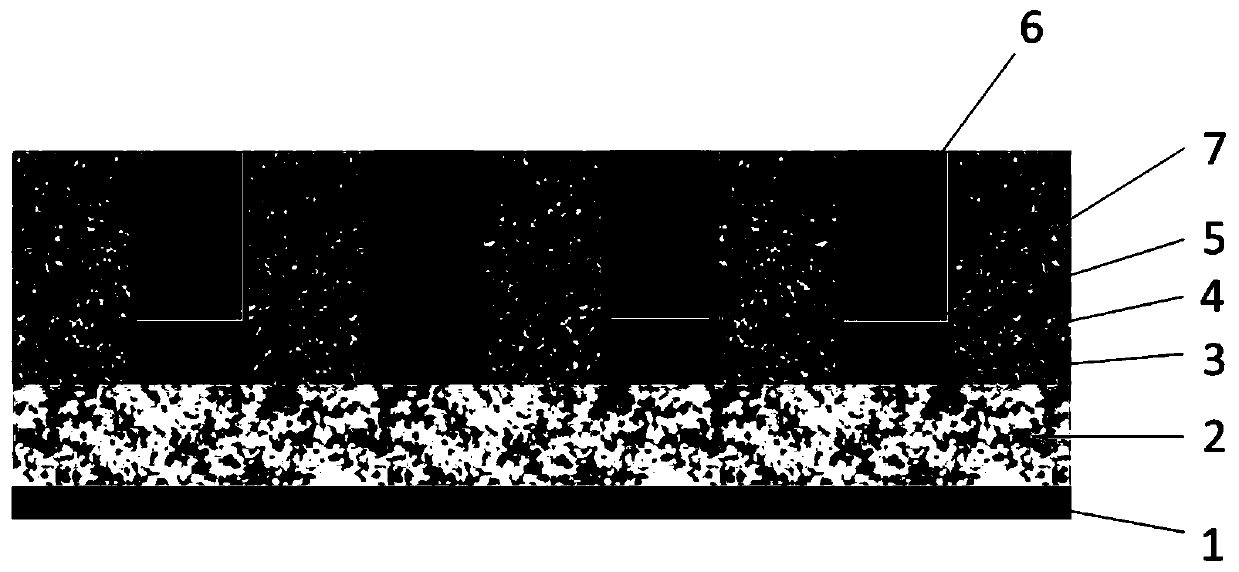

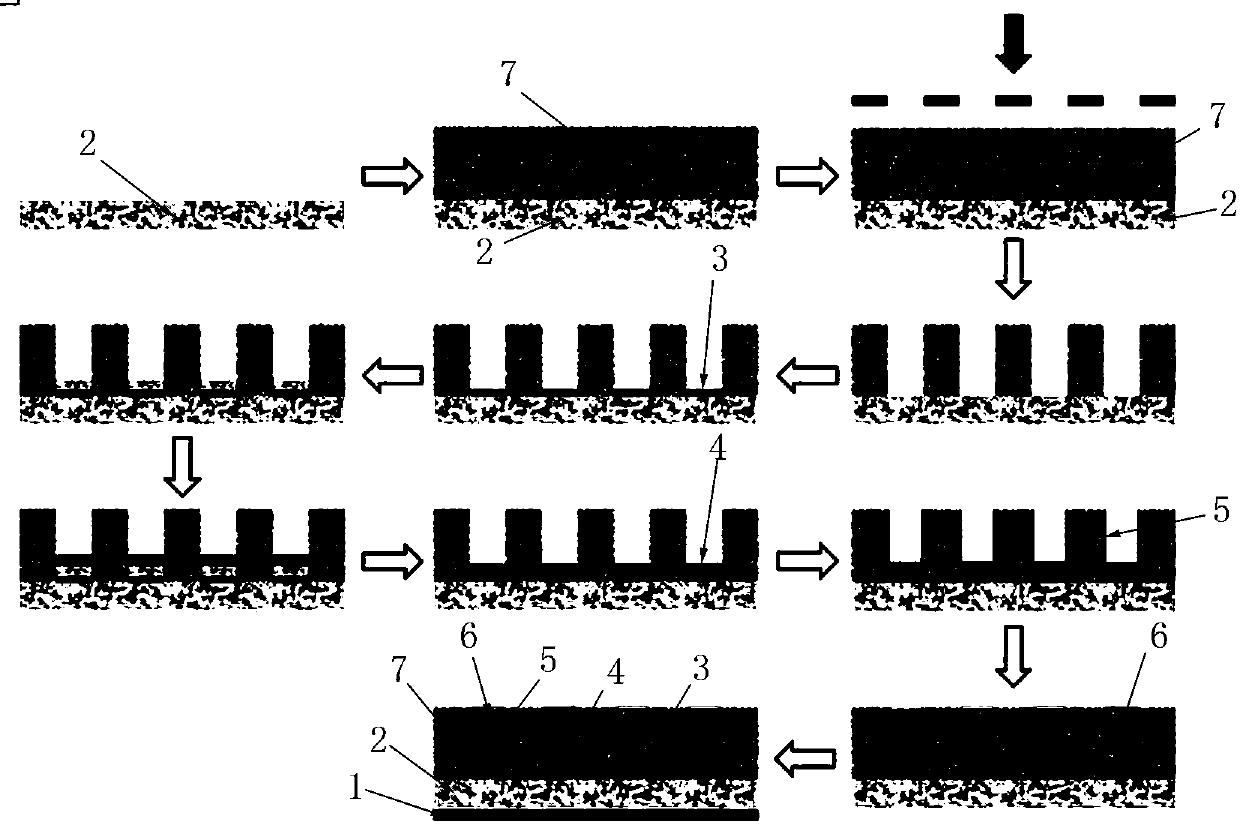

[0027] See attached picture. The resistive variable memory described in this embodiment includes a silicon wafer substrate 2 and a back electrode 1, a silicon dioxide protective layer 7 is provided above the silicon wafer substrate 2, and several cylindrical recesses are etched on the silicon dioxide protective layer 7, The contact between the recess and the silicon wafer substrate is a resistive dielectric layer 3, and above the resistive dielectric layer 3 is a silicide layer 4, and above the silicide layer 4 and the inner wall of the corresponding recess is an anti-metal diffusion layer 5. Inside the metal diffusion layer 5 is a metal top electrode 6; the resistive dielectric layer 3 is a silicon-based thin film, and the anti-metal diffusion layer 5 is a tantalum / tantalum nitride mixed layer.

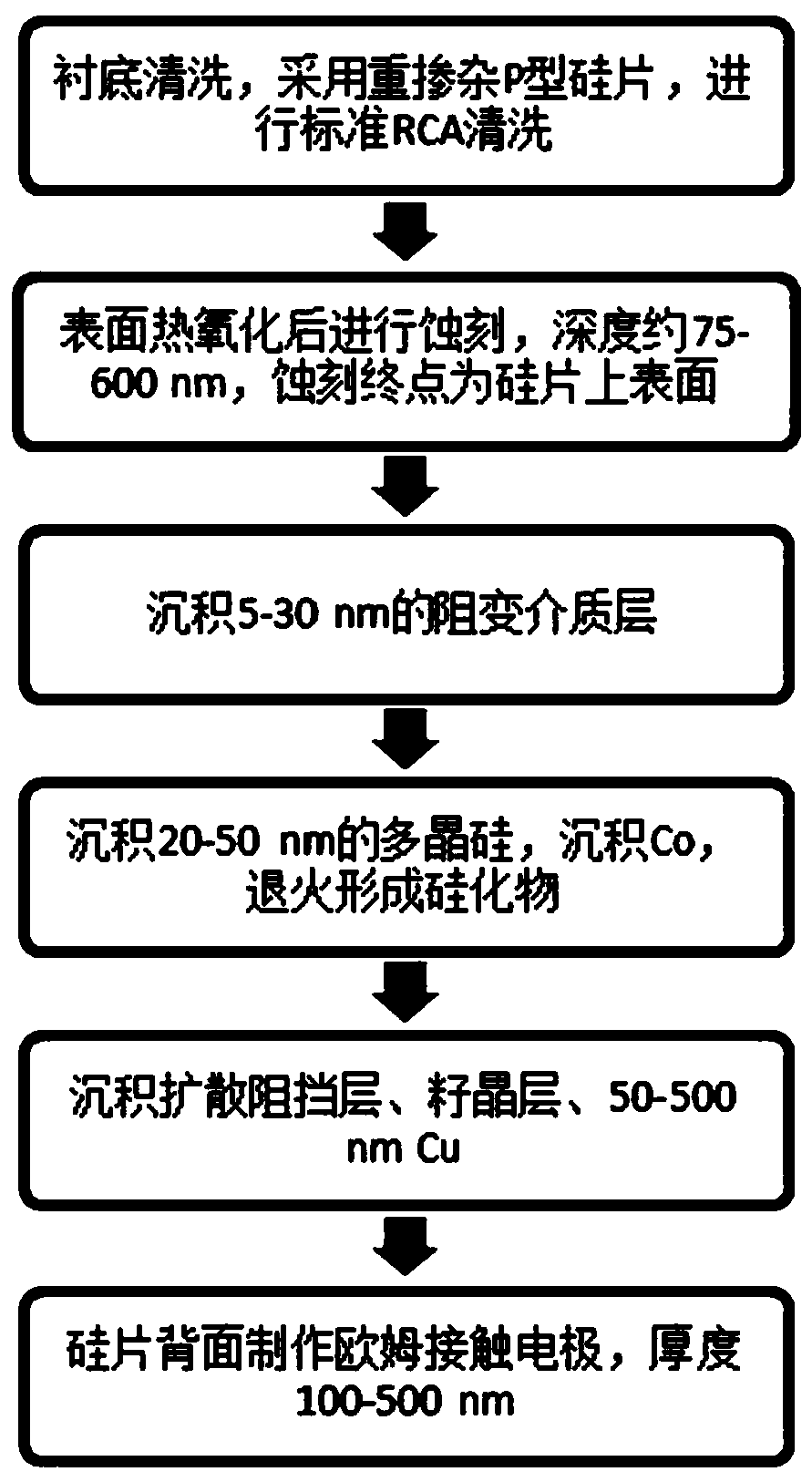

[0028] The preparation process of the resistive variable memory described in this embodiment:

[0029] 1) First, use the RCA standard cleaning method in the integrated circuit (IC) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More