Groove power semiconductor element and manufacture method thereof

A technology of power semiconductors and manufacturing methods, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of reducing the gate/drain capacitance value of trench power semiconductor components, affecting component characteristics, and failing to gate There are problems such as PN junction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

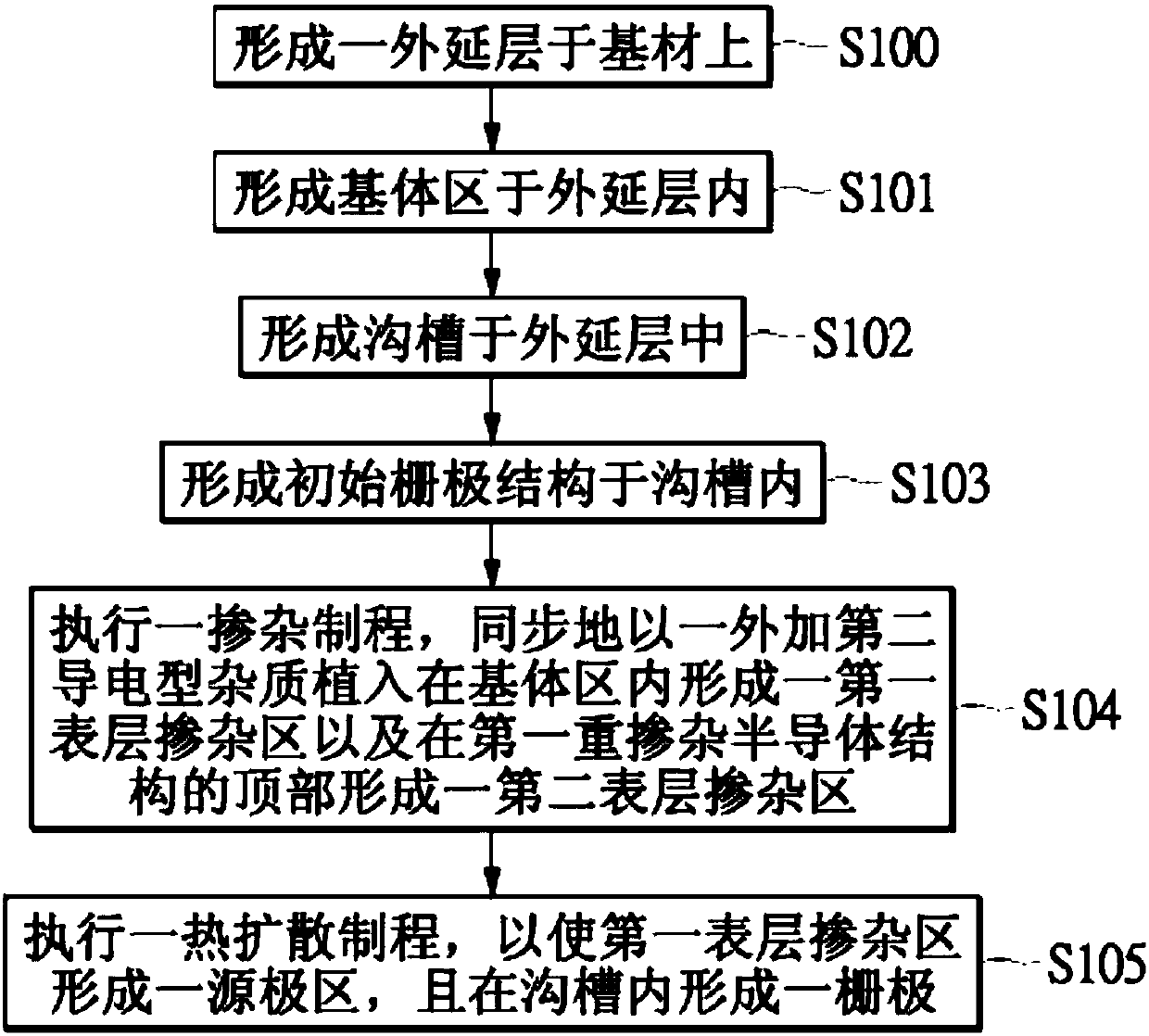

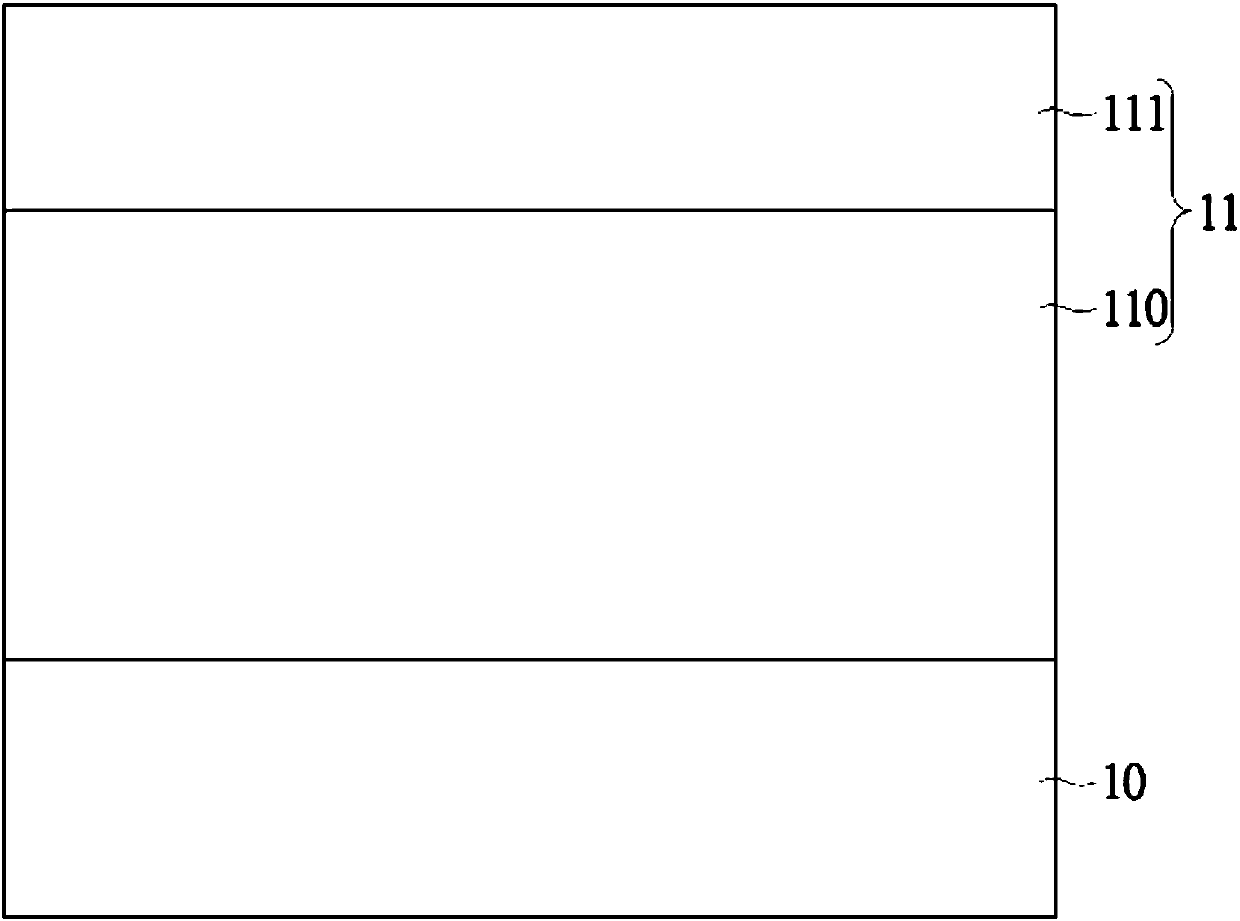

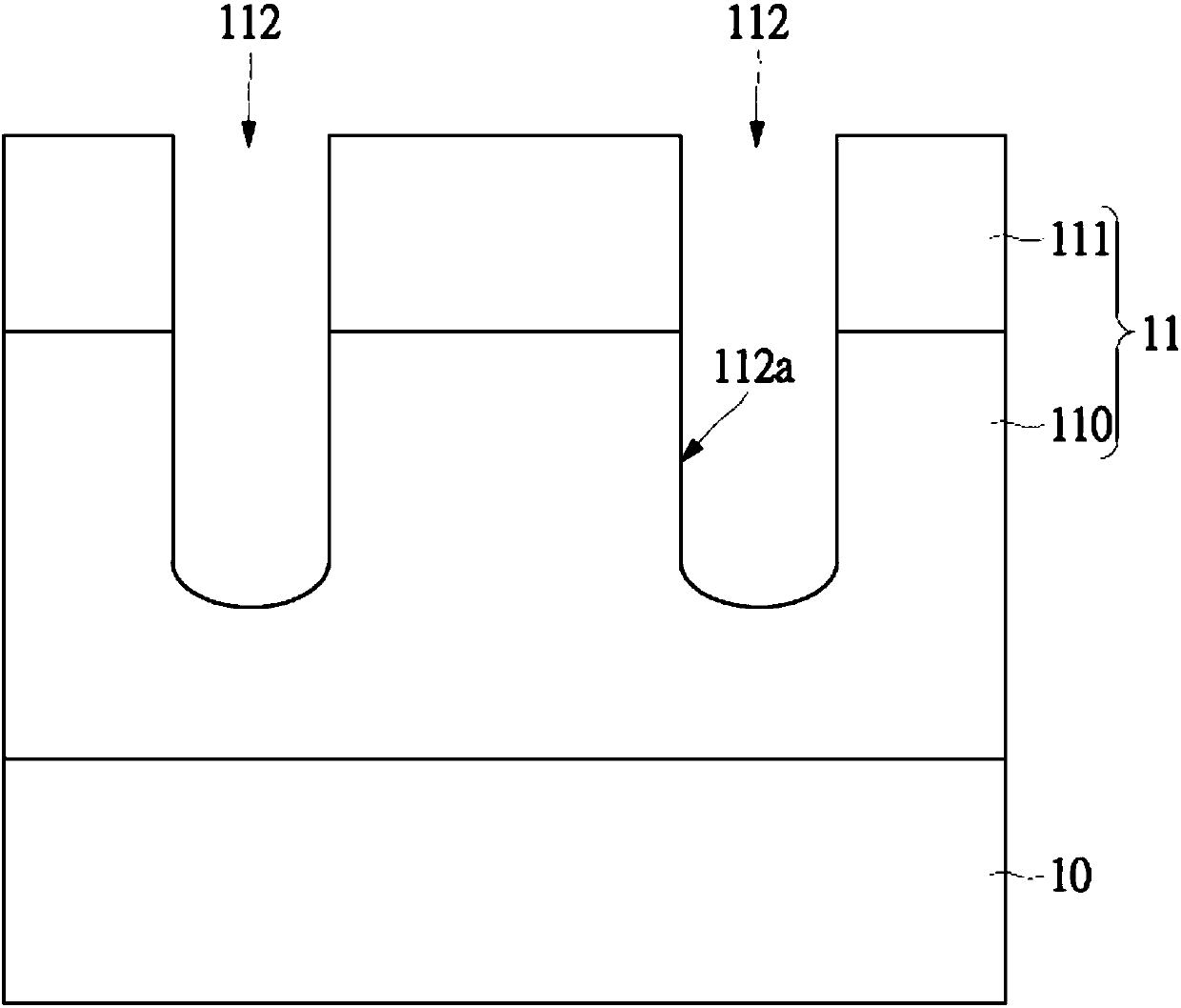

[0022] Please refer to figure 1 , shows a flowchart of a method for manufacturing a trench power semiconductor device according to an embodiment of the present invention. Also, please refer to Figure 2A to Figure 2J , respectively depict a partial cross-sectional schematic view of each step of the trench type power semiconductor device according to an embodiment of the present invention.

[0023] In step S100 , an epitaxial layer 11 is formed on the substrate 10 . Please refer to Figure 2A . Figure 2A A substrate 10 is shown in , and an epitaxial layer (epitaxial layer) 11 has been formed on the substrate 10, wherein the substrate 10 is, for example, a silicon substrate (silicon substrate), which has a first heavily doped region with a high doping concentration The epitaxial layer 11 has a low doping concentration to serve as the drain of the trench power MOSFET.

[0024] The substrate 10 has a high concentration of impurities of the first type conductivity, forming a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More