Patents

Literature

59results about How to "Lower power consumption levels" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

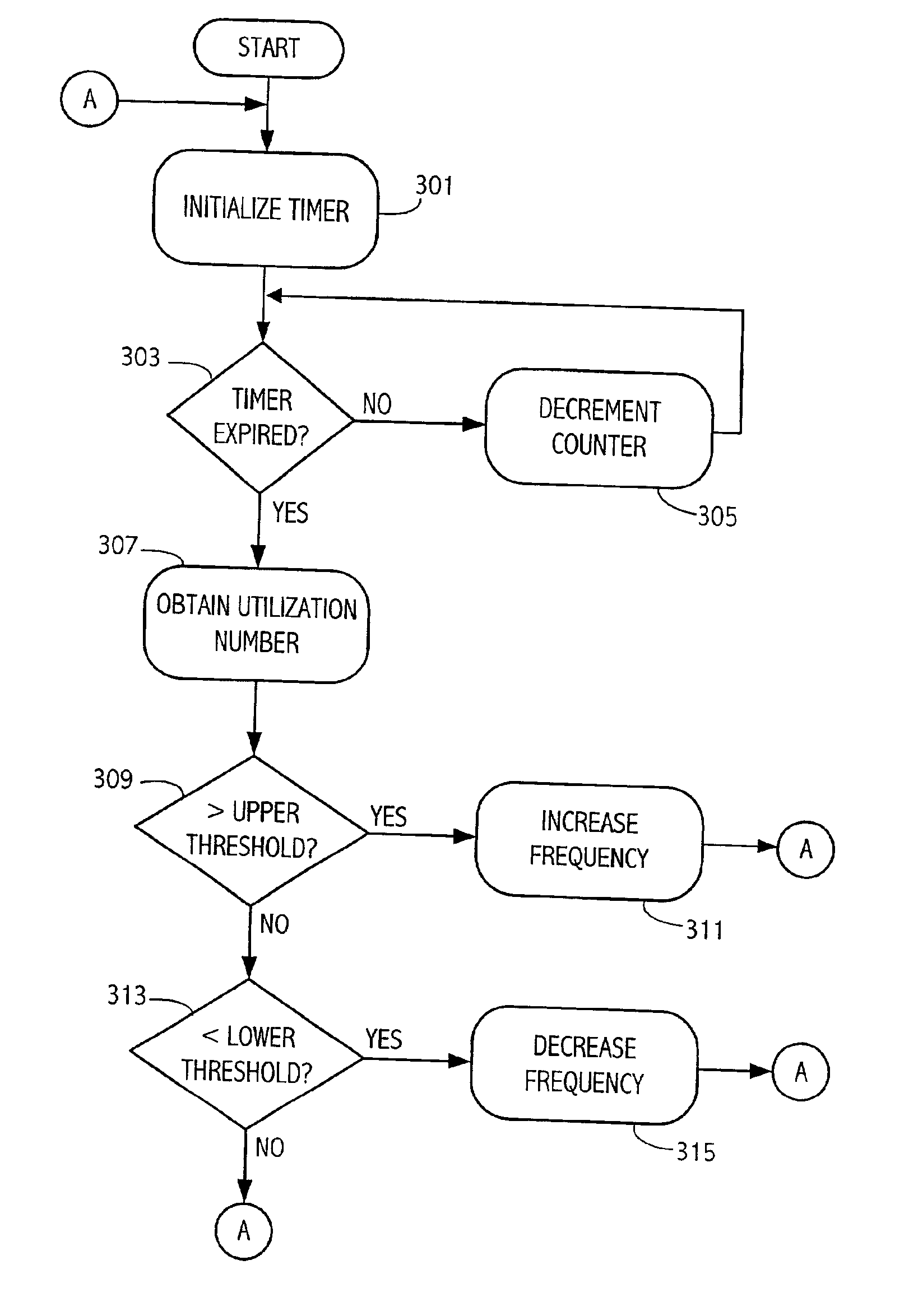

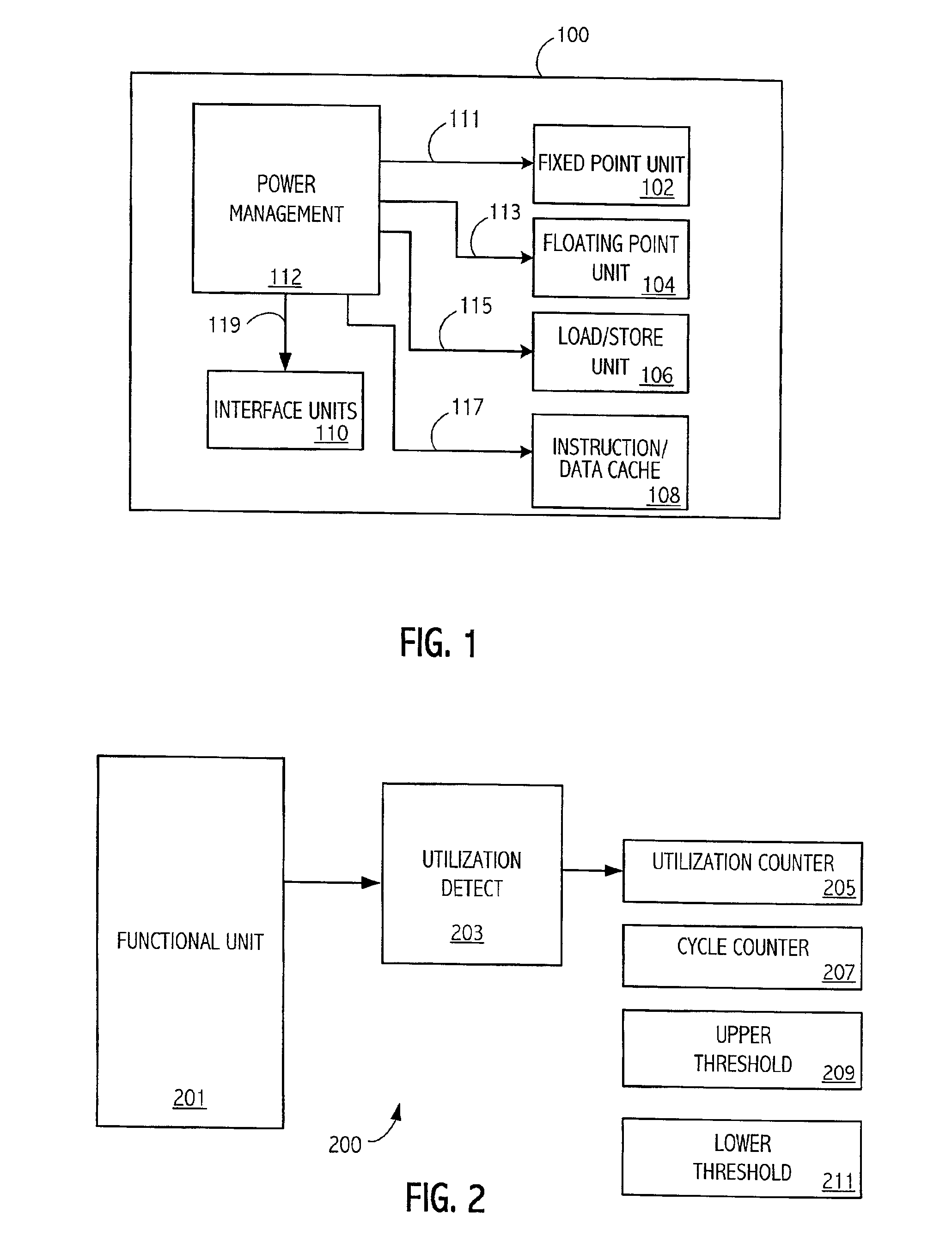

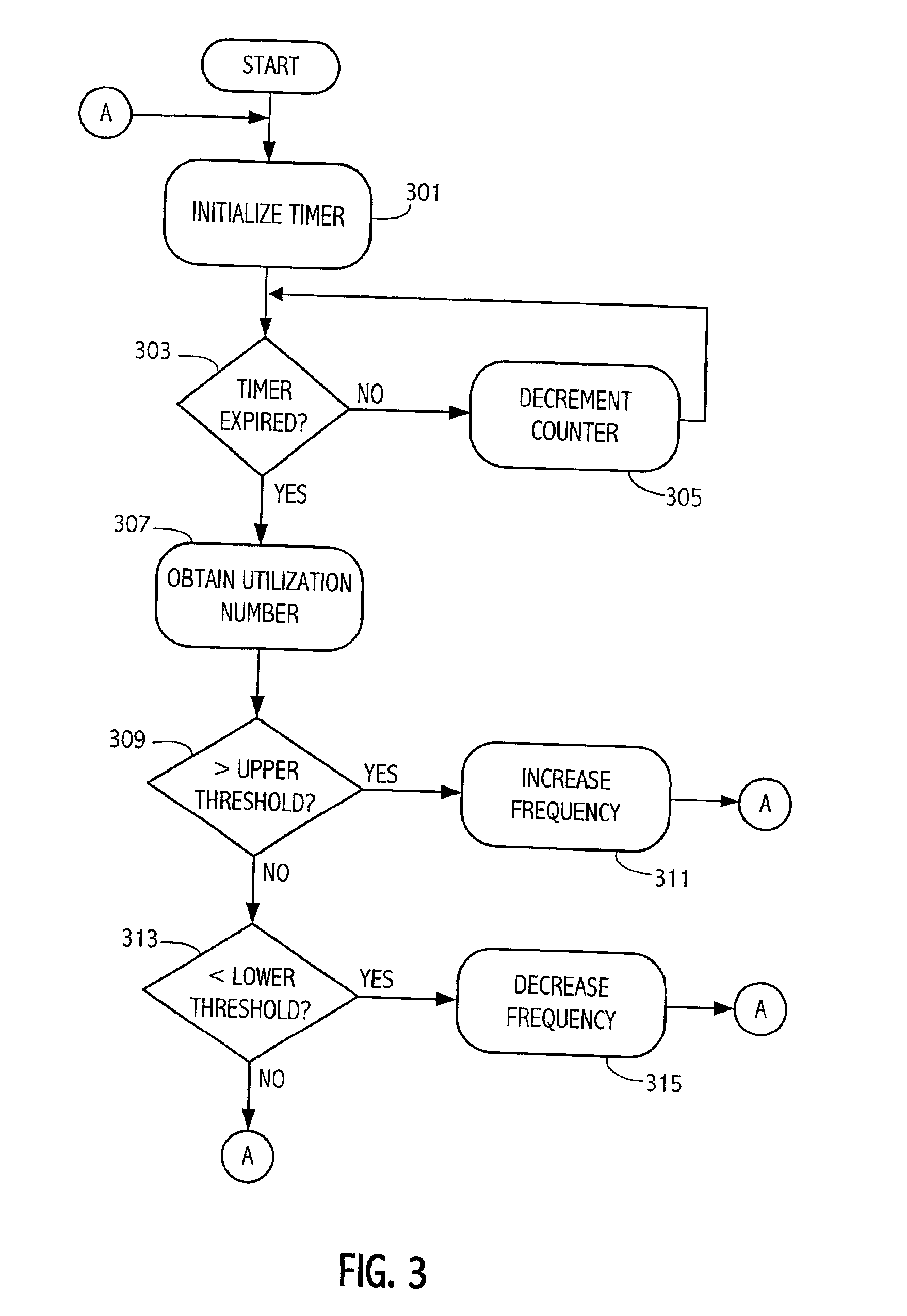

Performance and power optimization via block oriented performance measurement and control

InactiveUS6895520B1Improve the level ofIncrease power consumptionEnergy efficient ICTVolume/mass flow measurementEngineeringIntegrated circuit

An integrated circuit includes a plurality of functional blocks. Utilization information for the various functional blocks is generated. Based on that information, the power consumption and thus the performance levels of the functional blocks can be tuned. Thus, when a functional block is heavily loaded by an application, the performance level and thus power consumption of that particular functional block is increased. At the same time, other functional blocks that are not being heavily utilized and thus have lower performance requirements can be kept at a relatively low power consumption level. Thus, power consumption can be reduced overall without unduly impacting performance.

Owner:ADVANCED MICRO DEVICES INC

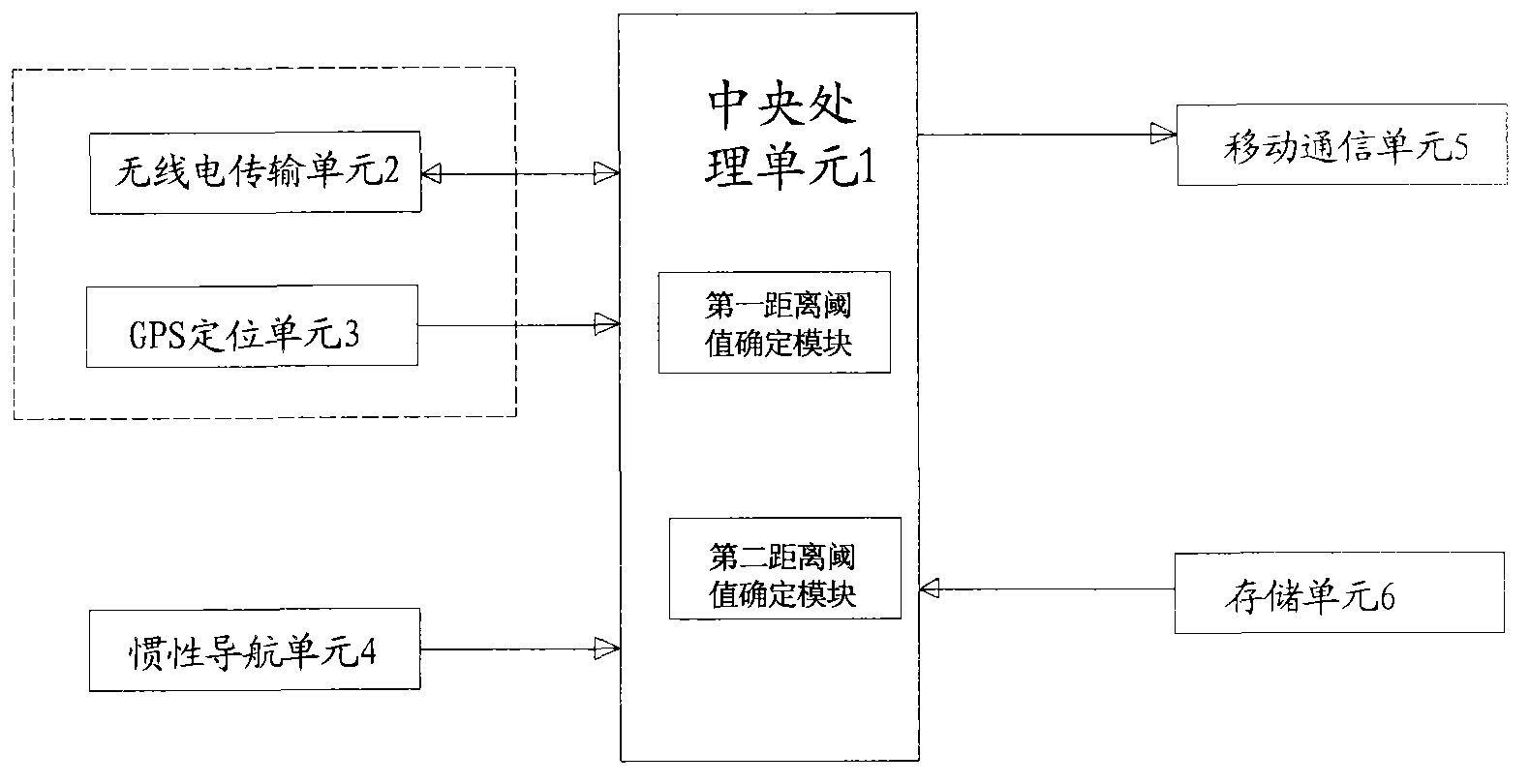

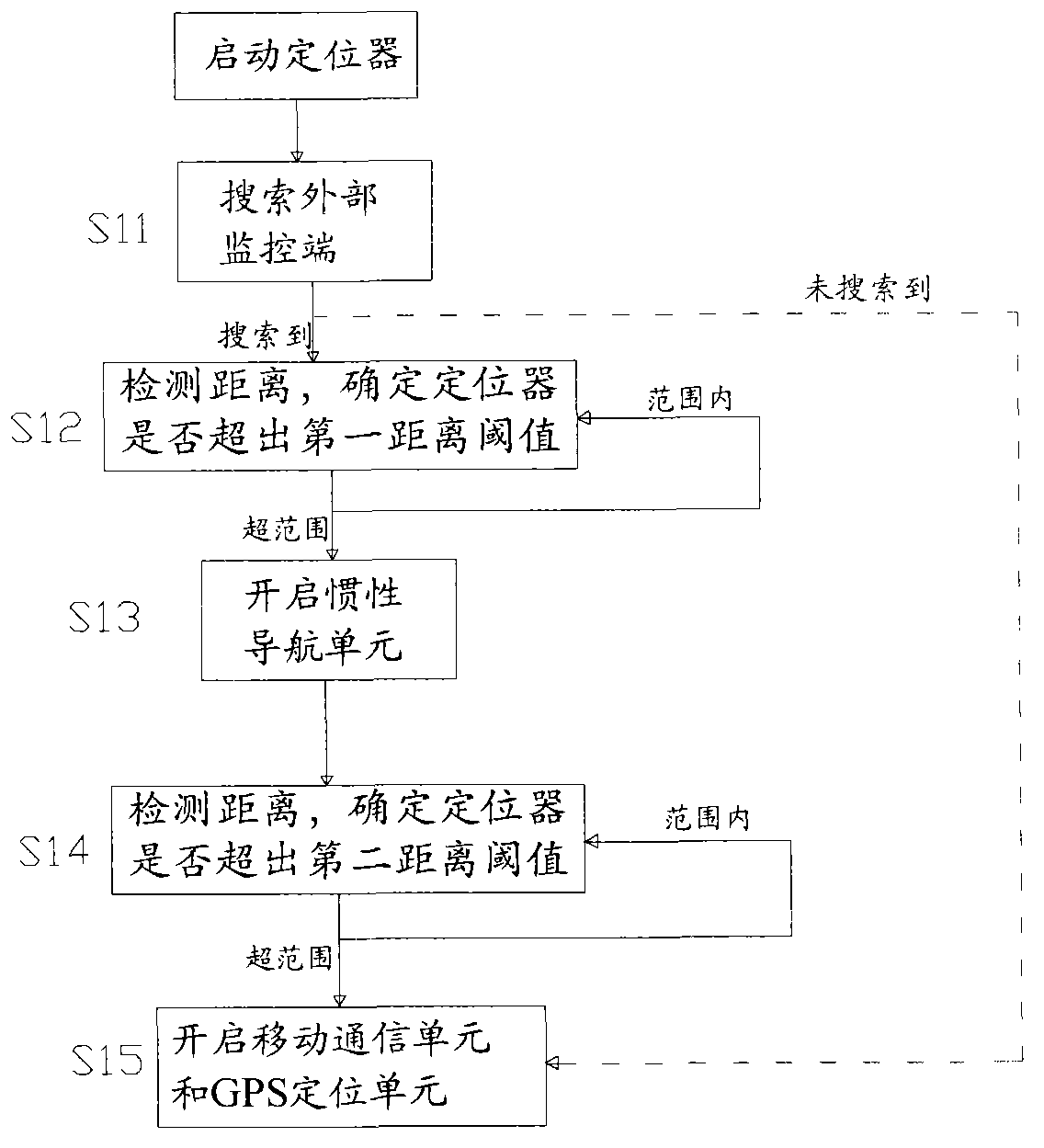

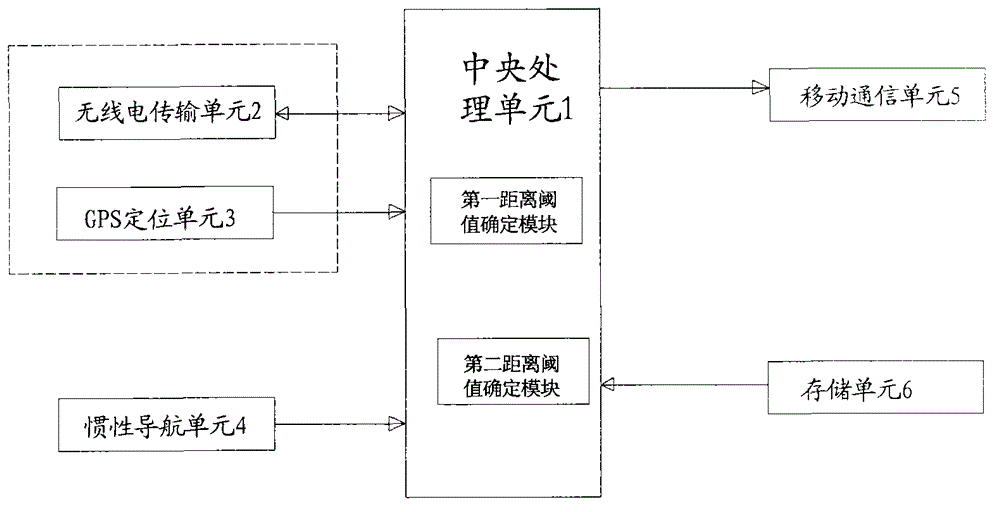

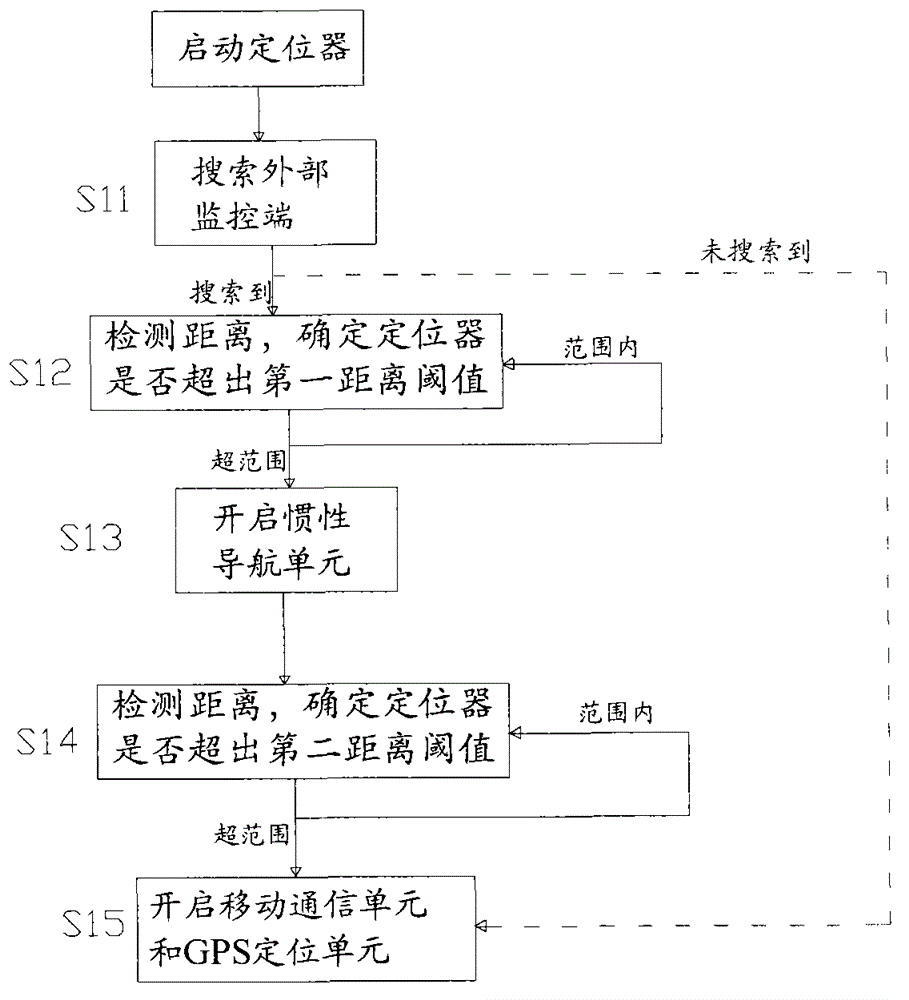

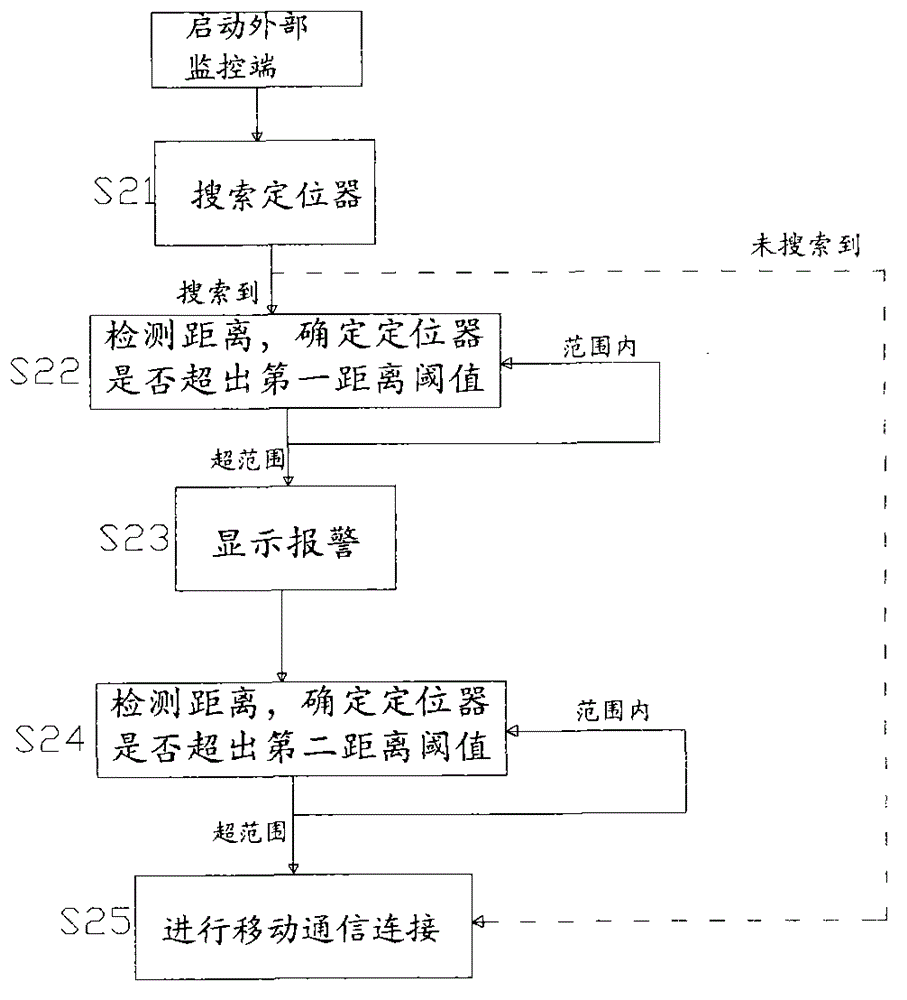

Locator-based locating method

ActiveCN103237292ASolve power consumptionSolve the problem of indoor positioning trackingEnergy efficient ICTNear-field systems using receiversGyroscopeAccelerometer

The invention provides a locator-based locating method. A locator comprises a central processing unit, a wireless unit, a global positioning system (GPS) locating unit, an inertial navigation unit, a mobile communication unit and a storage unit. The method comprises the following steps that a corresponding external monitoring end is searched based on a wireless detection signal; whether the current distance between the locator and the external monitoring end exceeds a first distance threshold value is determined based on the current wireless signal intensity and a mapping table stored in the storage unit; the inertial navigation unit is started when the current distance exceeds the first distance threshold value; whether the current distance exceeds a second distance threshold value is determined by detecting whether wireless connection can be established between the locator and the external monitoring end; and the mobile communication unit and the GPS locating unit are started when the current distance exceeds the second distance threshold value. By combining low power consumption Bluetooth, wireless fidelity (WIFI), a gyroscope and an accelerometer, the problem of power consumption due to the sustained use of a mobile network and GPS locating is solved.

Owner:钟国峰

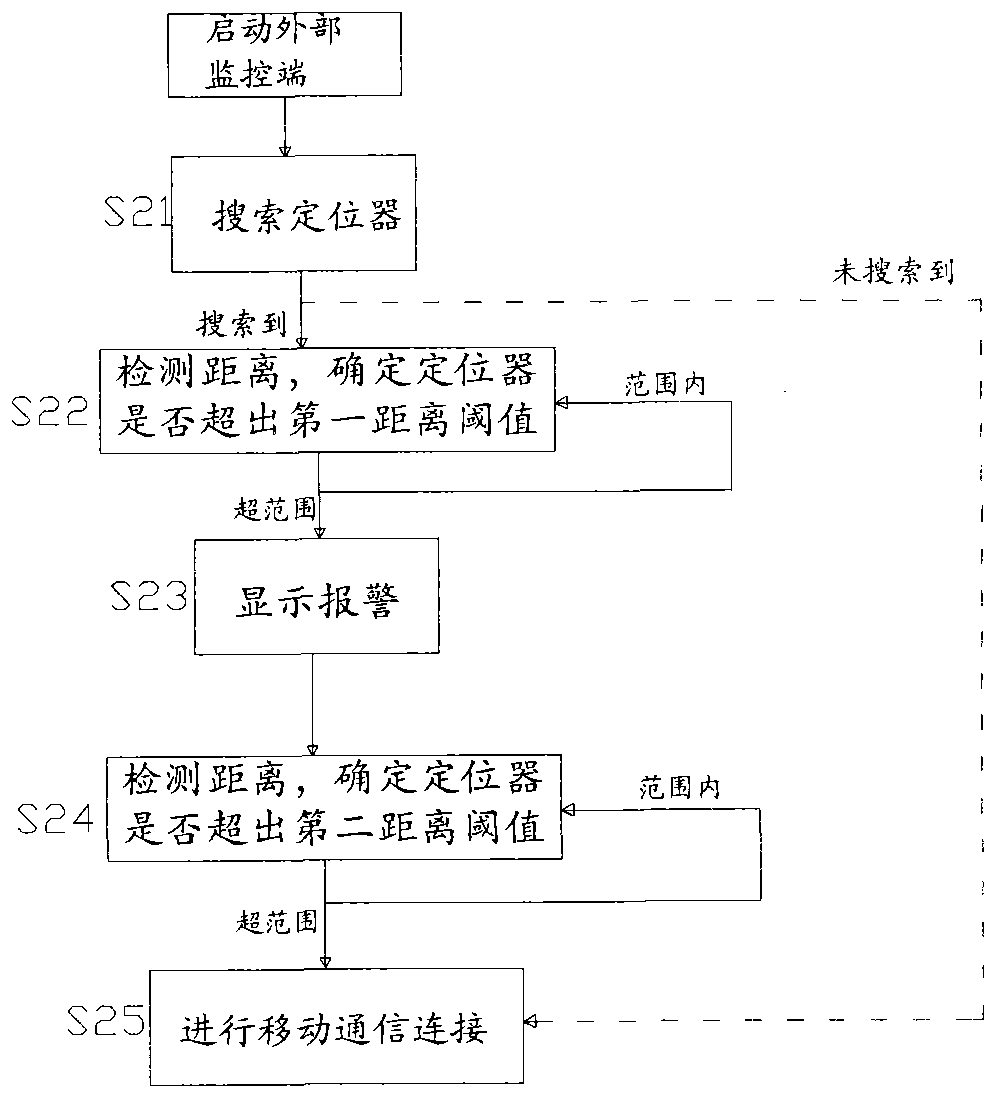

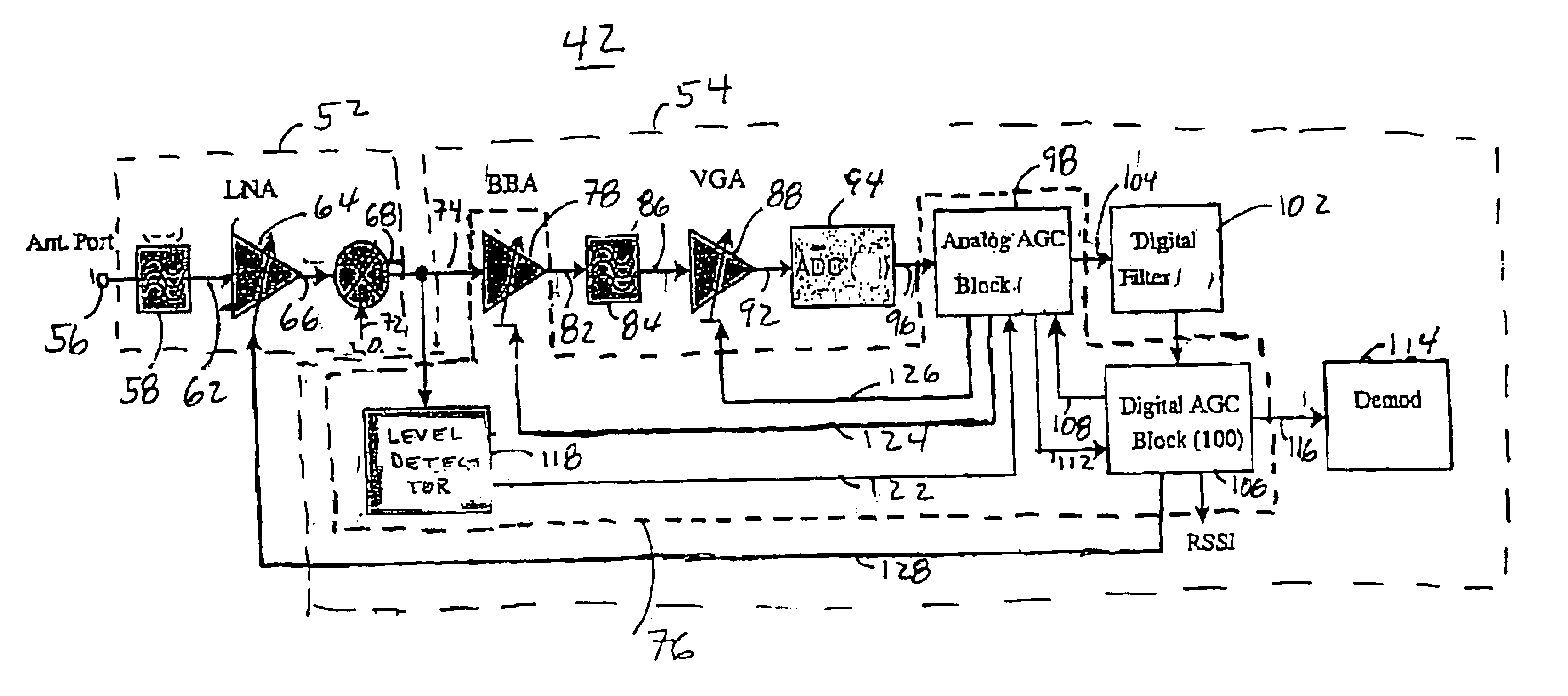

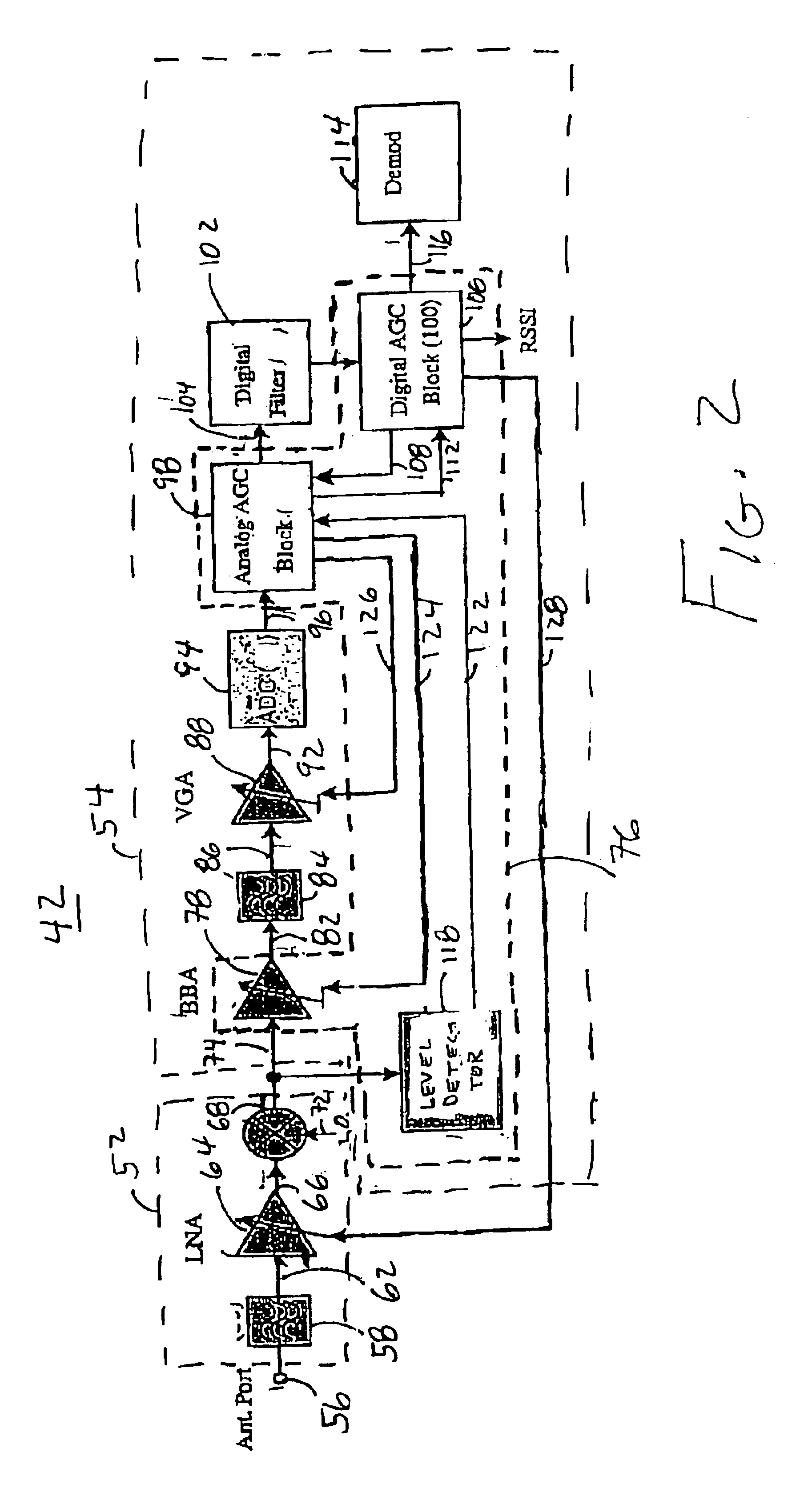

Apparatus, and an associated method, for increasing receiver sensitivity of a direct conversion receiver

InactiveUS6950641B2Improve performanceExcellent characteristicsGain controlRadio transmissionAudio power amplifierDirect-conversion receiver

Apparatus, and an associated method, for a direct conversion receiver by which to selectably increase the sensitivity of the receiver. The direct conversion receiver includes a baseband amplifier positioned in front of a baseband filter, and coupled to receive a direct-converted baseband signal. The gain at which the baseband amplifier amplifies the signal provided thereto is selected, in combination with gains applied to other amplification elements of the direct conversion receiver to distribute the gain across the receive chain. When a signal received at the receiver includes a large interfering signal component, the gain of the baseband amplifier is reduced to lessen the possibility that the amplified signal become saturated. A gain controller controls the gain of the amplification elements.

Owner:NOKIA CORP

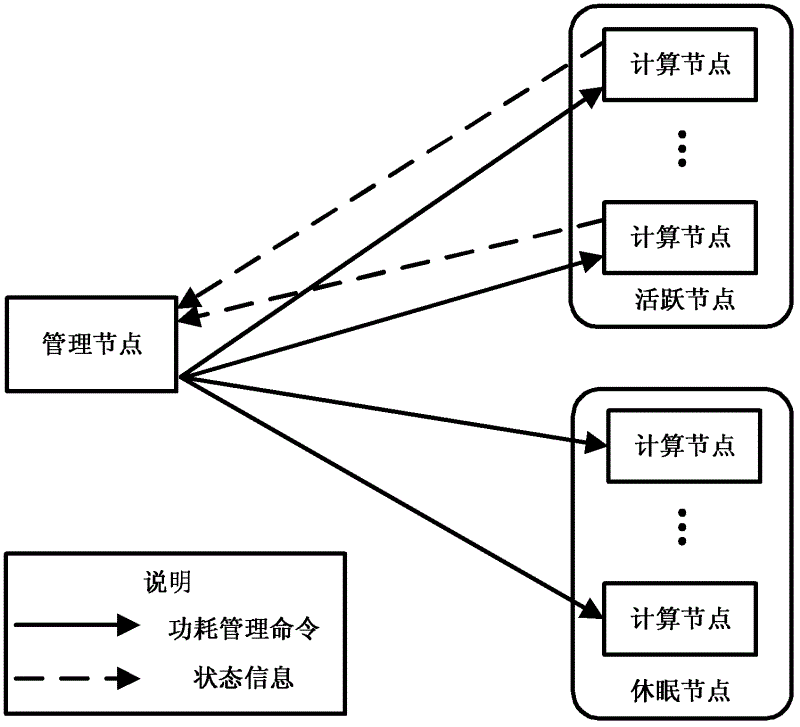

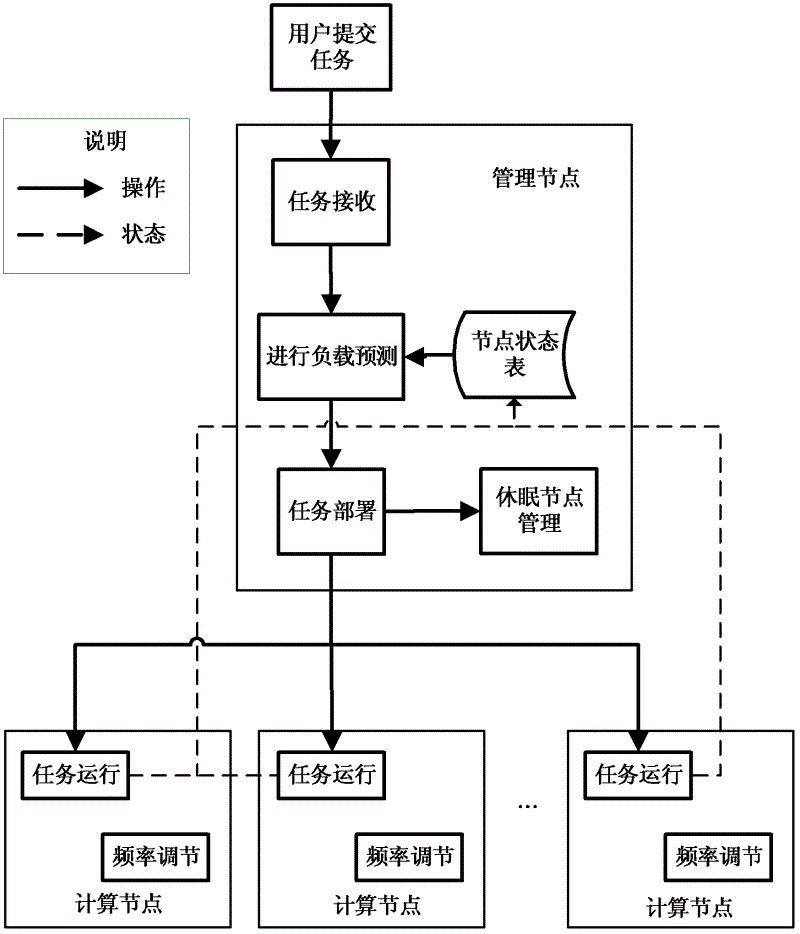

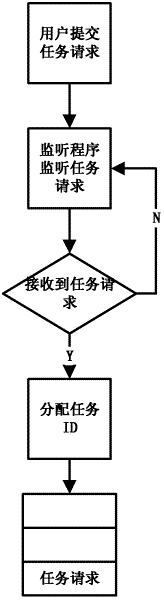

Self-learning load prediction based cluster on-demand starting method

ActiveCN102622273ALower power consumption levelsReduce energy consumptionEnergy efficient ICTResource allocationTask PerformancesDormancy

The invention discloses a self-learning load prediction based cluster on-demand starting method, which includes the following steps of receiving a task from a user by management nodes and predicting load of the task according to historic load information; computing increased CPU (central processing unit) utilization rate after the task is dispatched to any one of computing nodes; searching and selecting an underloading computing node in the computing nodes; selecting a dormant computing node to wake up if the underloading computing node is not found; dispatching the task on the selected computing node; building a new thread to execute the task after the computing node receives the task; feeding back execution results of the task to the management nodes after the task is completed, feeding load information of the task back to the management nodes to be stored in historic load information; and setting the computing nodes without loading tasks in a certain time into dormancy by the management nodes at regular intervals. Power consumption of the integral cluster is reduced without affecting task performances by the self-learning load prediction based cluster on-demand starting method.

Owner:NAT UNIV OF DEFENSE TECH

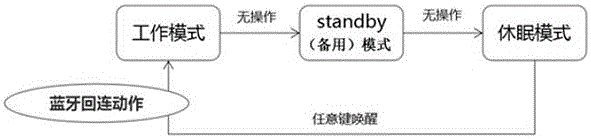

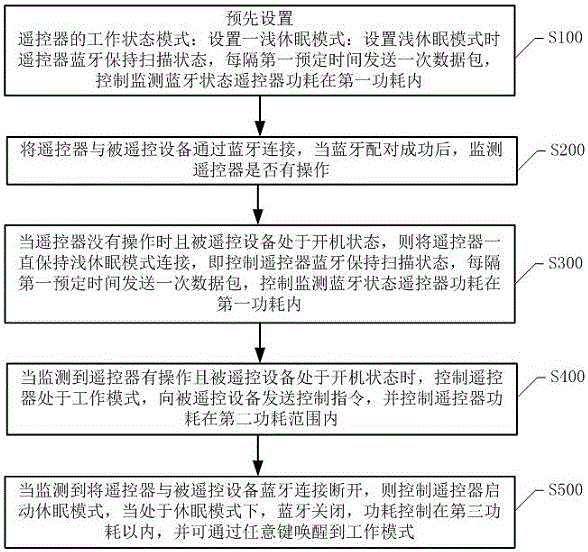

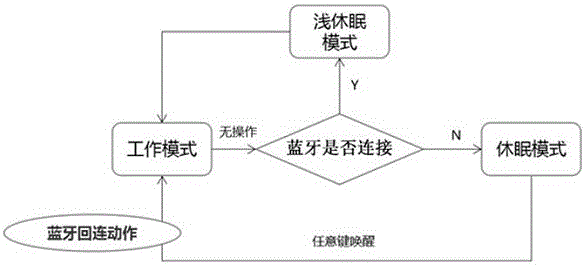

Method and system for processing remote controller connection

ActiveCN106131634AFix lag issuesLower power consumption levelsSelective content distributionDormancyStart up

The invention discloses a method and a system for processing a remote controller connection. The method comprises the steps of connecting a remote controller and a remotely controlled device via a Bluetooth, and after the Bluetooth pairing is successful, monitoring whether the remote controller has an operation; when the remote controller has no operation and the remotely controlled device is in a starting-up state, keeping the remote controller in a shallow dormancy mode connection all the time, namely controlling the Bluetooth of the remote controller to keep a scanning state, sending a data packet once every a first preset time, controlling and monitoring an energy of the remote controller in a Bluetooth state to be in the first energy; and when monitoring the Bluetooth connection between the remote controller and the remotely controlled device is disconnected, controlling the remote controller to start a dormancy mode, wherein the Bluetooth is closed when in the dormancy mode, the energy is controlled in the third energy, and a working mode can be awakened via any key. According to the method and the system disclosed by the invention, on the basis of the prior art, the energy mode of the remote controlled is modified, so the experience problem possibly due to a reconnection speed is solved, and the energy is guaranteed to be at a relatively low level.

Owner:KONKA GROUP

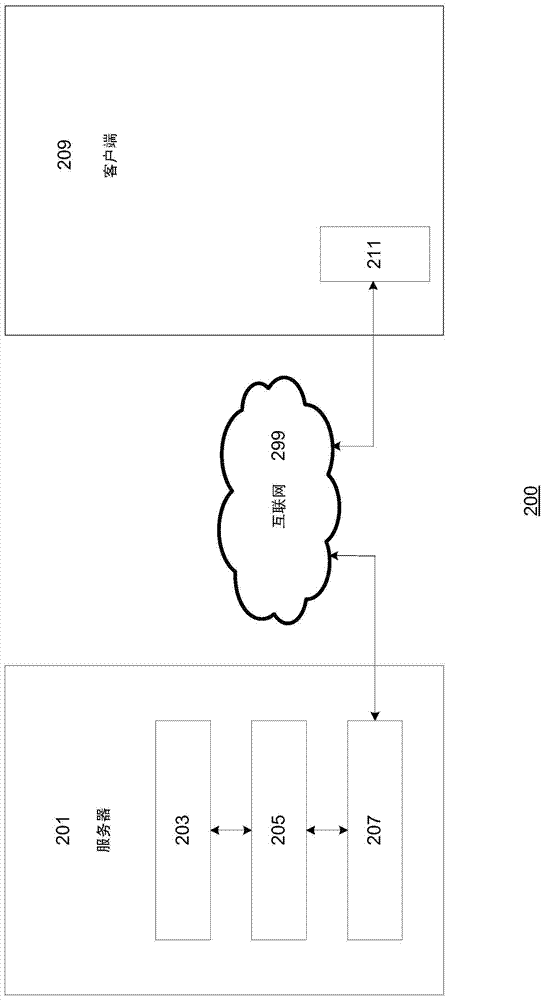

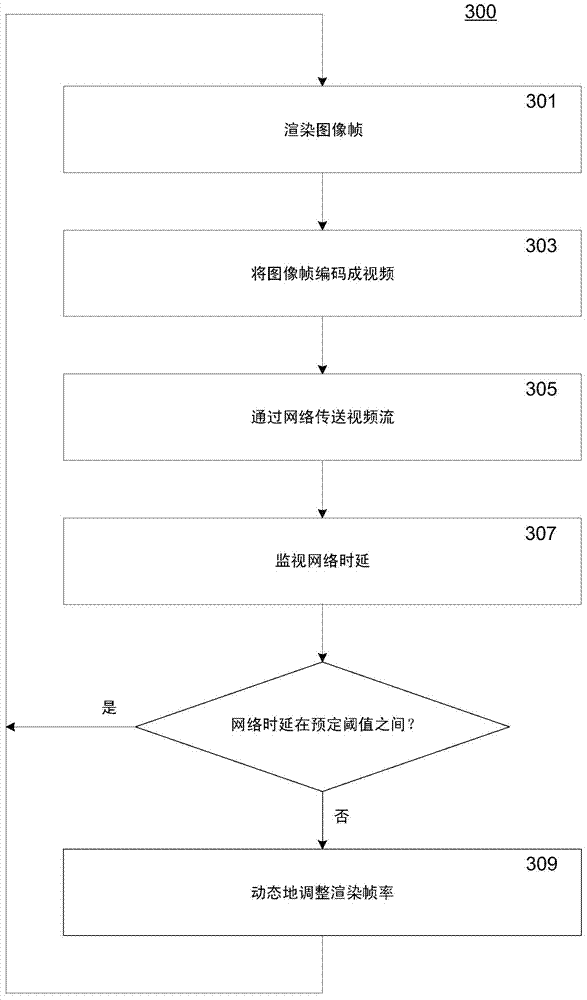

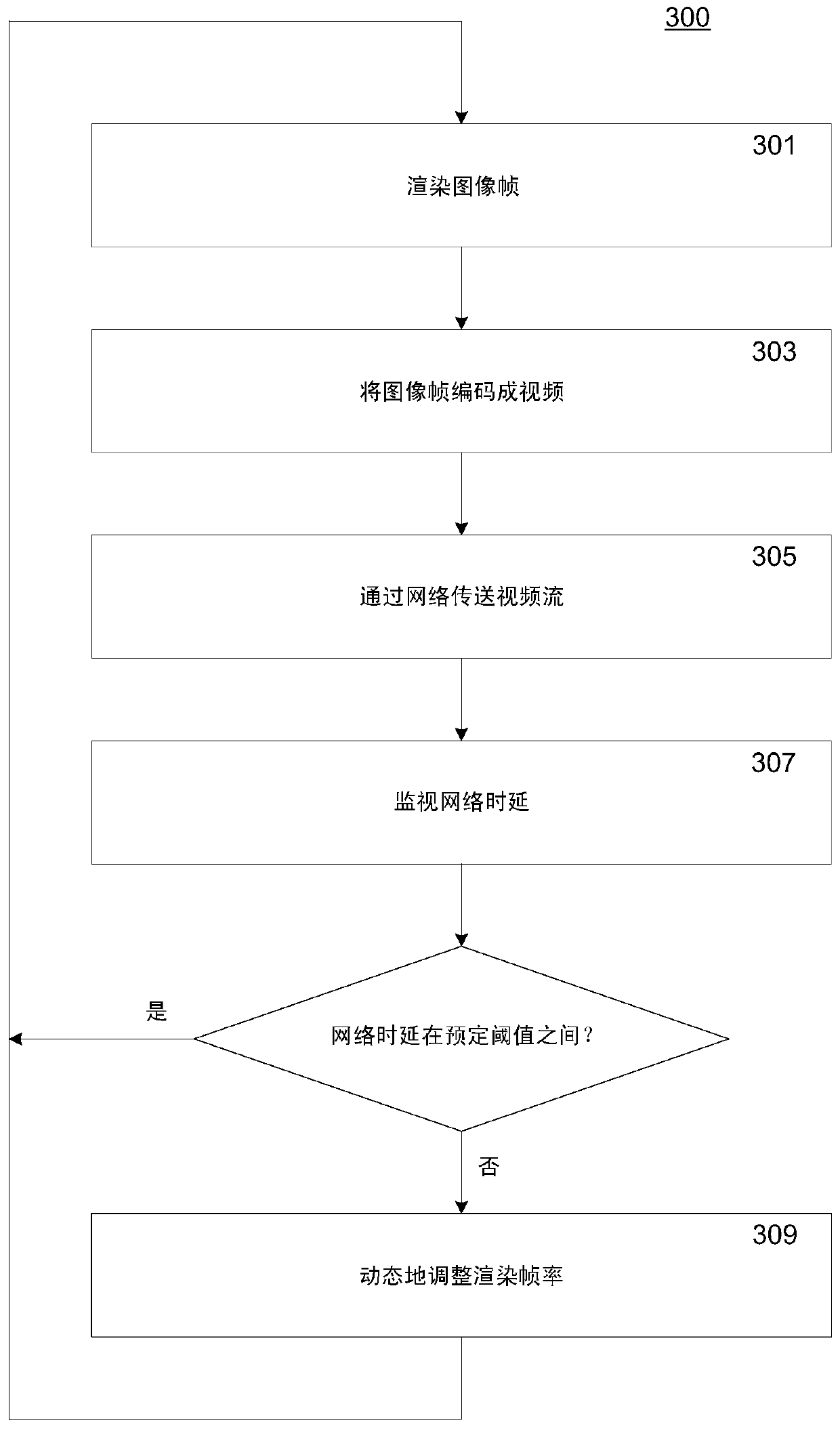

Network adaptive latency reduction through frame rate control

InactiveCN103905836AConsistent quality of serviceStable service qualityTransmissionSelective content distributionQuality of serviceNetwork conditions

Novel solutions are provided for consistent Quality of Service in cloud gaming system that adaptively and dynamically compensate for poor network conditions by moderating rendered frame rates using frame rate capping to optimize for network latency savings (or surplus). In further embodiments, the encoding / sent frame rate to the client can also be managed in addition, or as an alternative to capping the rendered frame rates. The claimed embodiments not only maintain a constant Quality of Service (QoS) for the user, but may also be employed to leverage higher-performing networks to reduce operational costs.

Owner:NVIDIA CORP

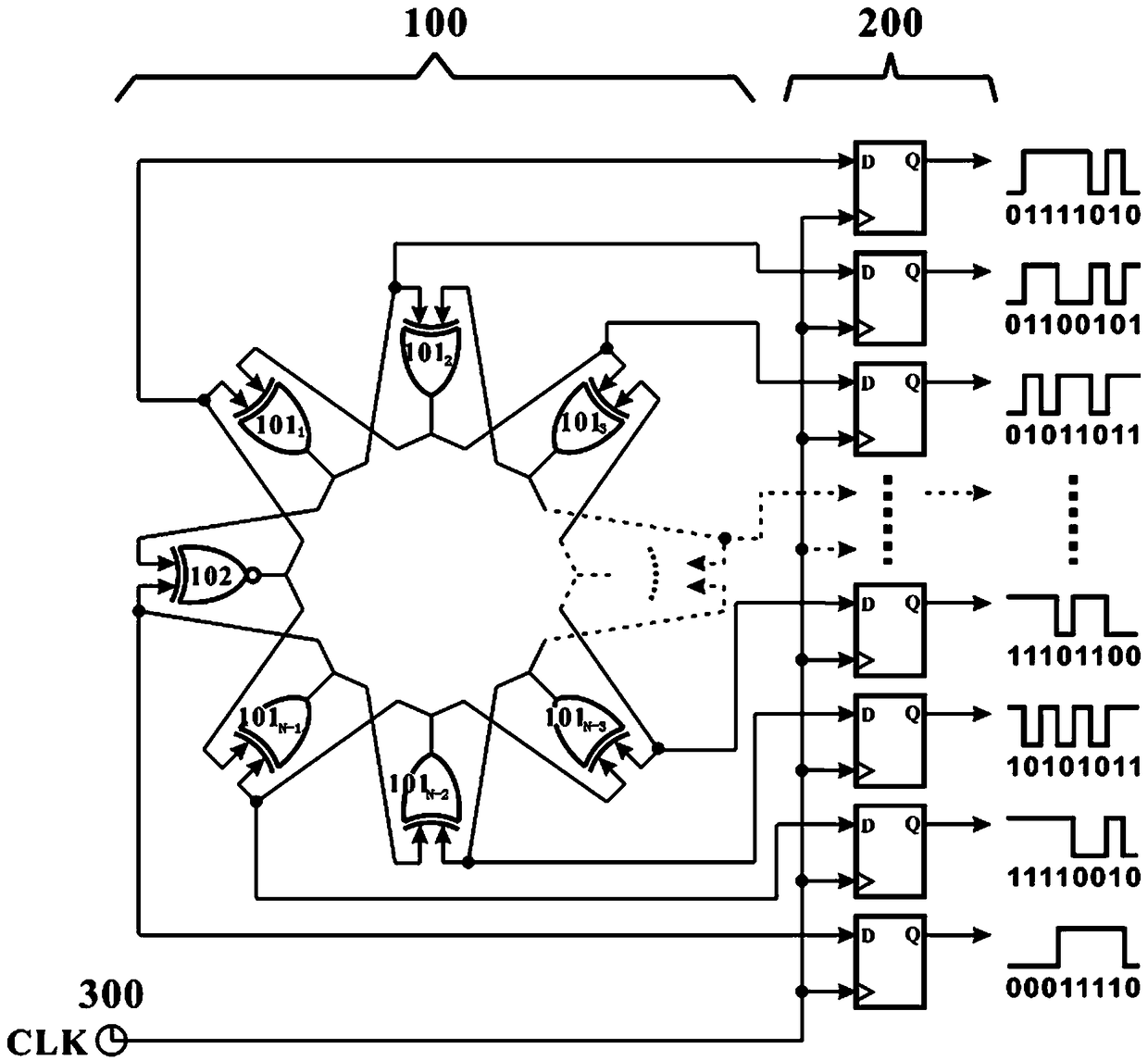

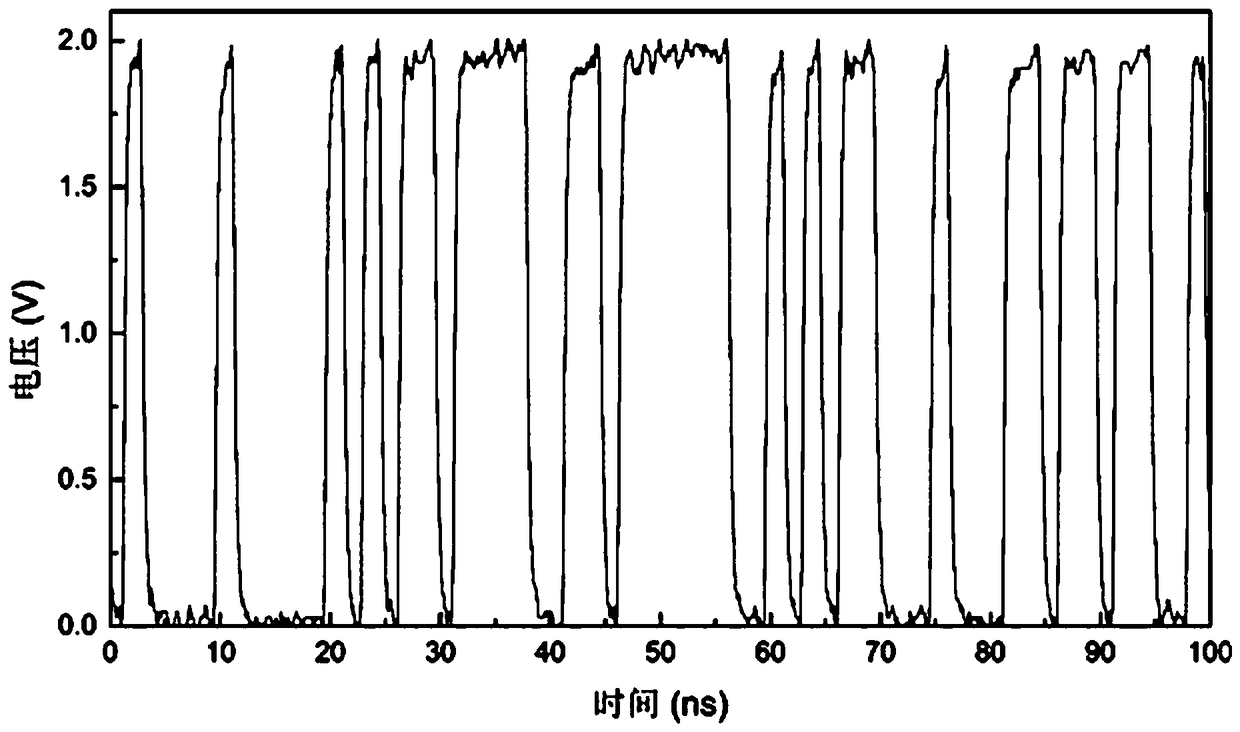

High-speed random number generation method and apparatus

ActiveCN108345446AIncrease spawn rateSimple structureRandom number generatorsFrequency spectrumBoolean network

The invention discloses a high-speed random number generation method and apparatus. The apparatus comprises two parts including an entropy source module and an entropy sampling module. The entropy source module is an autonomous Boolean network consisting of digital logic gates; the network consists of an XNOR gate and N-1 XOR gates; N is equal to 3n (n is a positive integer); and the entropy source module can generate a chaotic signal with a wide and flat spectrum. The entropy sampling module is composed of a D trigger, and performs sampling and quantization on the chaotic signal to generate arandom number sequence. The generated random number sequence can pass random number industry test standards (NIST and Diehard statistical tests), and has good random statistical characteristic. The apparatus consists of the digital logic gates, and is simple in circuit structure and easy to integrate and manufacture; and a post-processing algorithm or circuit necessary for a conventional random number generation apparatus is not required, so that the power consumption can be greatly reduced. The high-speed random number generation method and apparatus can be widely applied to the field of information security of secret communication, key distribution, data encryption and the like.

Owner:TAIYUAN UNIV OF TECH

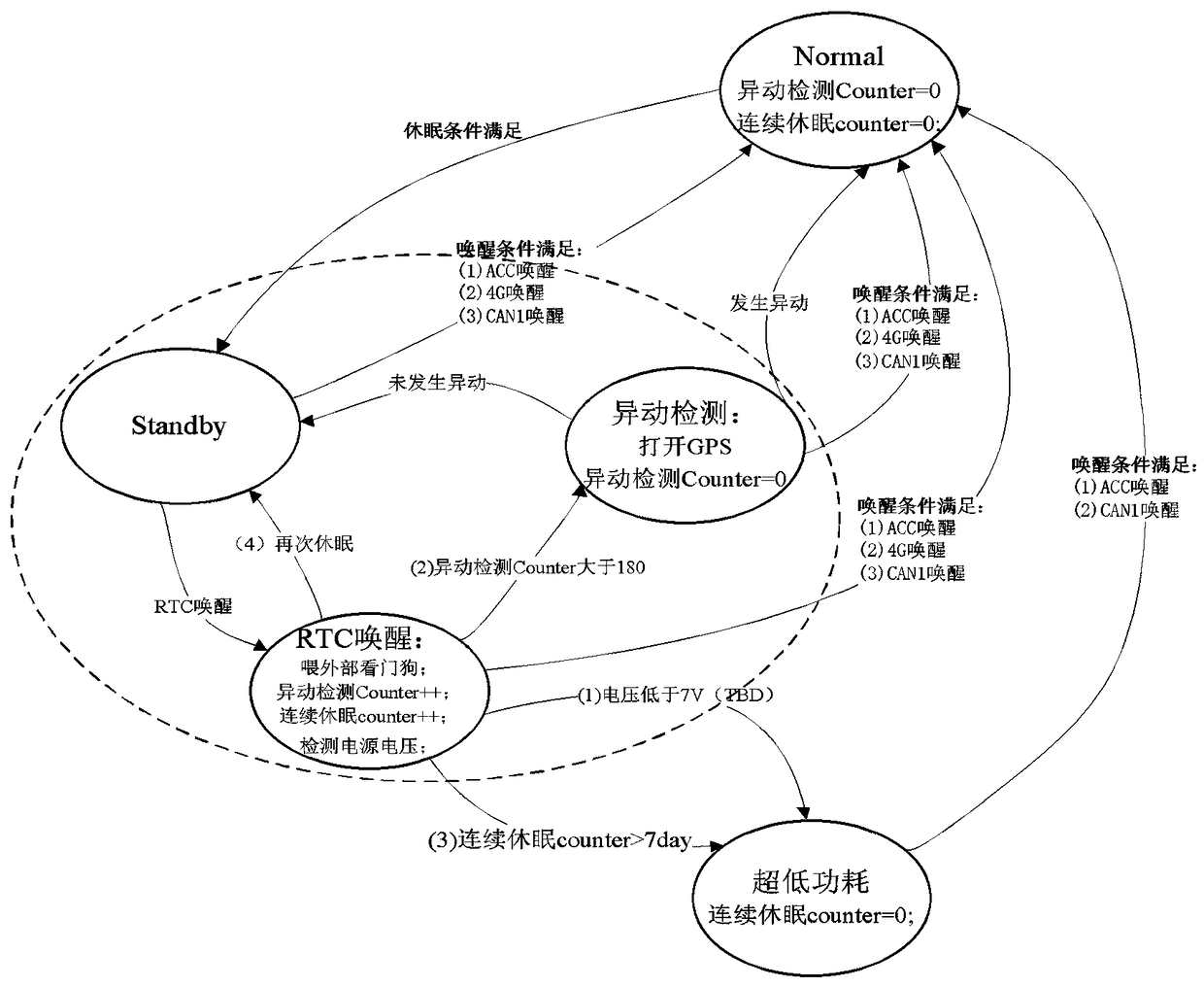

Internet-of-Vehicles terminal power control method

ActiveCN108819884ASmall working currentImprove experienceElectric/fluid circuitEnergy efficient vehicular chargingElectricityThe Internet

The invention relates to an Internet-of-Vehicles terminal power control method. A power management module is arranged in an Internet-of-Vehicles terminal to take charge of power-on, power-off, dormancy and awakening functions of vehicle-mounted functional modules, and a reliable and low-energy-consumption voltage logic operation control strategy is provided for a whole system. The control strategyincludes three working states which are the full working mode, a low power consumption mode and an ultra-low power consumption mode. After the system is powered on, the power management module adoptsa full power-on mode to start all the vehicle-mounted functional modules and enters in a Normal mode, and a state machine monitors the working state of the system in real time; after an active dormancy signal is received, the system enters in a front / transitional state, the related functional modules are sequentially stopped according to a set sequence, after all dormancy conditions are met, thesystem enters in the low power consumption dormancy state, and an overtime detection program is started; and after the current working state meets the ultra-low power consumption dormancy condition, the system enters in the ultra-low power consumption dormancy mode, and a deep electricity saving requirement is met.

Owner:JIANGLING MOTORS

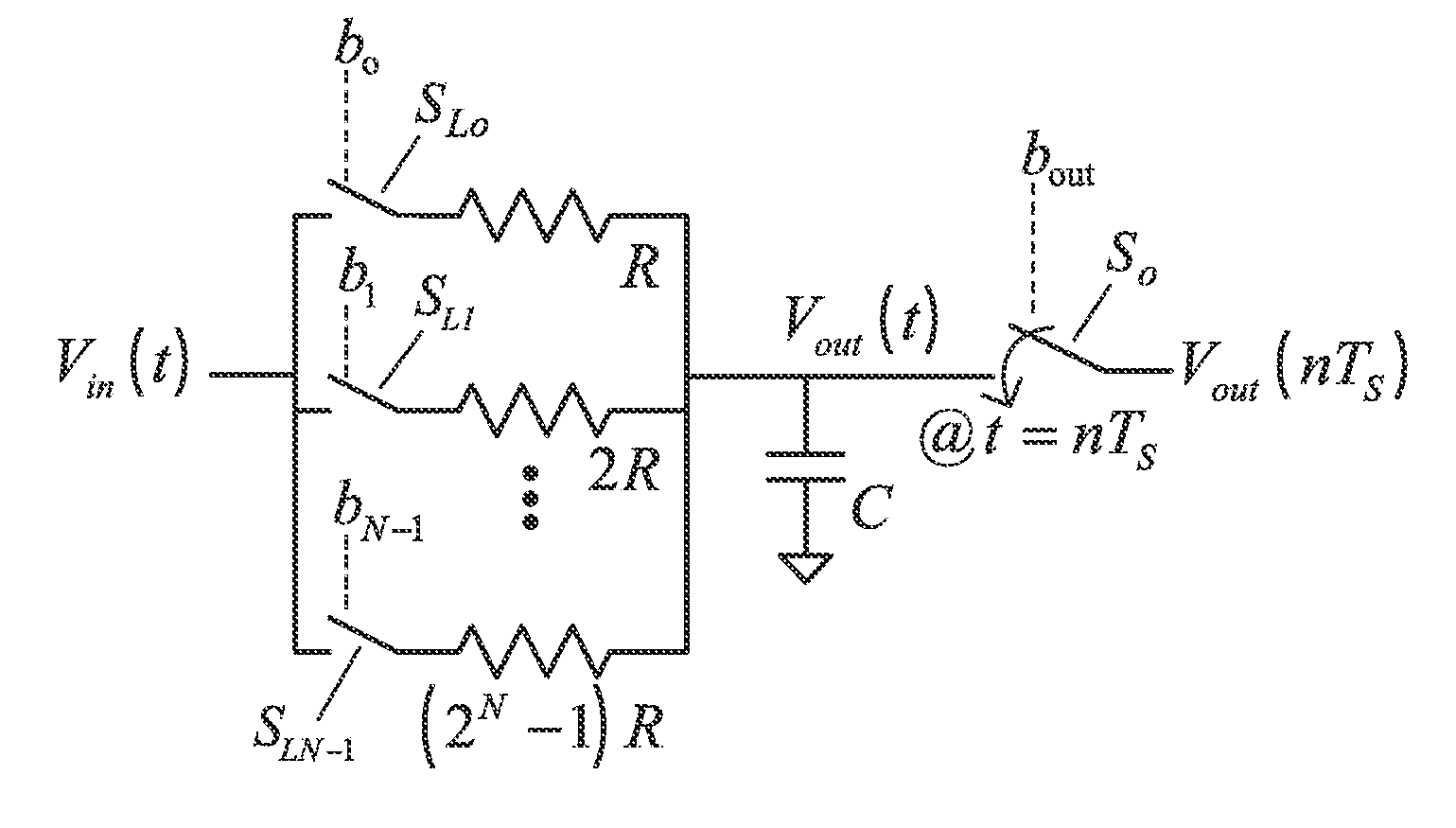

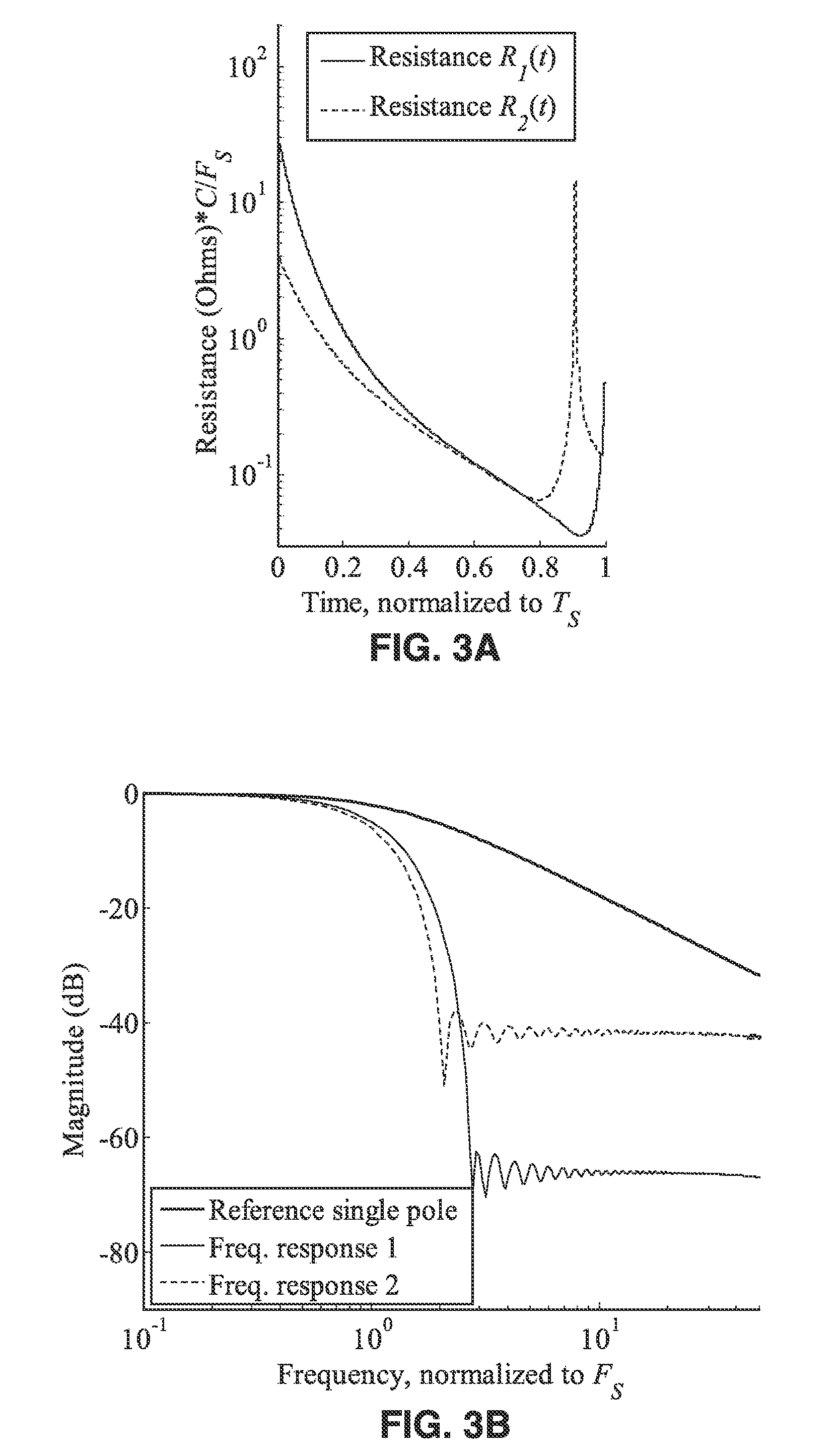

Sharp programmable filters using periodically time-varying components

ActiveUS20140333373A1Easy to implementLower power consumption levelsMultiple-port networksTime-varying networkElectrical resistance and conductanceCapacitance

A method and apparatus for selective programmable filtering using analog circuits with time-varying components (e.g., resistances, capacitances) is presented. An analog front end receives an electronic signal and filters said signal by a passive or active continuous-time filter, having a combination of equivalent memory-less (e.g., resistive) and memory (e.g., capacitive or inductive) elements. A variable resistor circuit allows switching through a range of values to control one or more of the equivalent resistances of the passive or active continuous-time filter. The variable resistors are controlled using a control circuit to periodically modulate the resistances in the continuous-time filter between periodic sampling instances, such as during analog to digital conversion. Such periodic modulation of the resistances in the continuous-time filter allows for the programming and enhancement of the selectivity of said filter.

Owner:RGT UNIV OF CALIFORNIA

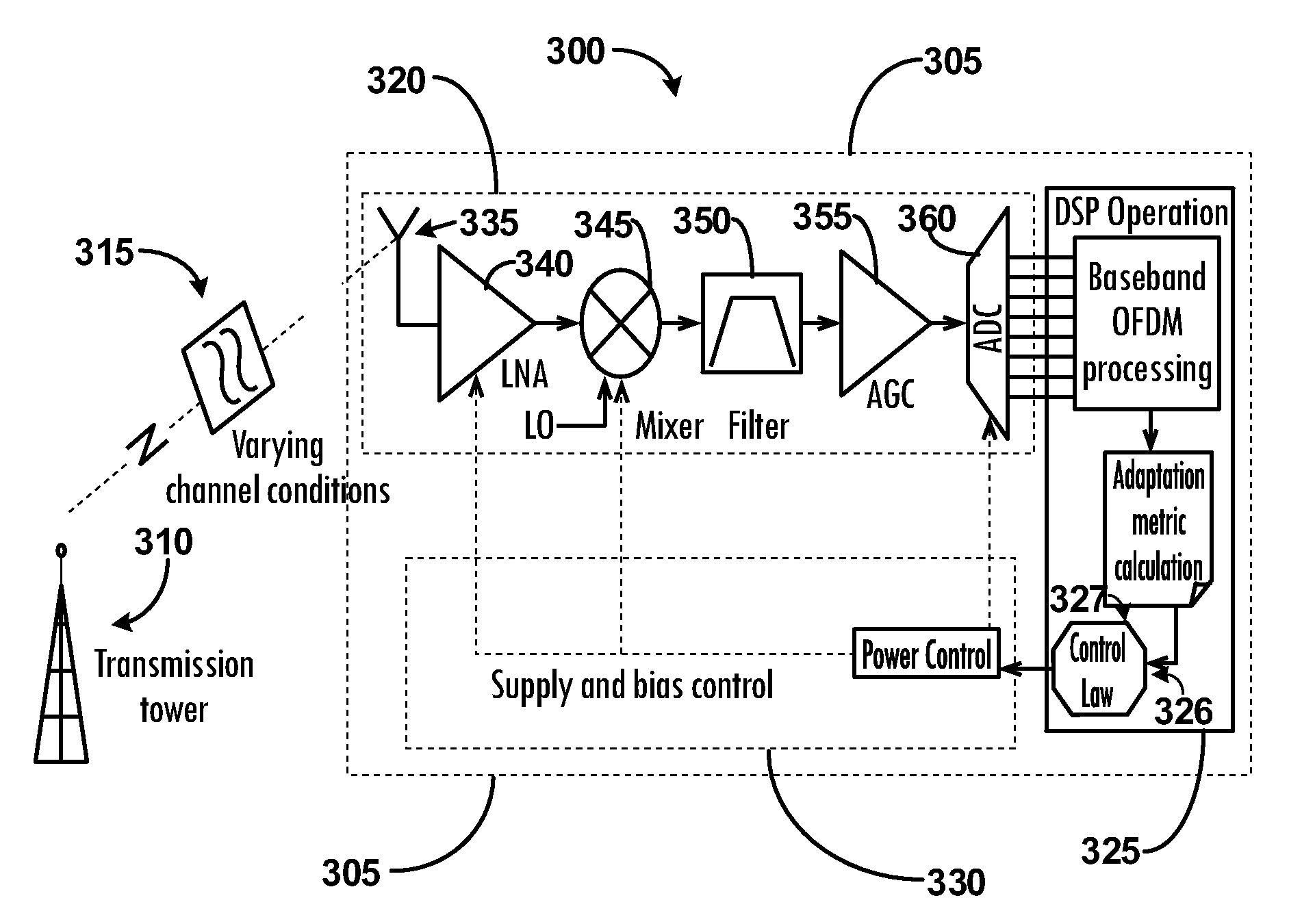

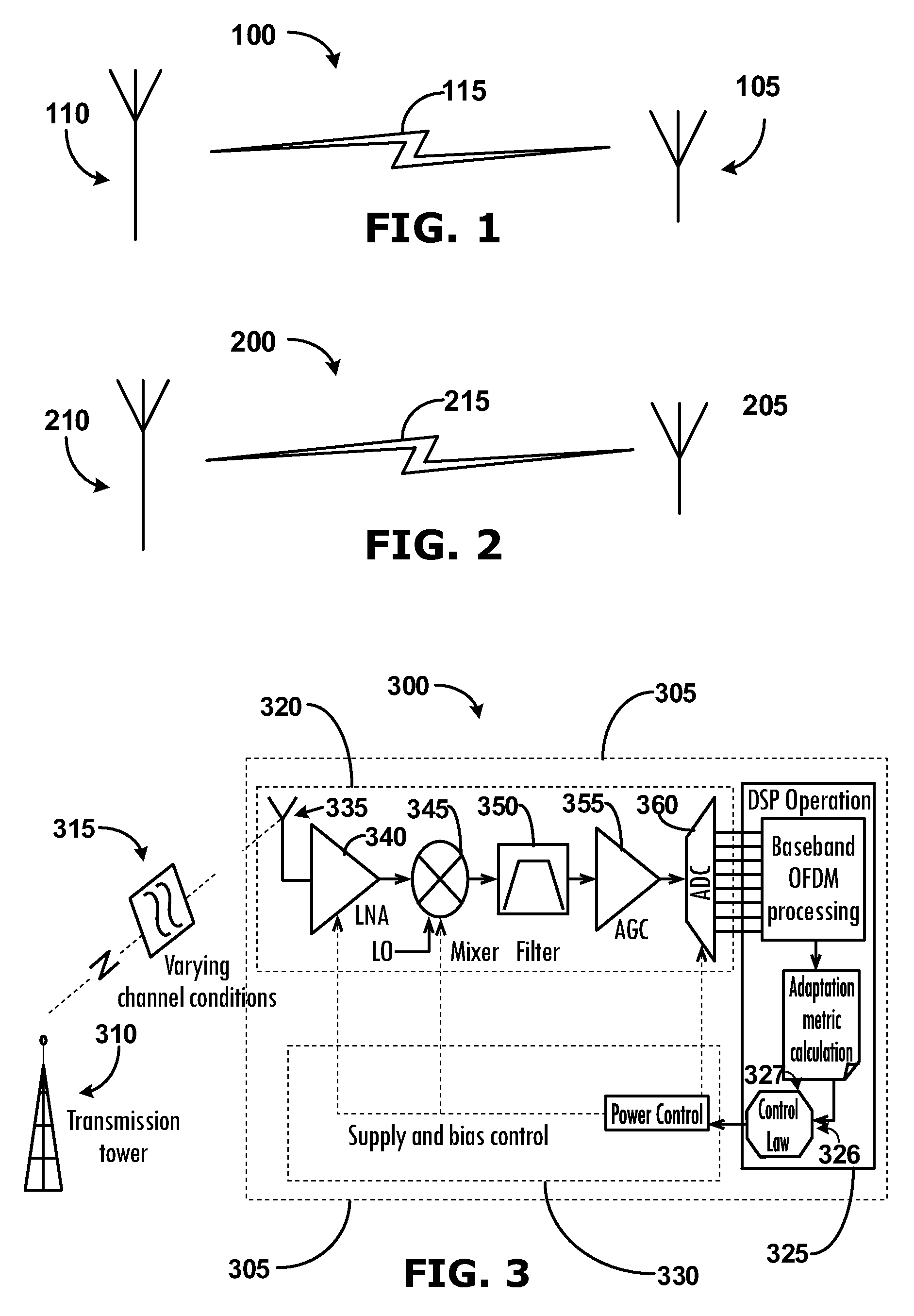

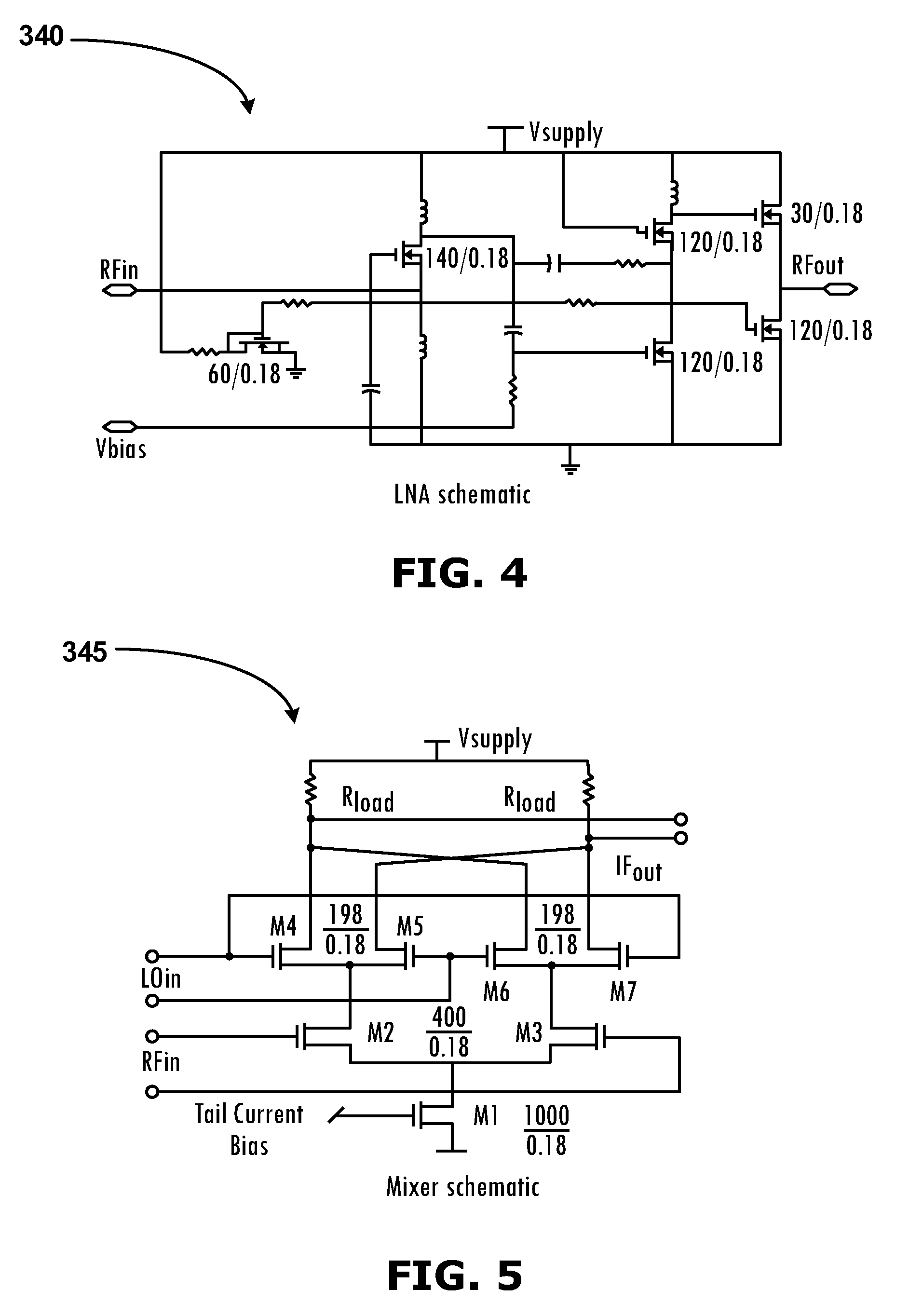

Methodology for designing environment adaptive ultra low power wireless communication systems and methods

InactiveUS8059571B2Lower power consumption levelsEnabling power conservationTransmission systemsNetwork traffic/resource managementSignal qualityCommunications system

Owner:GEORGIA TECH RES CORP

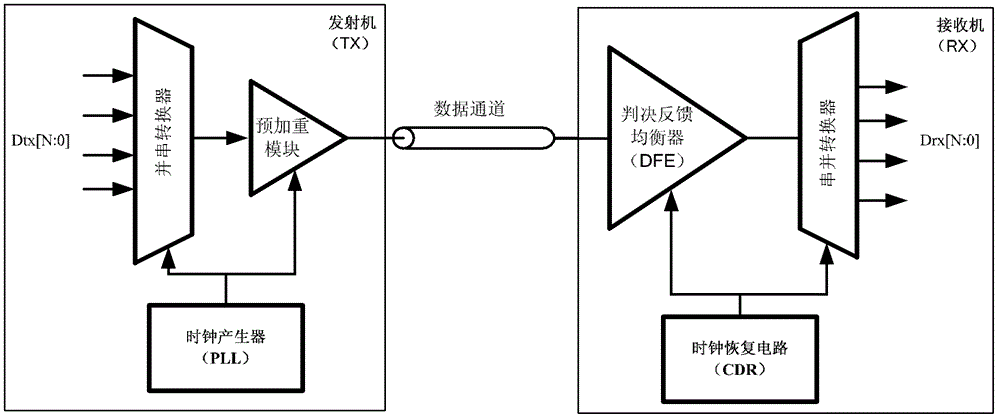

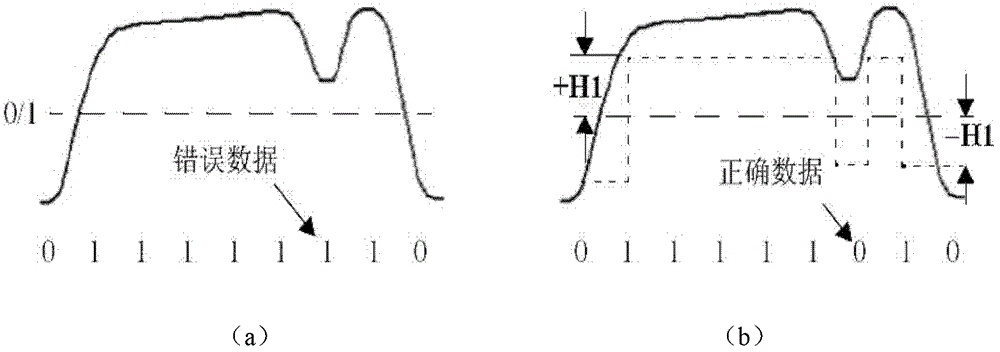

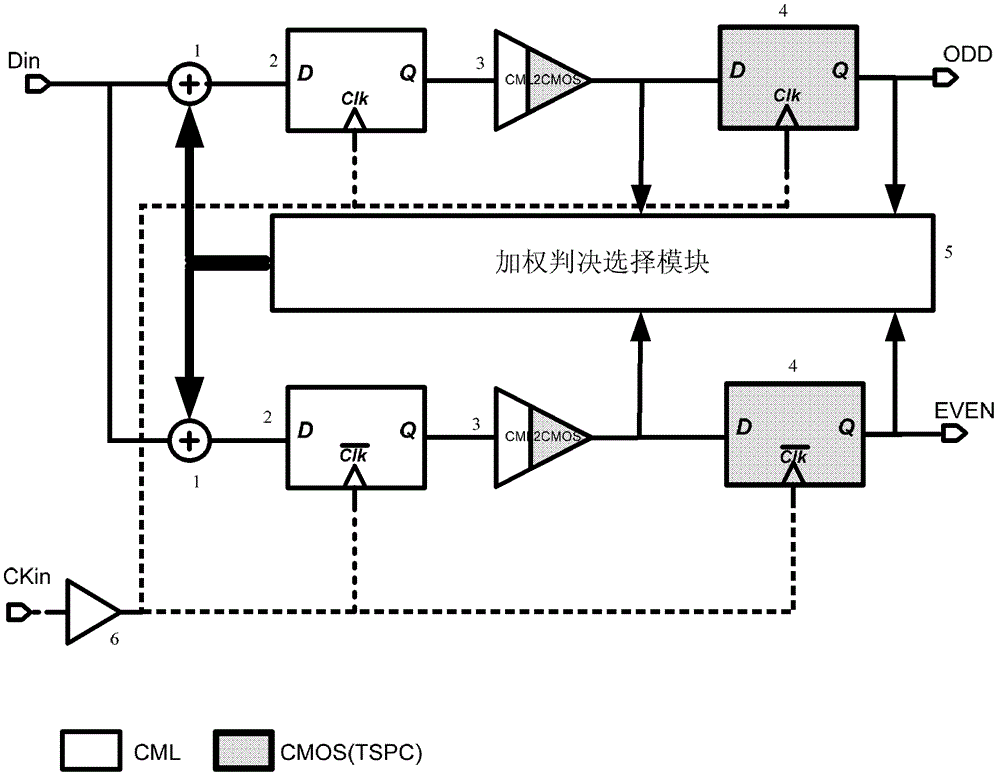

Current integrating decision feedback equalizer used in high-speed serial interface

InactiveCN102801667AEasy to handleSimple structureEnergy efficient ICTTransmitter/receiver shaping networksFeedback controlHigh-Speed Serial Interface

The invention discloses a current integrating decision feedback equalizer used in a high-speed serial interface, belonging to the field of integrated circuits. The current integrating decision feedback equalizer comprises two branches, wherein each branch is formed as follows: a signal input end orderly passes through an analogue weighting device, a CML(Current-Mode Logic) D trigger and a CML to CMOS (Complementary Metal Oxide Semiconductor) level switching circuit to be connected with a TSPC (True Single Phase Clock) D trigger; the input end of a weighting decision selecting module is respectively connected with the output ends of the two branches and the output ends of the CML to CMOS level switching circuits in the two branches, and the output end of the weighting decision selecting module is respectively connected with the feedback control ends of the analogue weighting devices in the two branches; the output end of one input clock buffer module is respectively connected with the clock control input ends of the CML D triggers and the clock control input ends of the TSPC D triggers in the two branches; and the clock signal of the input clock buffer module is an anti-phase half-speed differential clock signal. The current integrating decision feedback equalizer has the advantages of low error rate, simple structure, low power consumption, and so on.

Owner:PEKING UNIV

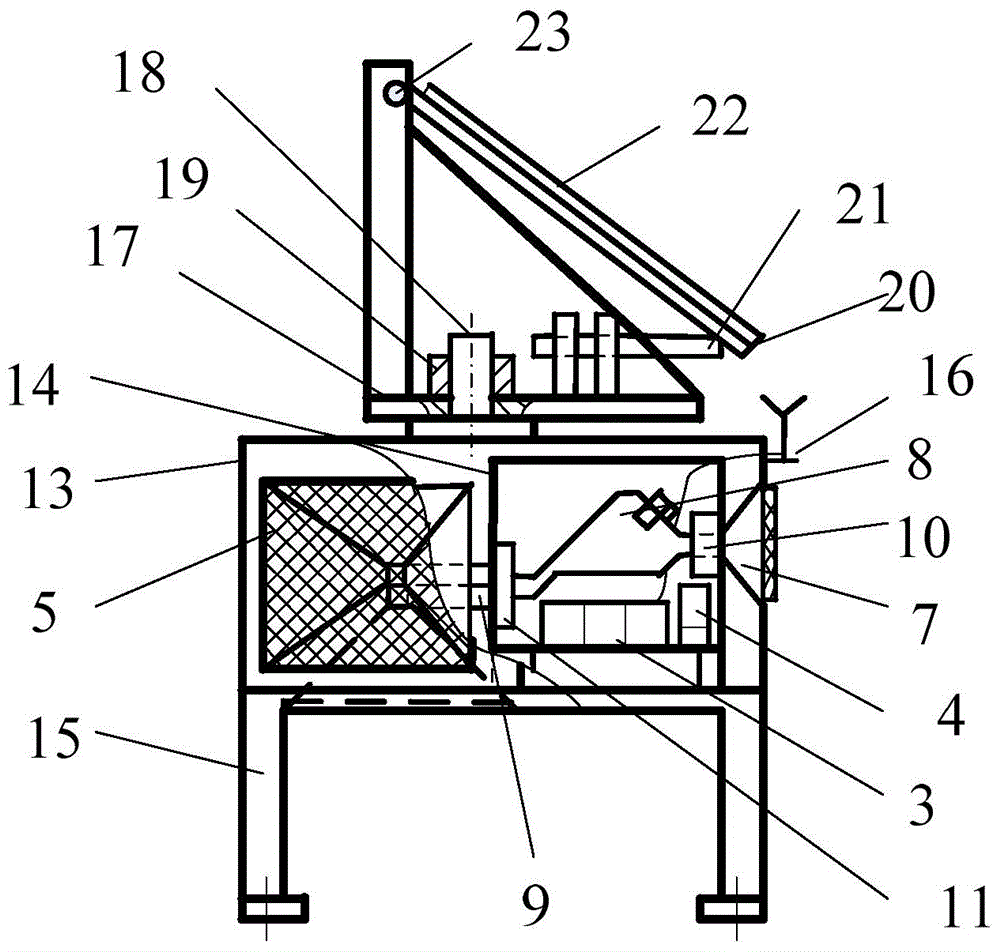

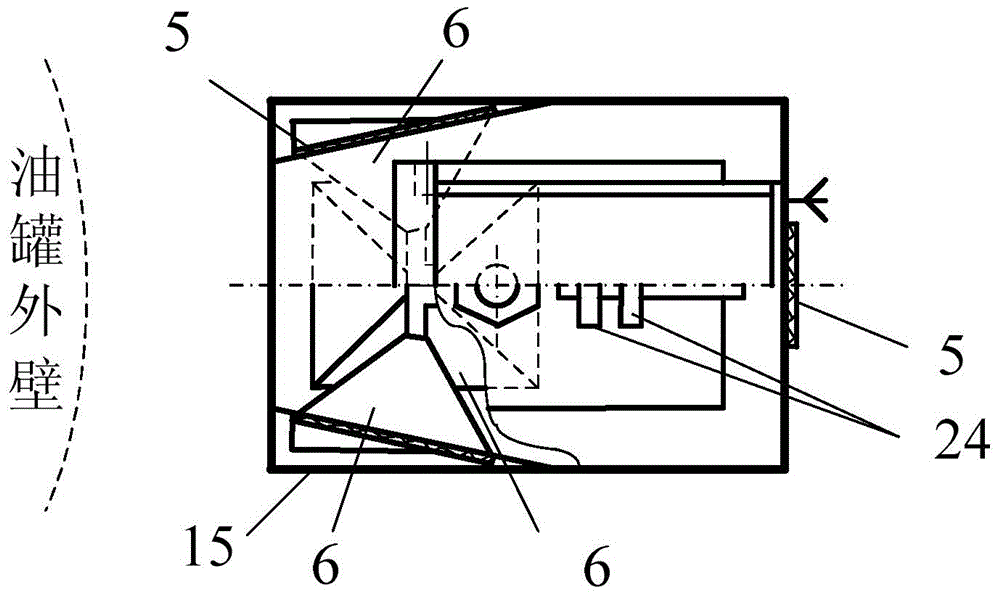

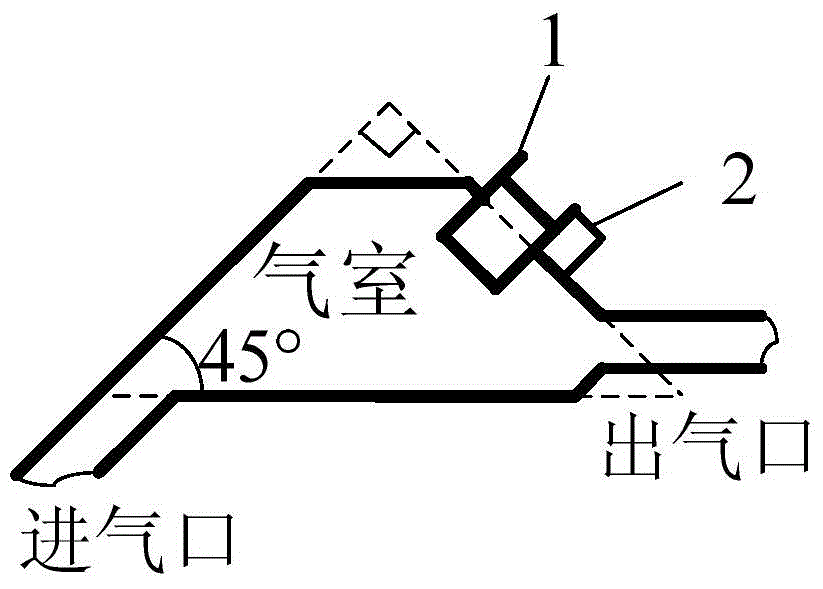

Device, system, and method for monitoring oil depot fuel leakage based on wireless sensing

InactiveCN105003829ALow power designReduce managementPipeline systemsTransmissionLow-power electronicsWireless sensor networking

The invention discloses a device, a system, and a method for monitoring oil depot fuel leakage based on wireless sensing. The device comprises a measurement and control and communication module, a gas collecting device, a mechanical structure, and a power module. The measurement and control and communication module which comprises an integrated photoionization sensor and temperature sensor combination for detecting fuel volatile gas controls the gas collecting device, and detects oil gas concentration around an oil tank periodically and sends monitoring information in a wireless manner. The system and the application method use a device as a node, and a plurality of nodes are arranged around an oil tank, so as to form a detection network. Two adjacent nodes of any node in the nodes can communicate directly, and a main node on a valve region is responsible for determining abnormal information reported by the nodes and reporting the abnormal information to a monitoring center. The device, the method, and the system are advantaged in that a wireless sensor network method is used to monitor oil depot fuel leakage online and give out alarm, power of the device is supplied by a cell charged by solar energy, the device is designed and managed in low power consumption and low operating voltage, and is designed to be sealed, so as to achieve operation requirement of safe, reliable, and energy-saving.

Owner:CENT SOUTH UNIV

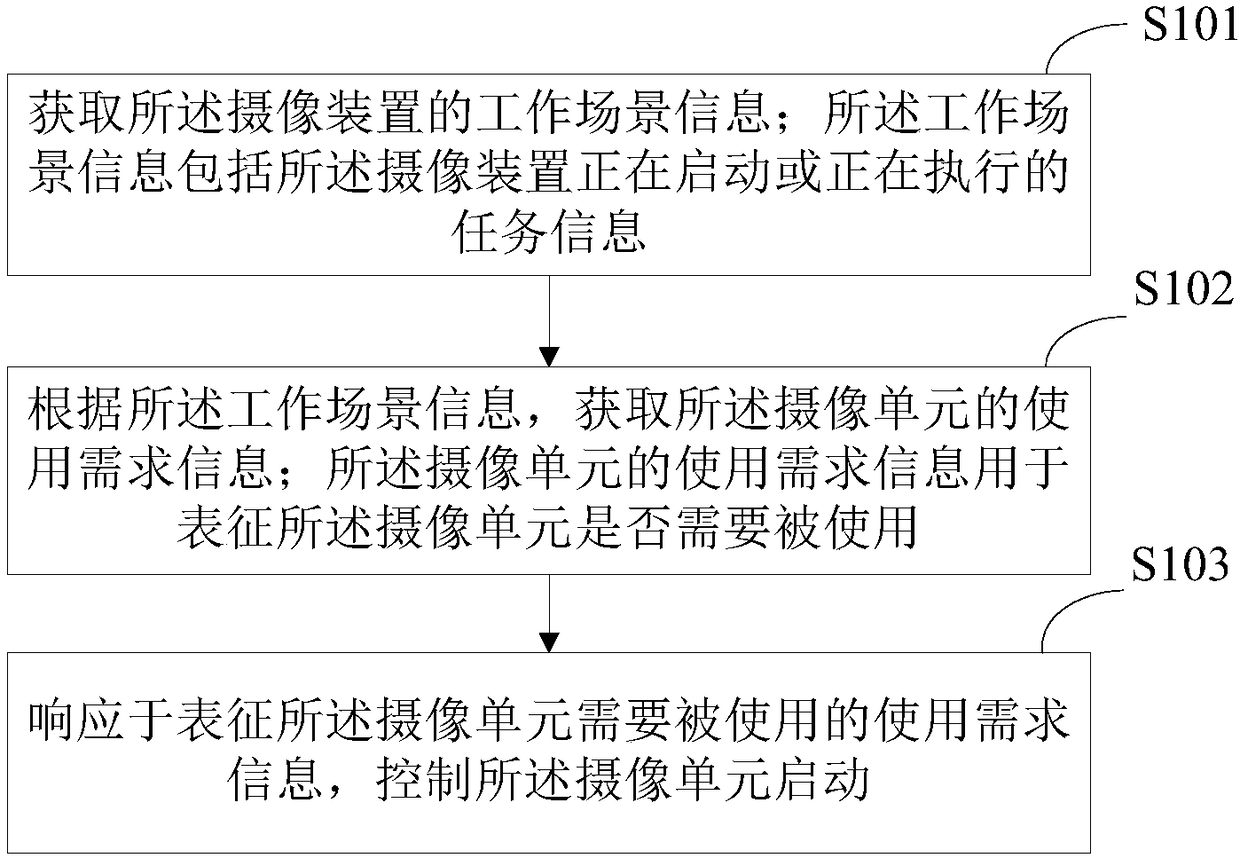

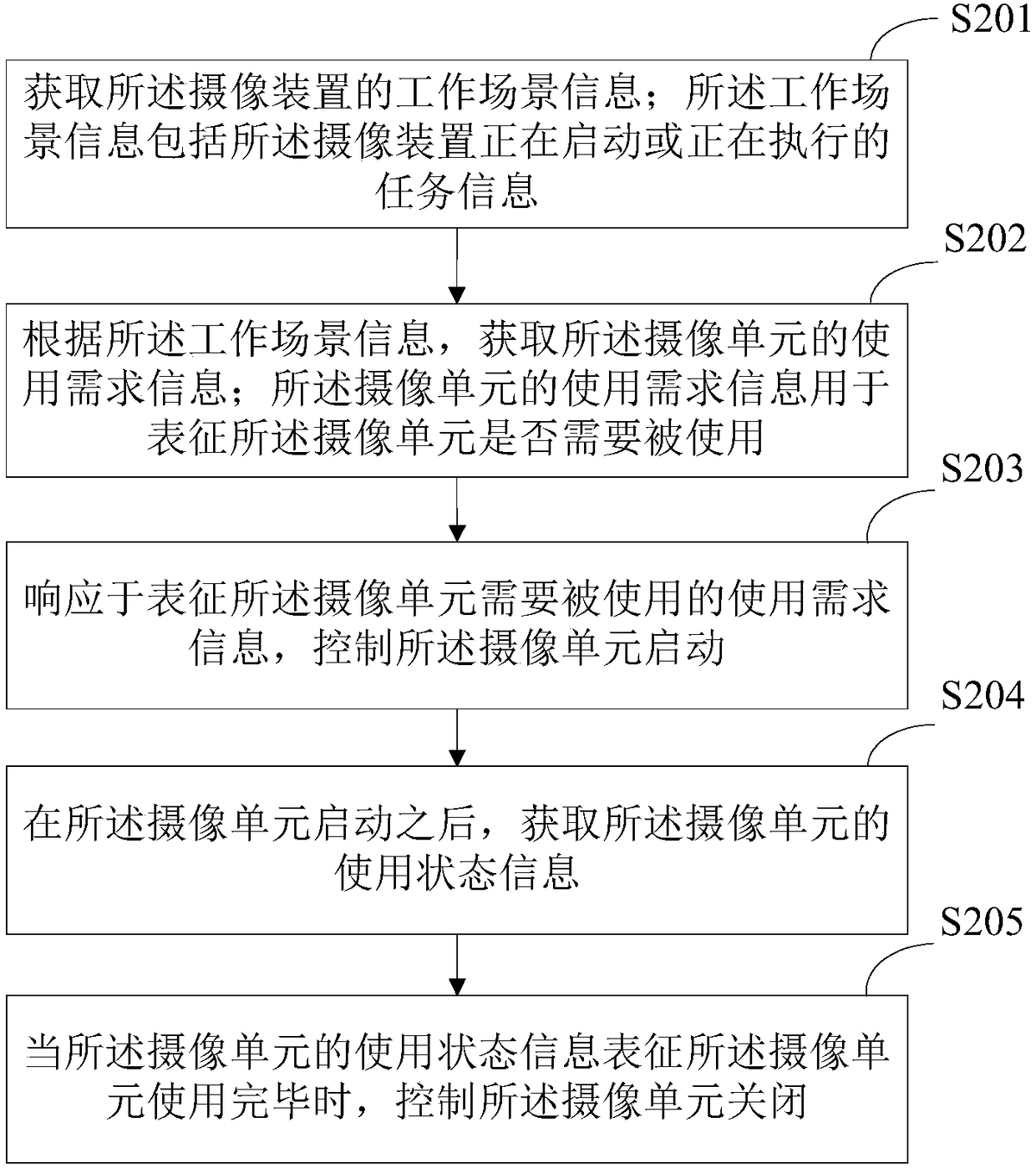

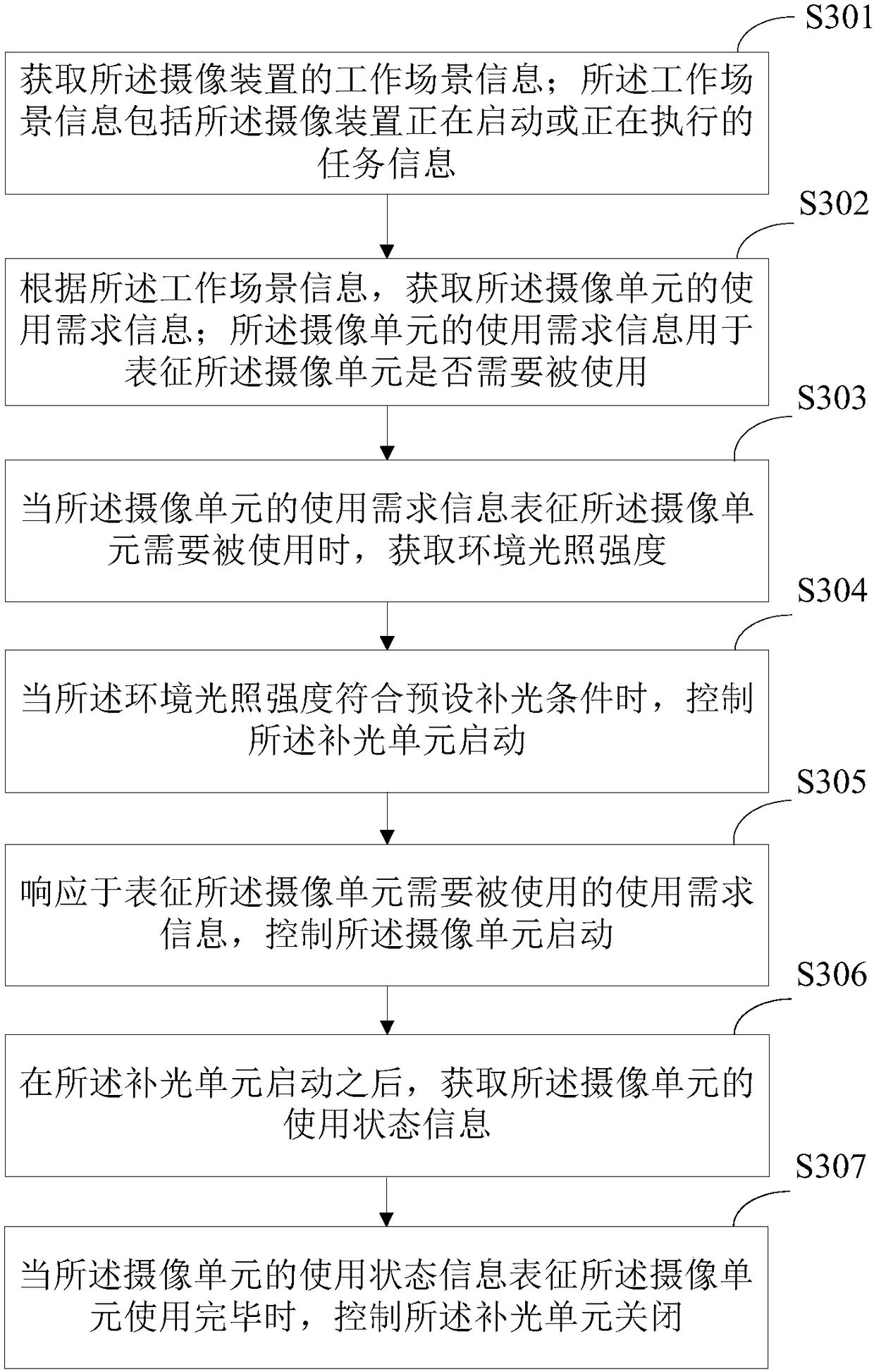

Power dissipation control method and camera device

ActiveCN108156388ALower power consumption levelsImprove power consumption control effectTelevision system detailsColor television detailsComputer visionPower consumption

The invention provides a power dissipation control method and a camera device. A camera unit in a camera device is under a closing state after starting the camera device. The method includes steps ofacquiring working scene information of the camera device; according to the working scene information, acquiring using demand information of the camera unit; when the using demand information of the camera unit represents that the camera unit is required to be used, controlling the startup of the camera unit. The camera unit only can be started under the working scene required to use, otherwise, the original closing state can be kept; thus the method effectively avoids the unnecessary power dissipation loss caused by starting the camera unit when the camera unit is not required to use, and further reduces the power dissipation level of the camera unit and improves the power dissipation control effect.

Owner:YUNDING NETWORK TECH BEIJING

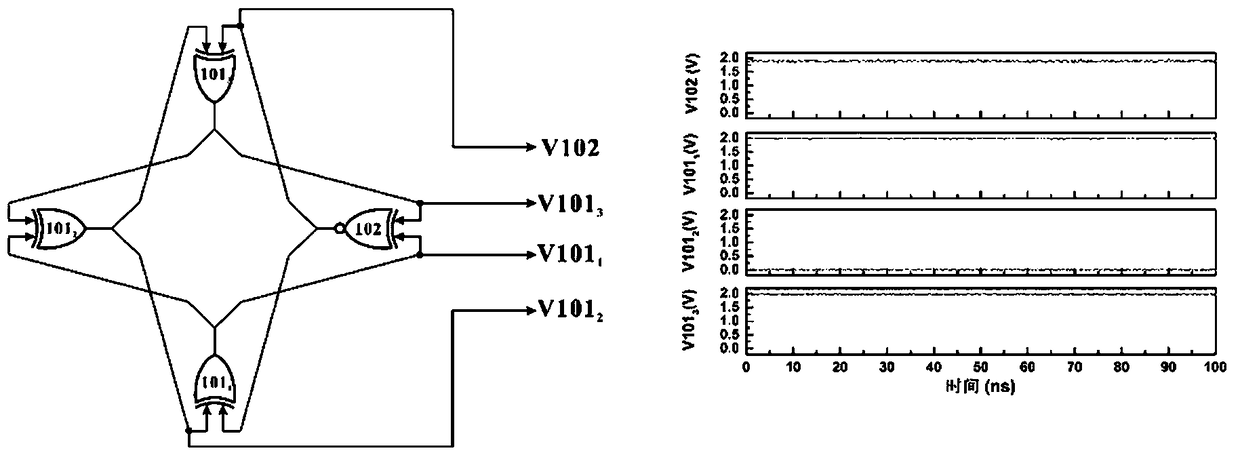

True random number generation method and device with detection and correction function

ActiveCN108717353AQuality improvementIncrease randomnessRandom number generatorsFrequency spectrumCryptosystem

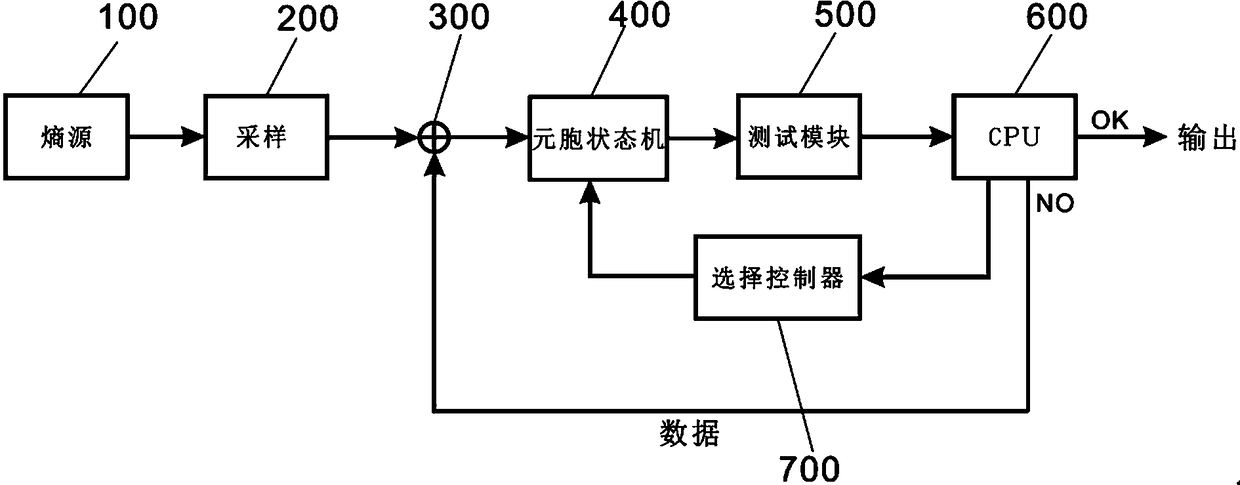

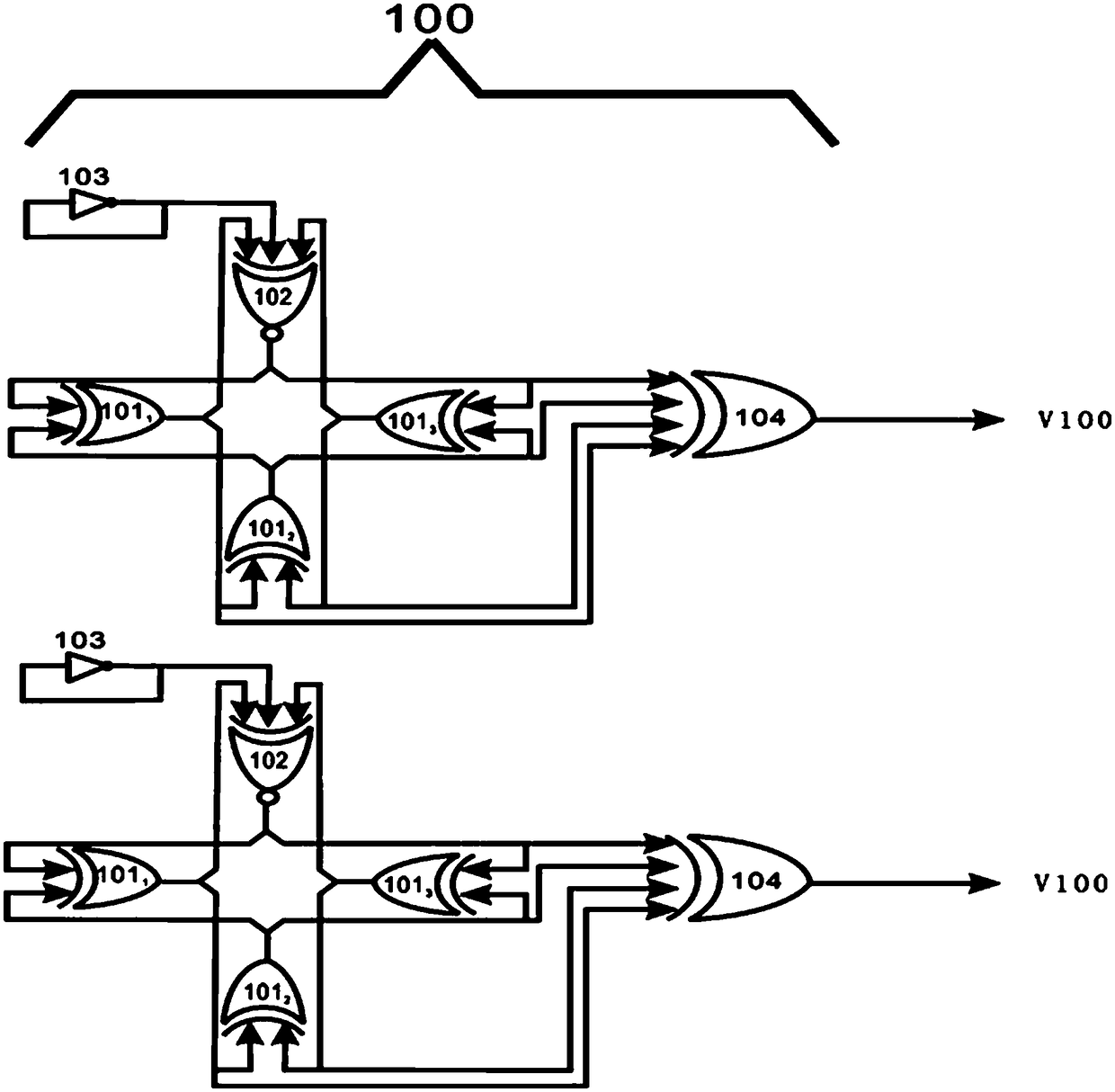

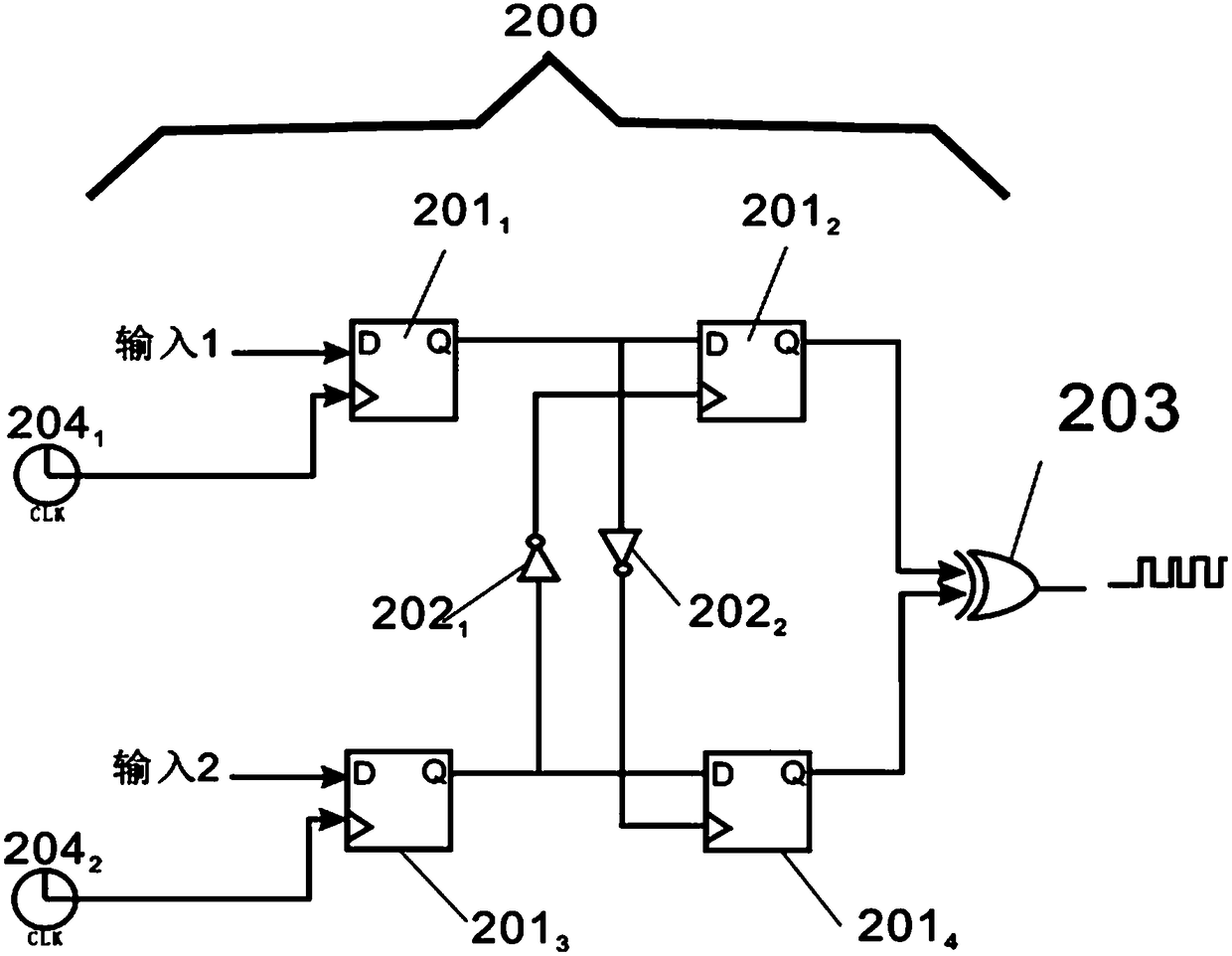

The invention discloses a true random number generation method and device with a detection and correction function. A random number is taken as an important component of a cryptosystem and is widely applied to a security system. The random number comprises a session key, an initial vector and a digital signature. The device is composed of an entropy source module, a sampling module, an XOR logic gate, a cellular finite state machine, a test module, a CPU and a selection controller. The entropy source module is composed of two identical oscillator structures. Each oscillator is a chaotic oscillator structure based on an autonomous Boolean network. The entropy source module can generate wide spectrum and high bandwidth chaotic signals. After a random sequence is tested through the test module, whether the sequence passes the test or not is judged through the CPU. The sequence is directly output if the sequence passes the test. Data is returned and enters a postprocessing module through an XOR circuit if the sequence does not pass the test. Moreover, a selection controller selects different postprocessing modes to process the data. The processed data enters the test module for test again, until the data passes the test. A random code sequence generated by the invention can pass a random number industry standard test.

Owner:TAIYUAN UNIV OF TECH

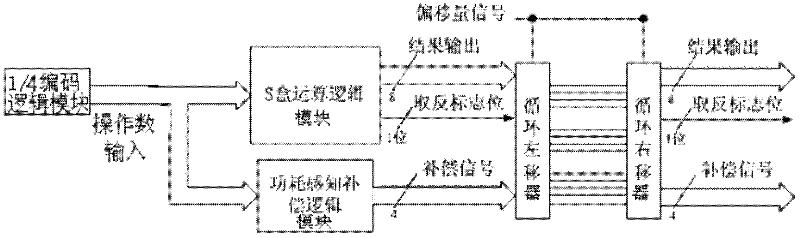

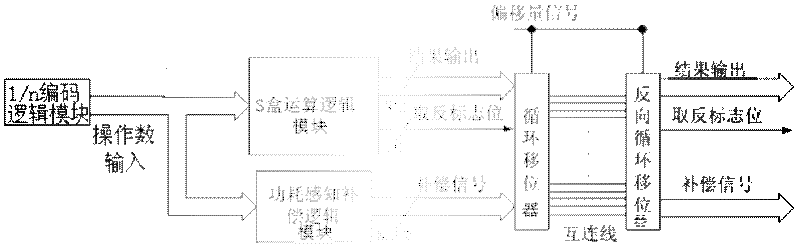

Power-aware power balancing S box unit circuit and application method thereof

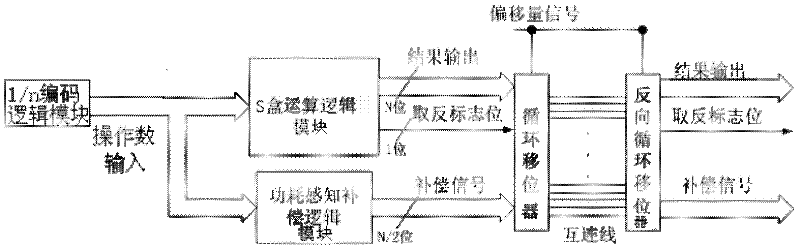

ActiveCN102509145AReduce power overheadLower power consumption levelsEncryption apparatus with shift registers/memoriesRecord carriers used with machinesComputer modulePower balancing

The invention discloses a power-aware power balancing S box unit circuit and an application method thereof, belonging to the technical field of power attack resistance. The power-aware power balancing S box unit circuit comprises an S box arithmetic logic module, a power-aware compensation logic module, a cycling shifter and a backcycling shifter, wherein the S box arithmetic logic module and the power-aware compensation logic module are simultaneously driven by an operand input port, and the S box arithmetic logic module calculates output values at a result output port and output values at a negative flag bit output port in accordance with input data; and the power-aware compensation logic module calculates output values at a compensation signal output port in accordance with the input data. The invention reduces the power consumption of power balancing, and provides the implementation of equivalent load balancing of multiple data lines in a random exchange interconnection line manner for the load balancing problem of the multiple data lines.

Owner:TSINGHUA UNIV

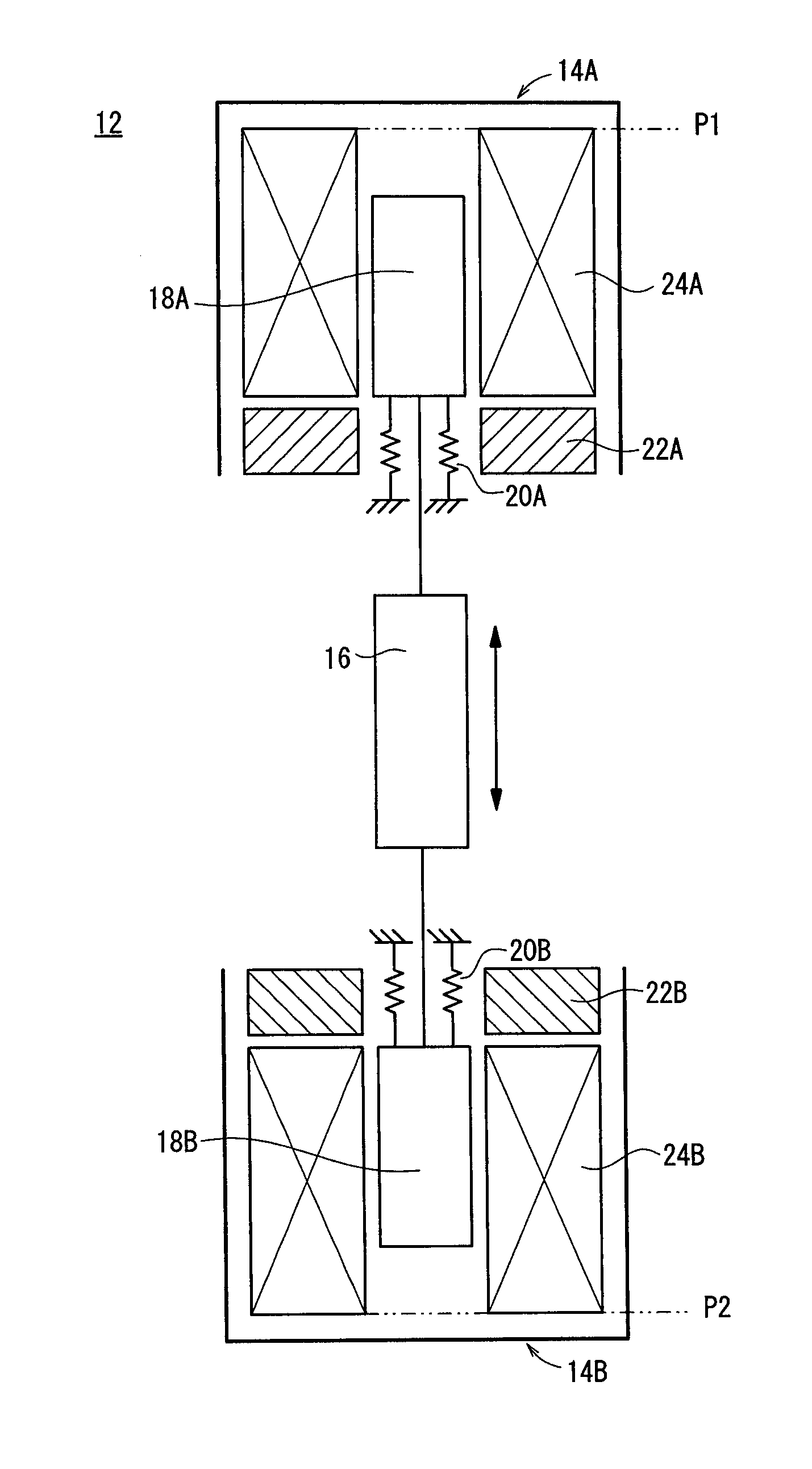

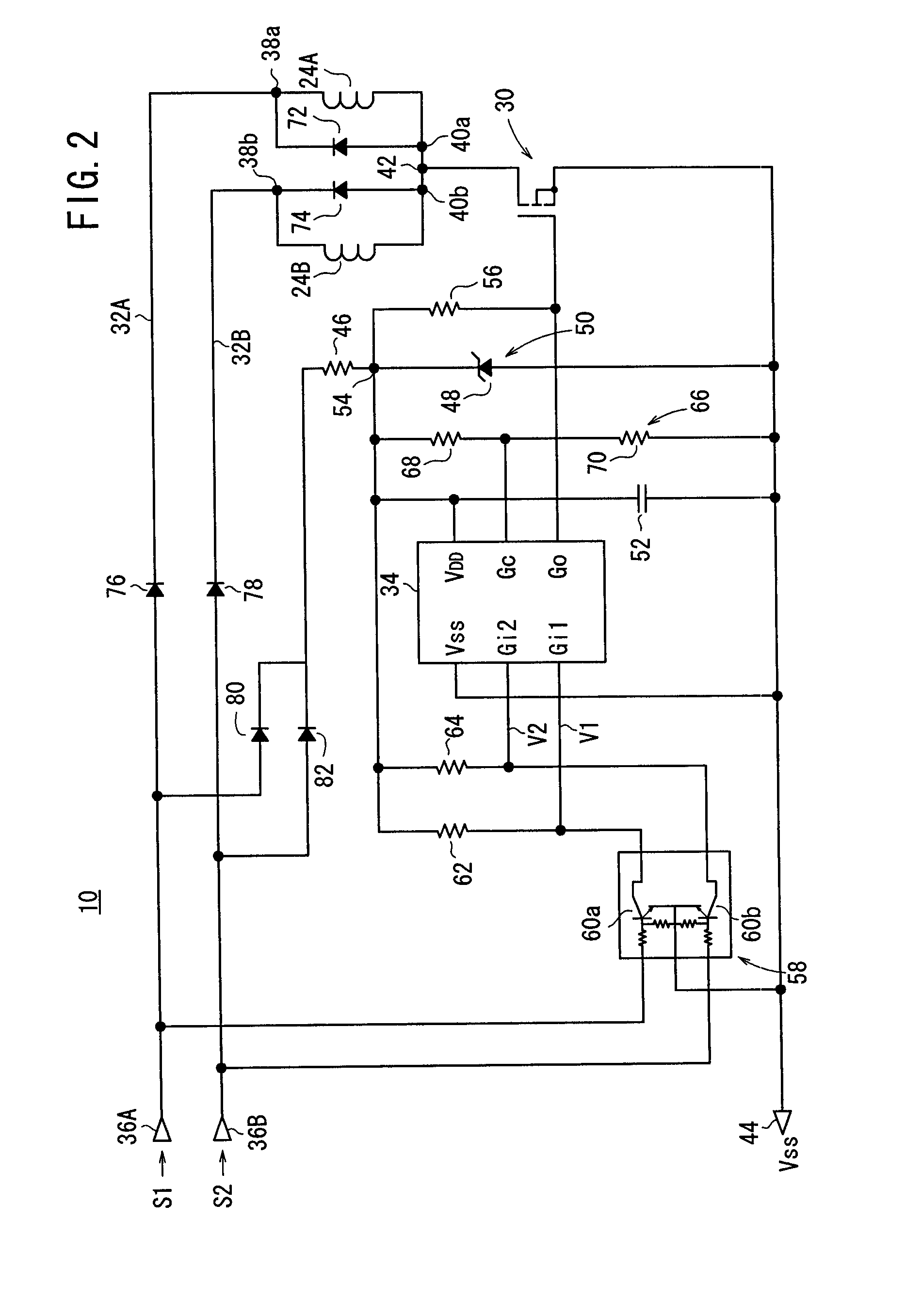

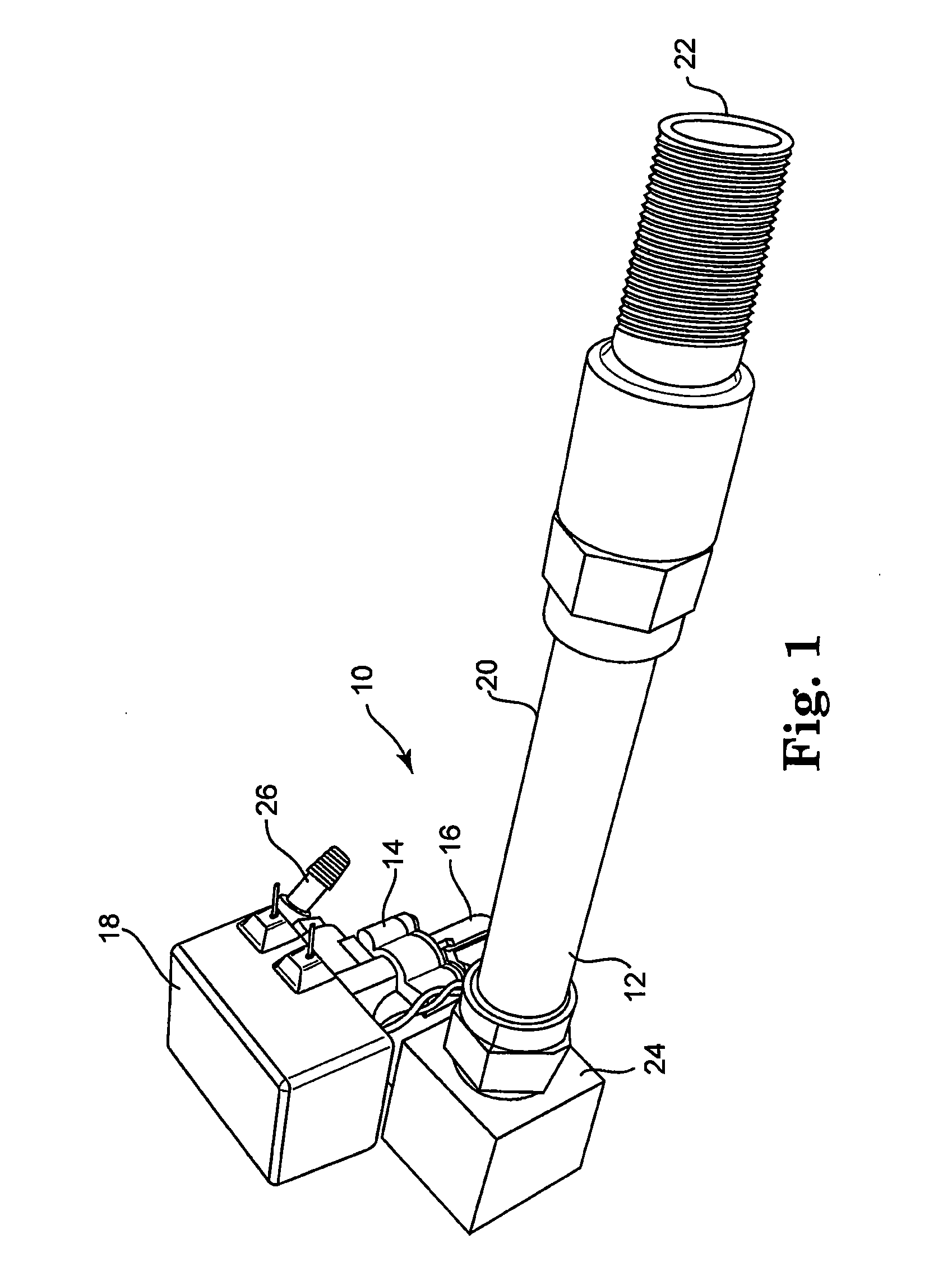

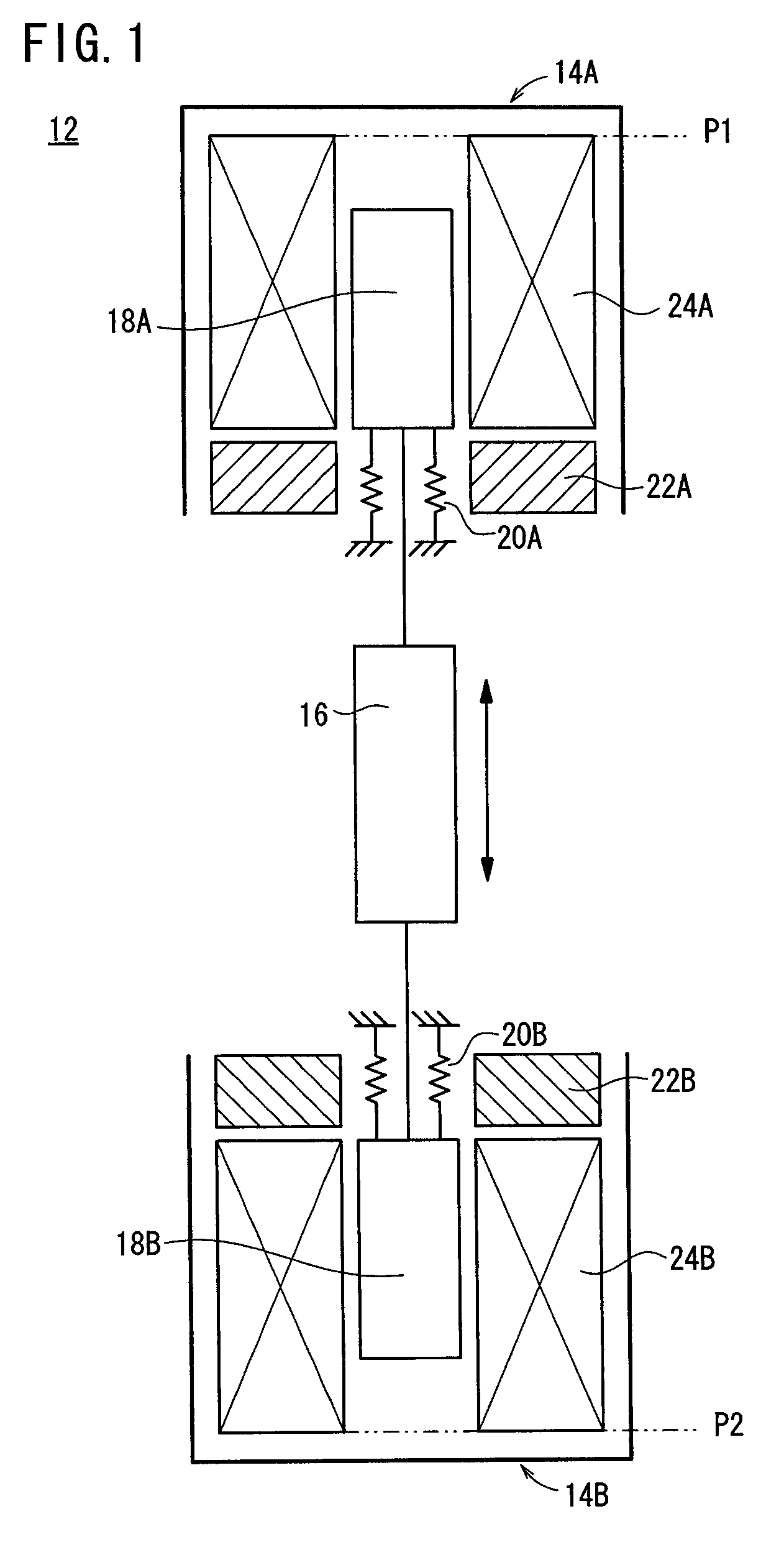

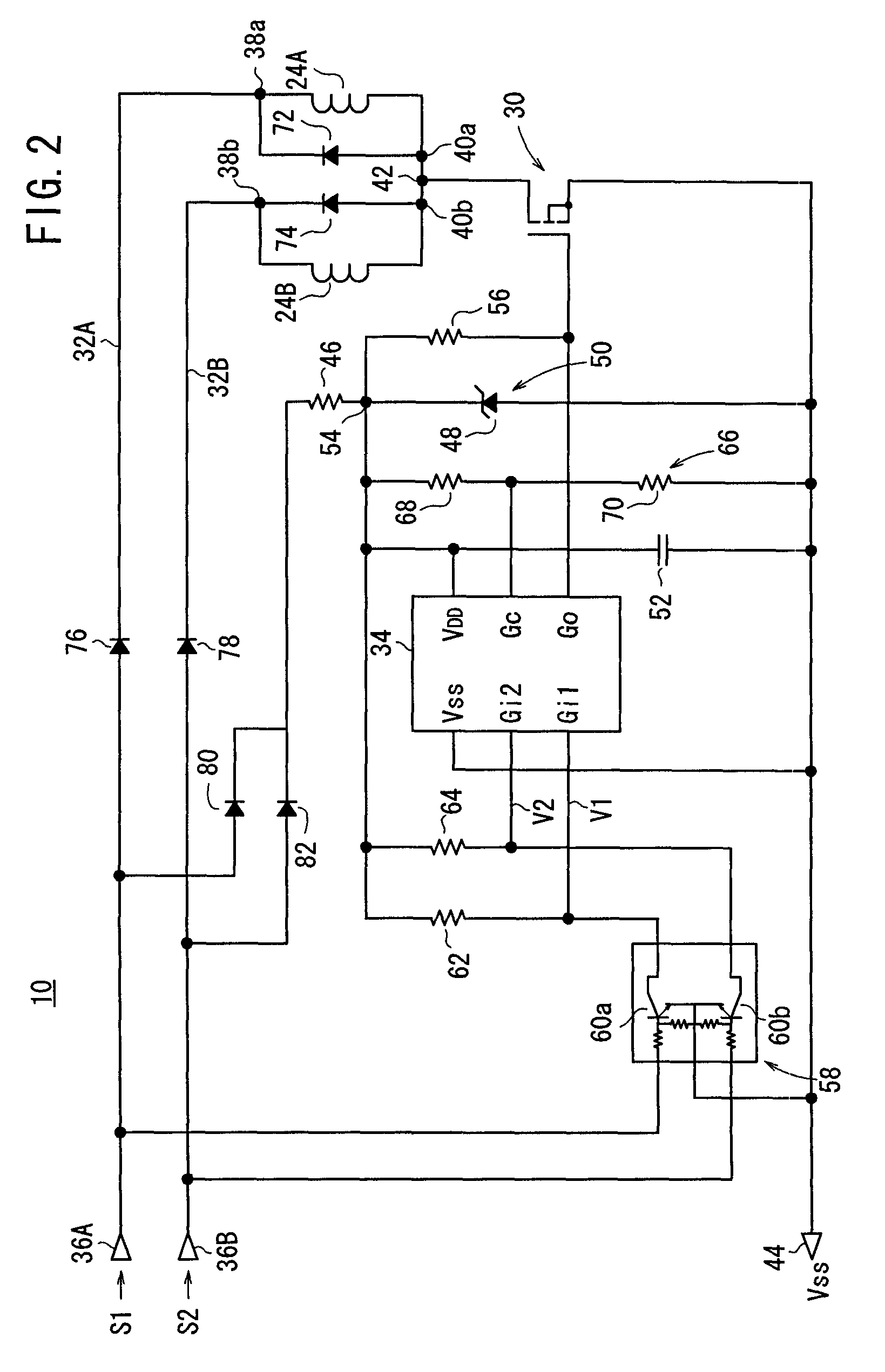

Solenoid-Operated Valve Controller

ActiveUS20070145316A1Small sizeReduce spacingOperating means/releasing devices for valvesElectric switchesSolenoid valveElectromagnetic coil

A solenoid-operated valve controller includes a first signal line and a second signal line, which are connected respectively to ends of a first solenoid coil and a second solenoid coil. The first solenoid coil and the second solenoid coil have other ends, which are electrically connected in common to a switch. One of the first and second solenoid coils, which corresponds to signal states of a plurality of input signals that are supplied respectively to the first and second signal lines, is selected, and the switch is turned on and off to control the selected one of the first and second solenoid coils.

Owner:SMC CORP

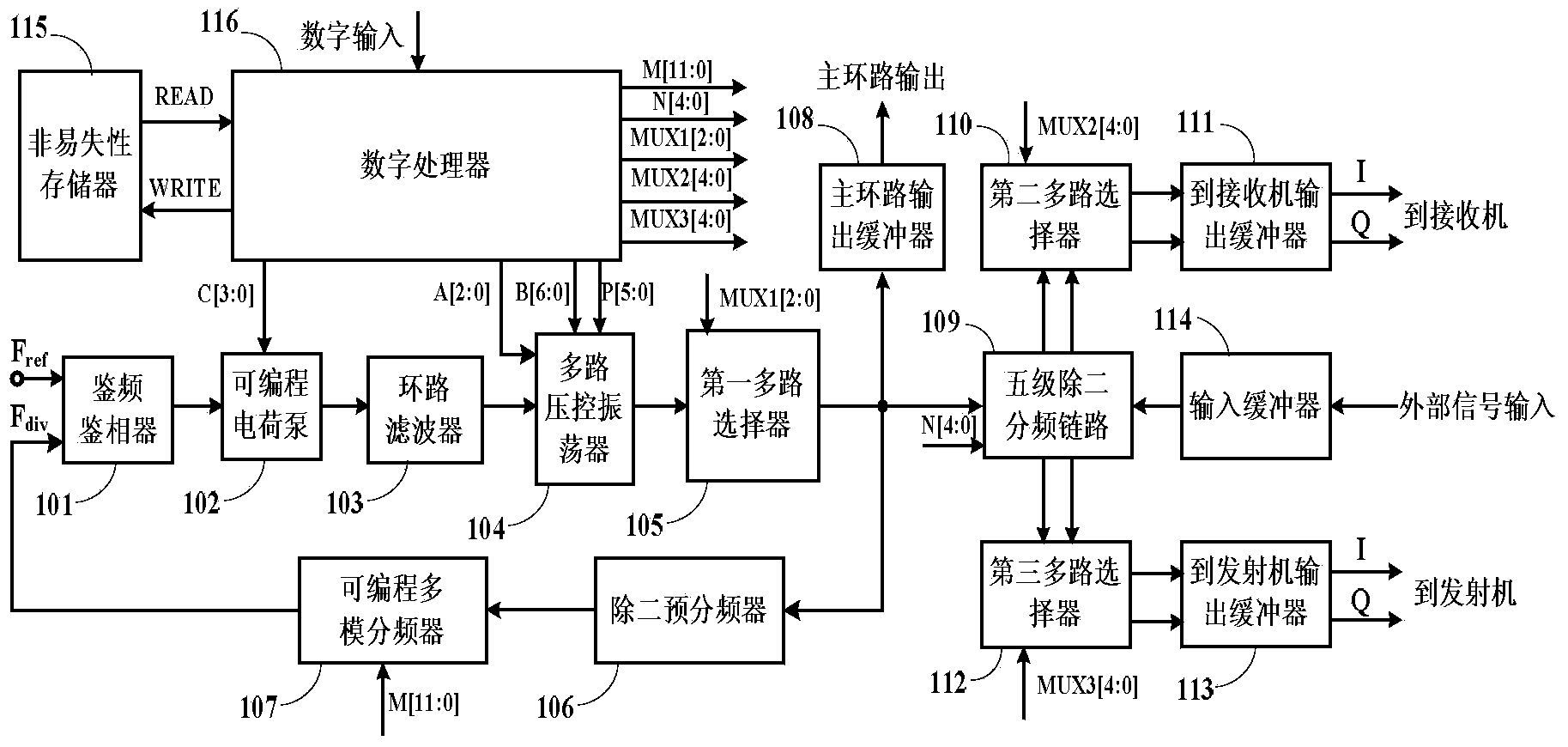

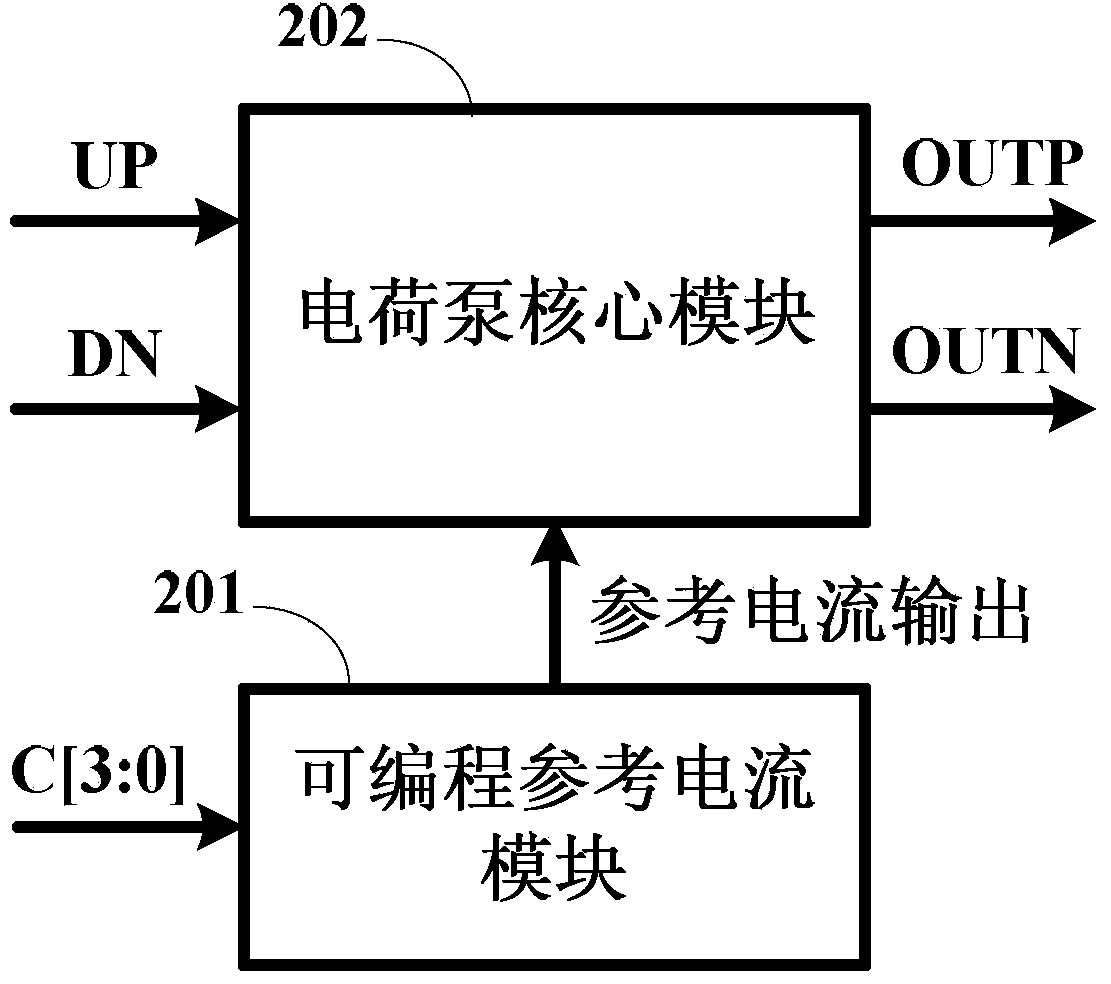

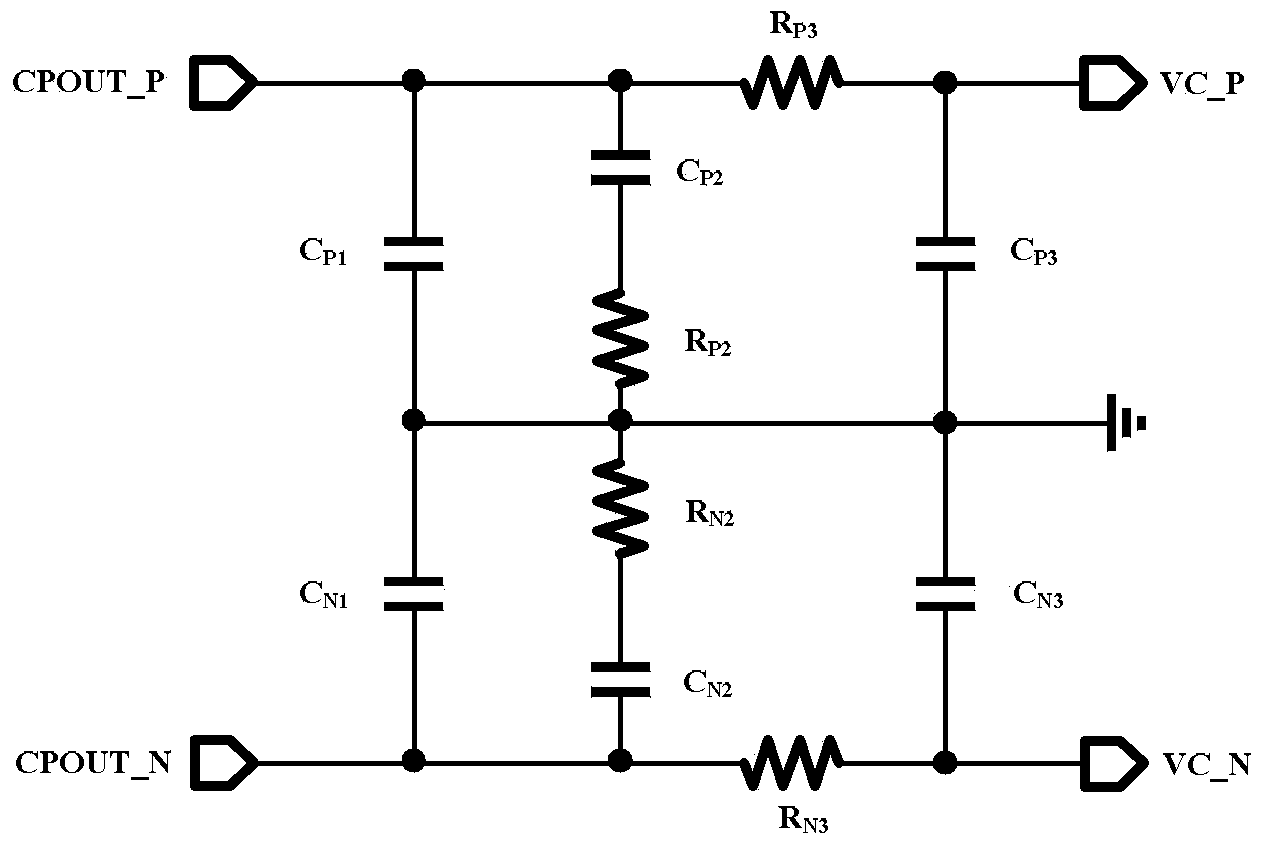

Multi-standard performance-reconfigurable I/Q carrier generator

ActiveCN104079315ARealize automatic adjustmentLow cost requirementsPulse automatic controlTransmissionLoop filterDifferential signaling

The invention discloses a multi-standard performance-reconfigurable I / Q carrier generator. Through reasonable frequency allocation, the generator can output I / Q carriers continuously covering the range from 0.1 GHz to 5 GHz and output differential signals continuously covering the range from 5 GHz to 10 GHz and the range from 1.5 GHz to 3 GHz; meanwhile, by arranging a programmable charge pump (102), a loop filter (103), a multi-path voltage-controlled oscillator (104), a first multiplexer (105) corresponding to the multi-path voltage-controlled oscillator (104), a five-stage two divided-frequency link (109), a second multiplexer (110) corresponding to the five-stage two divided-frequency link (109) and a third multiplexer (112), carrier signals of various frequencies with different loop bandwidths, different levels of phase noise, different power consumption levels and different locking times can be generated, and thus multi-standard performance-reconfigurable I / Q carriers can be generated.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

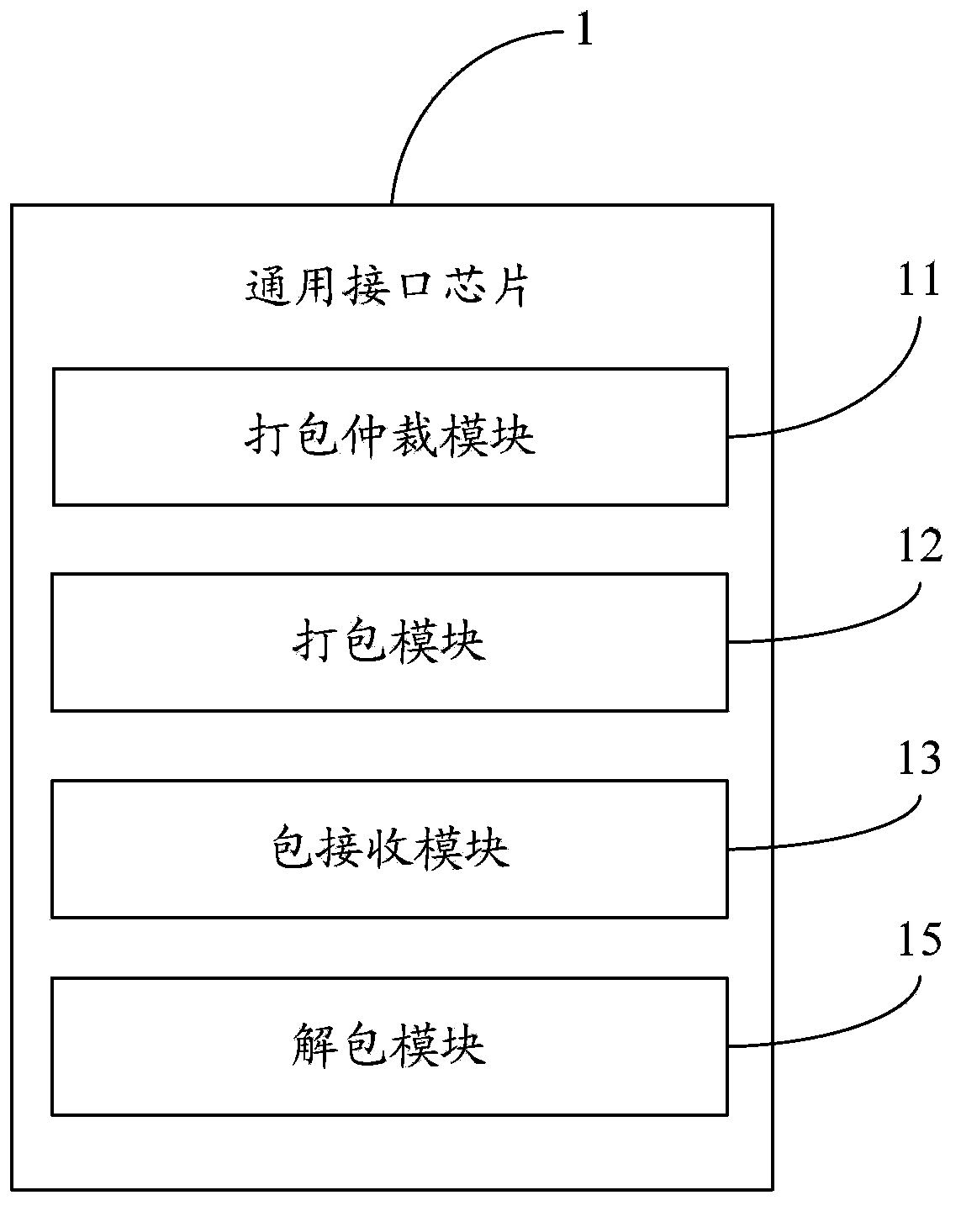

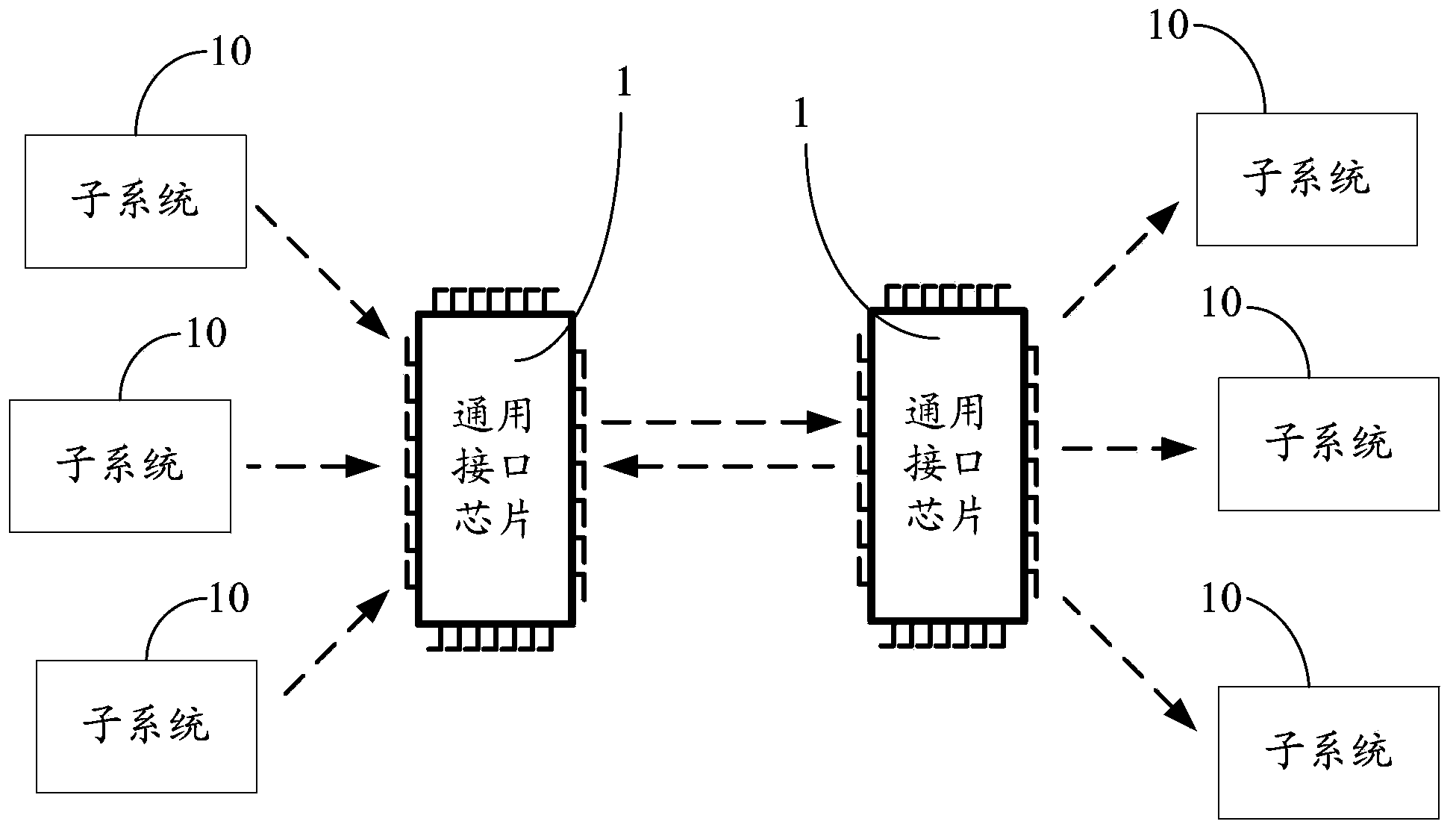

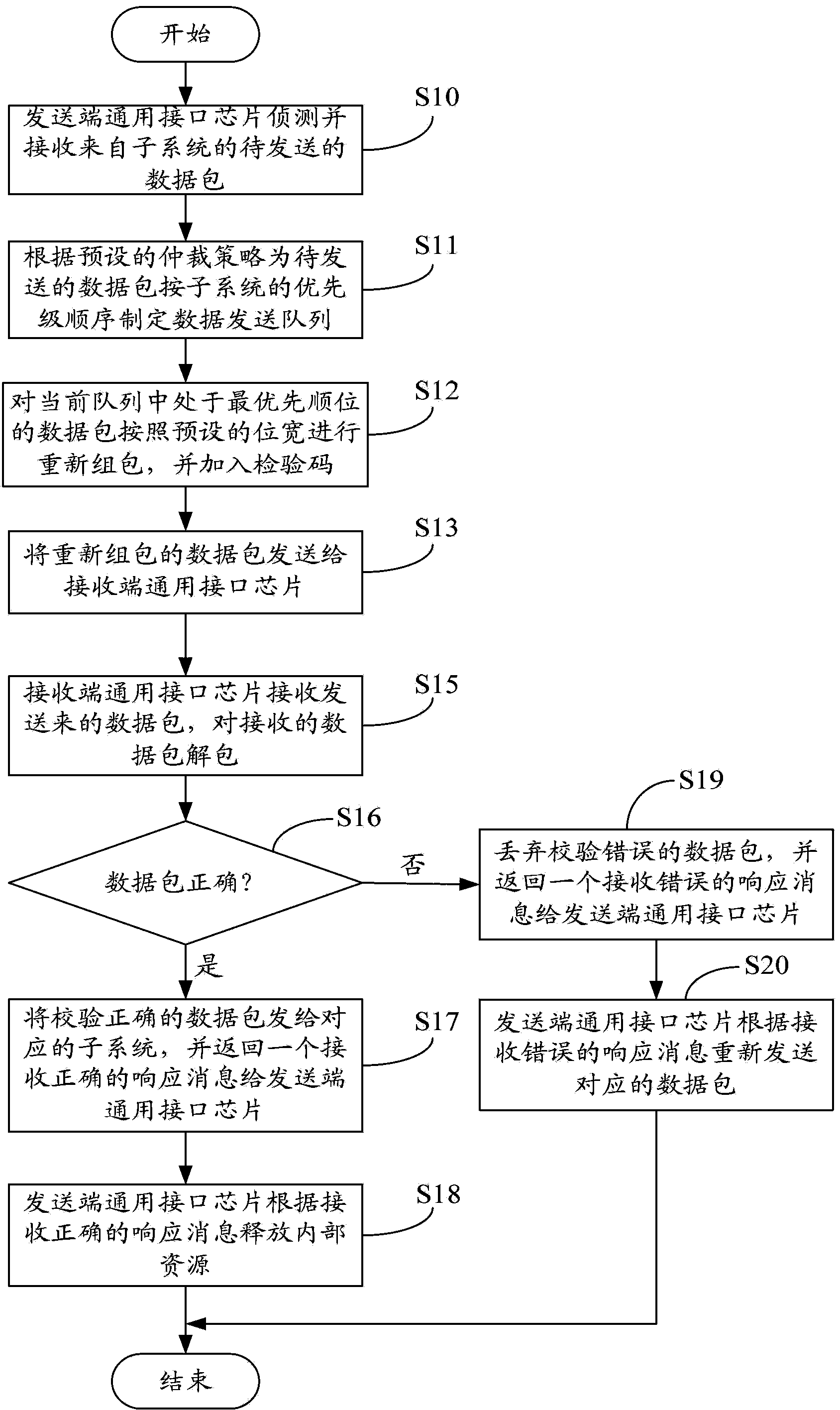

Method for achieving high-speed data transmission and universal interface chip

ActiveCN103838691AReduced complexity and power consumption levelsGuaranteed speed and qualityEnergy efficient ICTTransmissionData transmissionData exchange

The invention provides a method for achieving high-speed data transmission. According to the method, the preset bit wide is utilized to package a data packet to be transmitted again, checking codes are added into the data packet, system resources are released at once with regard to correct response information, the data packet is automatically retransmitted with regard to wrong response information, therefore, complexity and power consumption of a chip are reduced, and data exchange speed and quality are ensured. The invention further provides a universal interface chip for achieving high-speed data transmission.

Owner:SANECHIPS TECH CO LTD

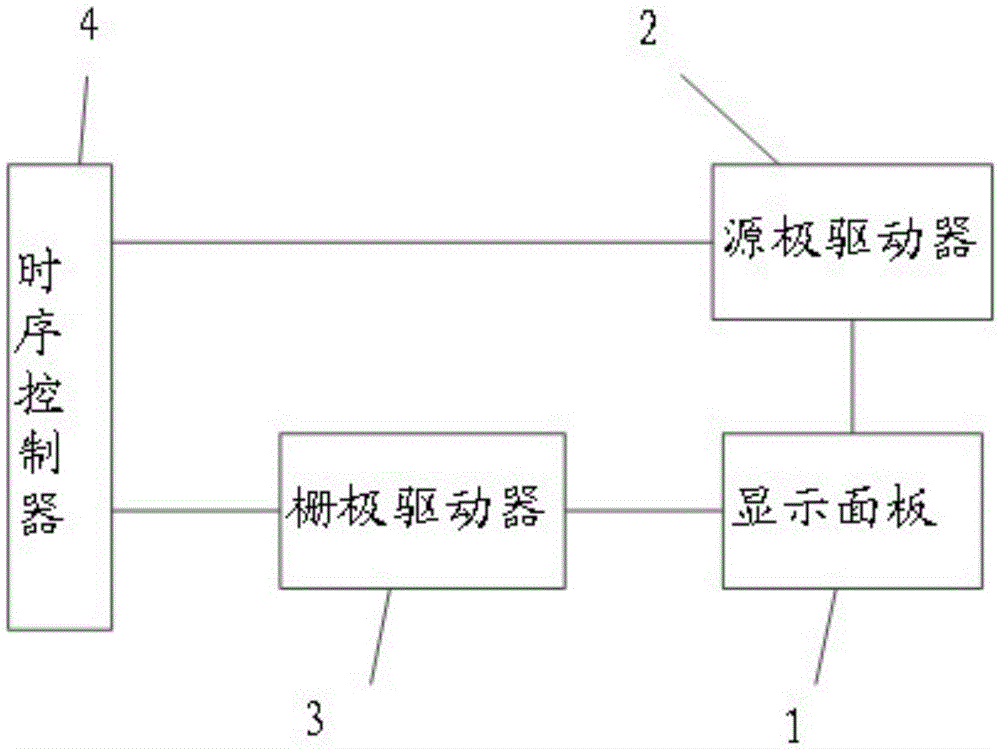

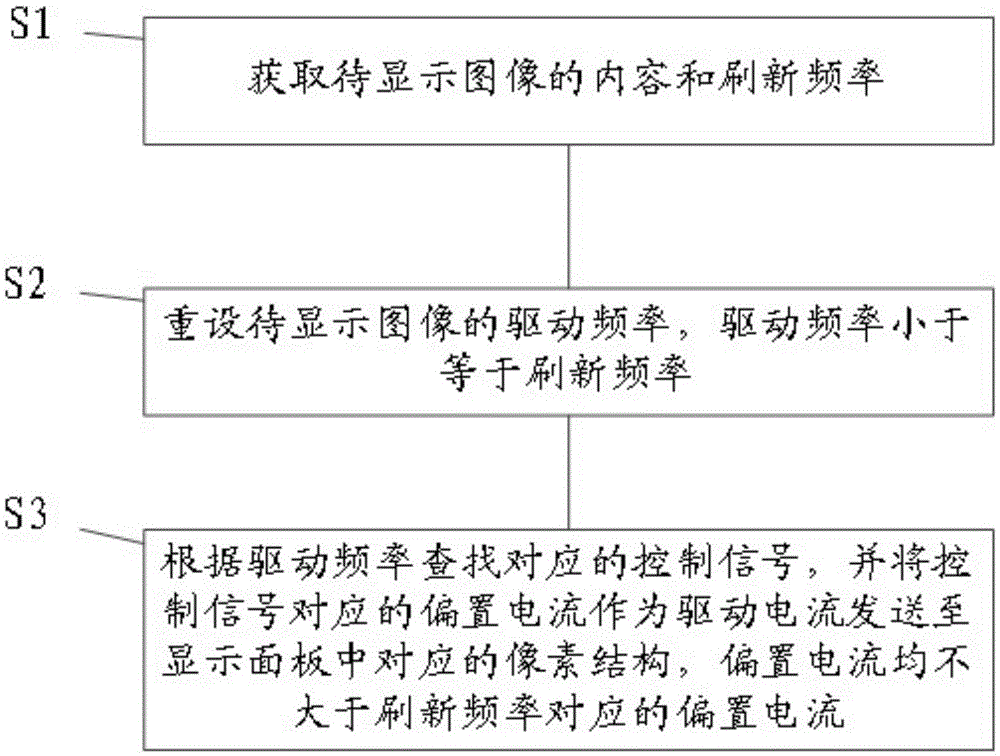

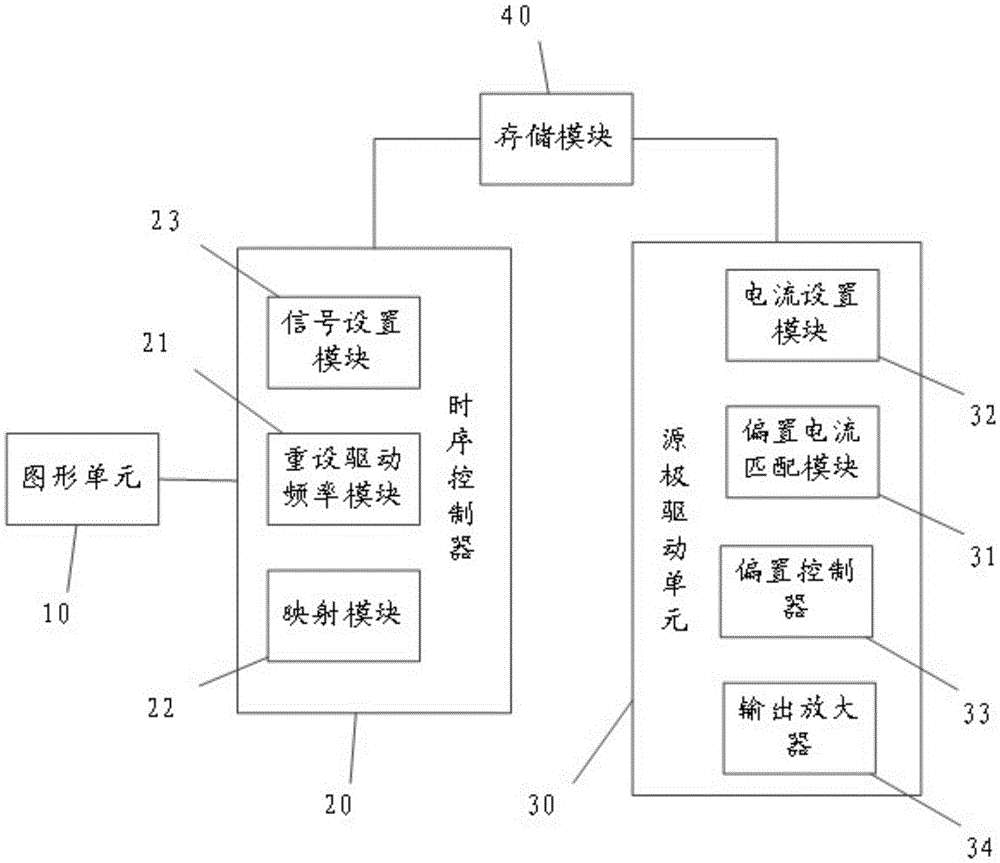

Driving method of display panel, driving circuit and display device

InactiveCN105679273AReduce power consumptionLower power consumption levelsStatic indicating devicesDriving currentControl signal

The invention provides a driving method of a display panel, a driving circuit and a display device, belongs to the technical field of display and at least partially solve the problem that the power consumption of an existing display panel is relatively large. The driving method of the display panel is used for providing driving currents for a plurality of pixel structure in the display panel and comprises the following steps of: obtaining content and a refreshing frequency of images to be displayed; resetting a driving frequency of the images to be displayed, wherein the driving frequency is smaller than or equal to the refreshing frequency; according to the driving frequency, searching for a corresponding control signal, and sending bias currents, serving as the driving currents, corresponding to the control signal to the corresponding pixel structures in the display panel, wherein the bias currents are respectively no more than a bias current corresponding to the refreshing frequency. According to the invention, when the display panel is driven by a low frequency (smaller than the refreshing frequency), the relatively small bias currents are used as the driving currents of the display panel, and the power consumption of the display panel is substantially lowered.

Owner:BOE TECH GRP CO LTD +1

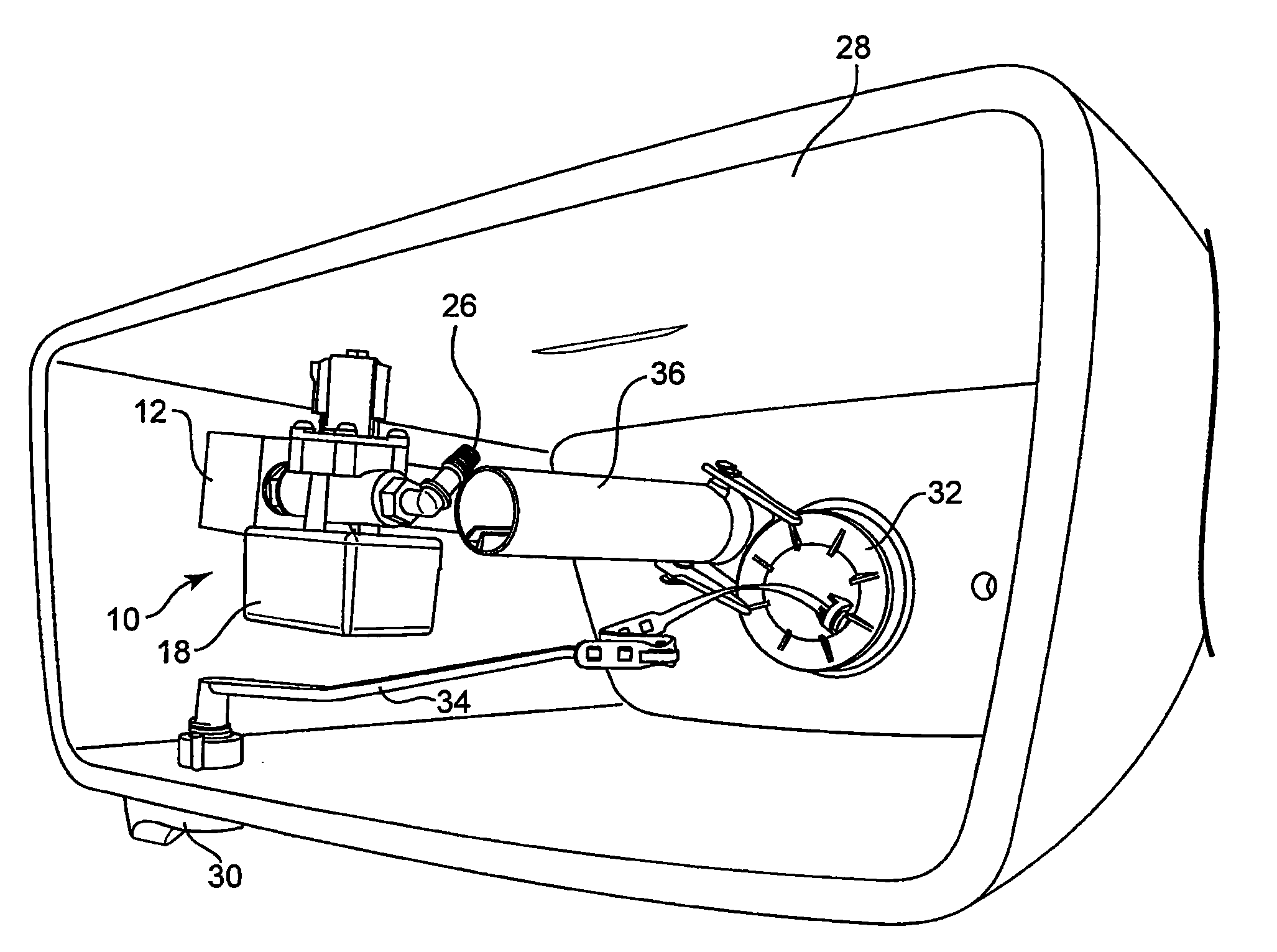

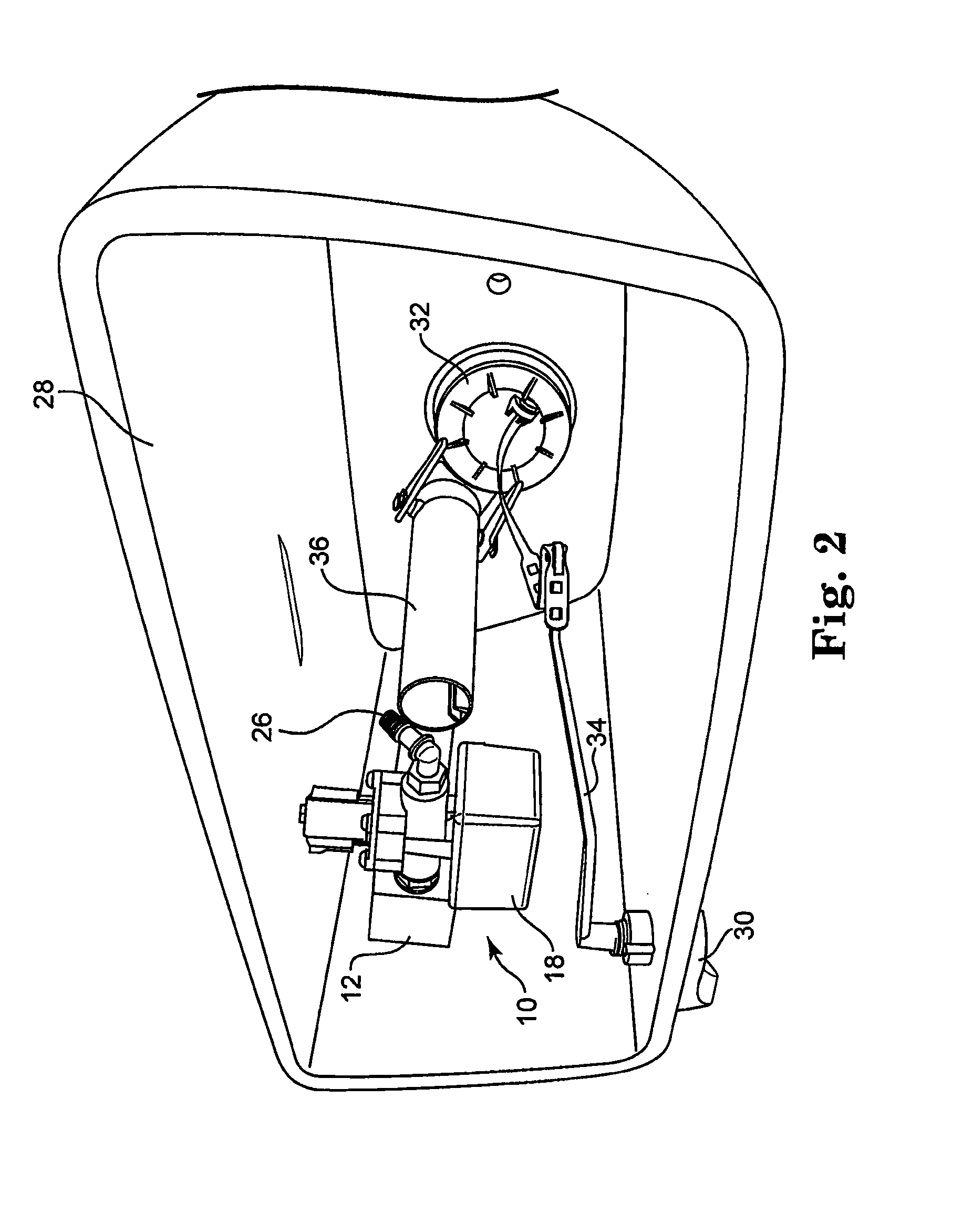

Electronic toilet tank monitor utilizing a bistable latching solenoid control circuit

InactiveUS20080209622A1Reliably water levelMinimal power requirementFlushing devicesFluid controlEngineering

A fluid control circuit system is capable of maintaining fluid within a fluid tank at a desired level using electronic sensors and control circuitry, where the control circuitry and actuators are configured for low power consumption, thus allowing operation to be powered by a self contained internal power supply. To provide appropriate fluid control, the system includes a fluid sensor indicating if fluid is at a predetermined level, control circuitry attached to the fluid sensor, a latching solenoid attached to the control circuitry and also attached to a fluid control valve, and an internal power supply to power all electrical components.

Owner:WOOD KURT E +1

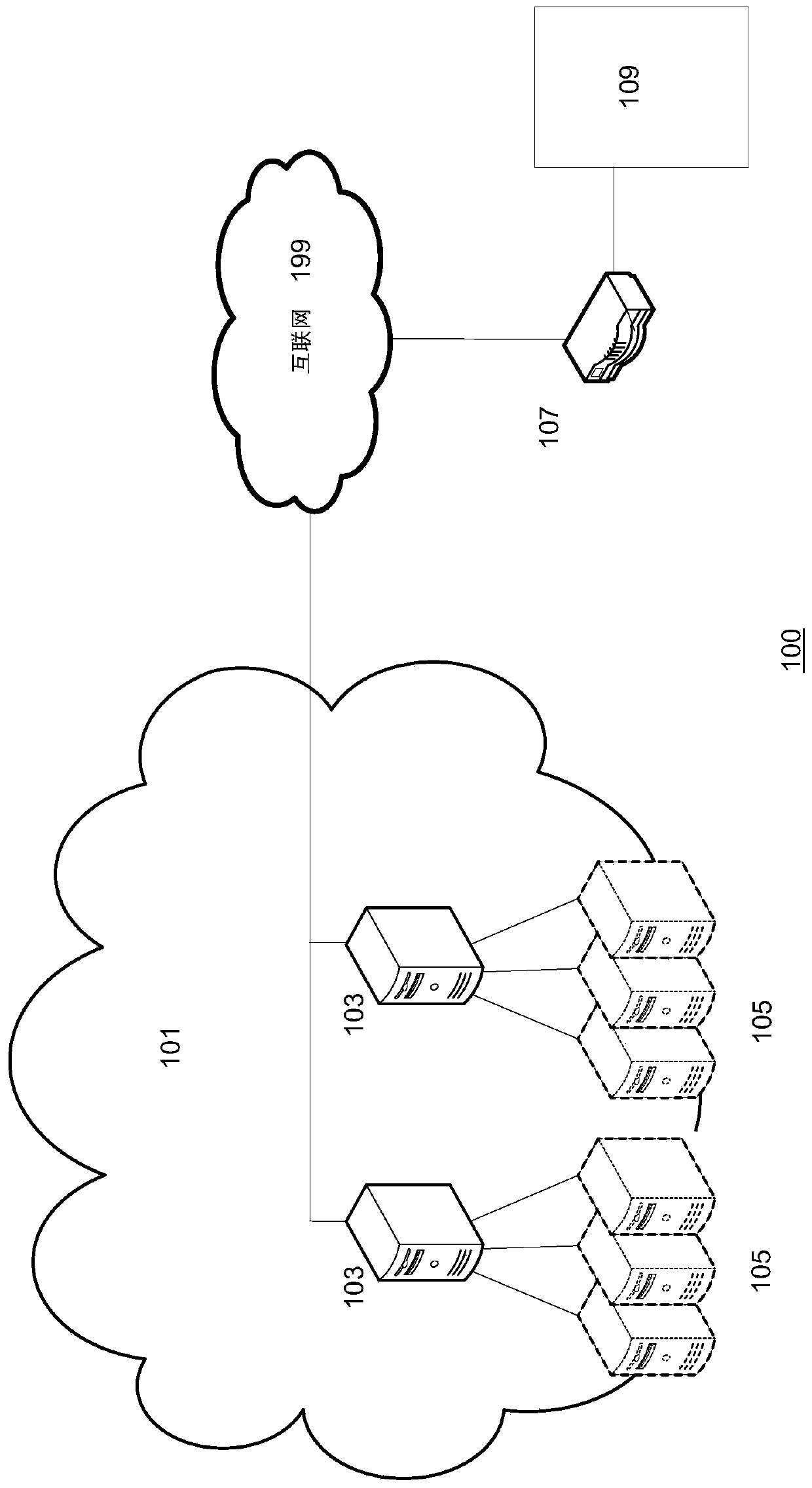

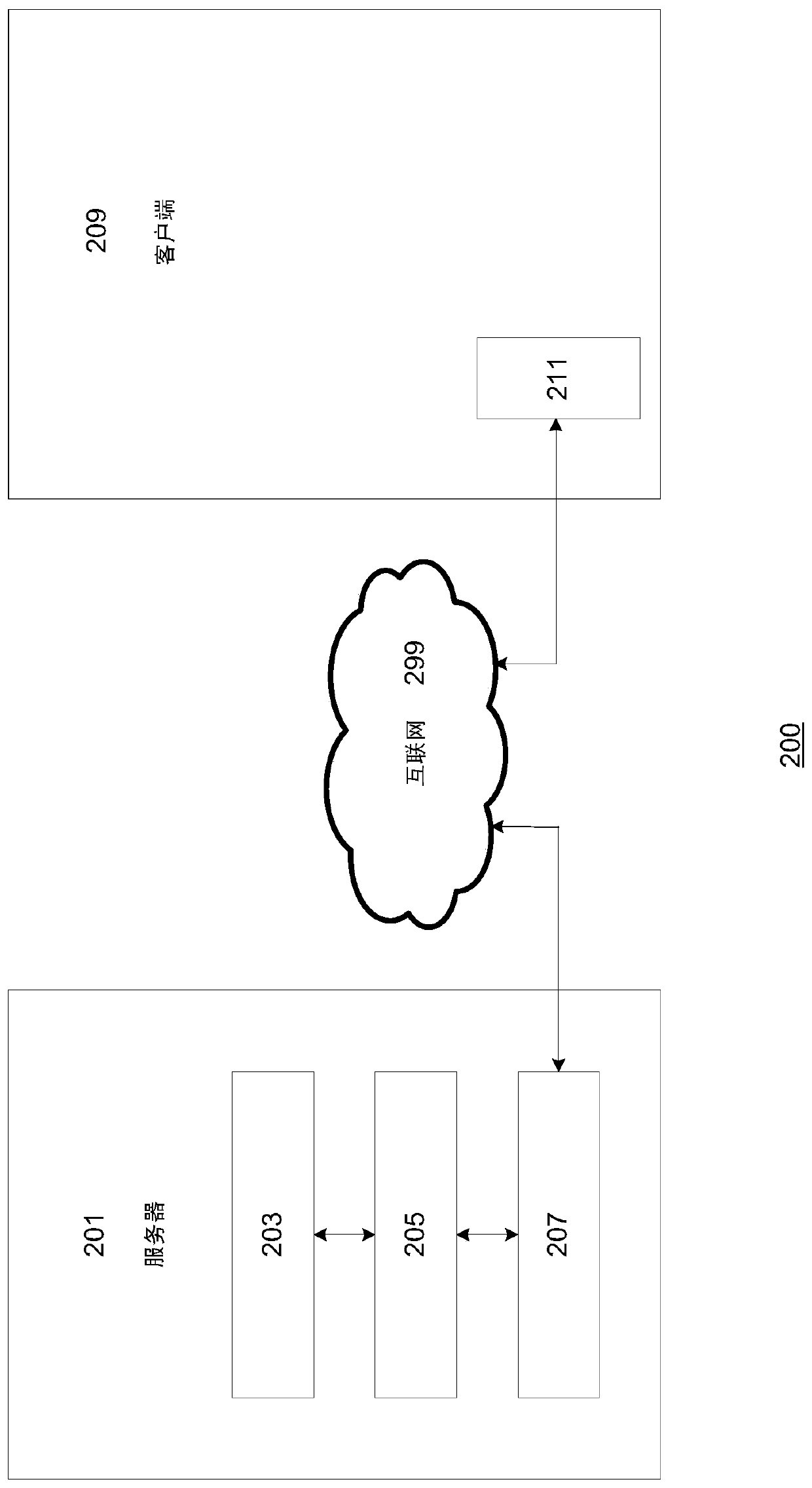

Network adaptive latency reduction through frame rate control

PendingCN110460496AConsistent quality of serviceStable service qualityData switching networksQuality of serviceNetwork conditions

The invention relates to network adaptive latency reduction through frame rate control. Novel solutions are provided for consistent Quality of Service in cloud gaming system that adaptively and dynamically compensate for poor network conditions by moderating rendered frame rates using frame rate capping to optimize for network latency savings (or surplus). In further embodiments, the encoding / sentframe rate to the client can also be managed in addition, or as an alternative to capping the rendered frame rates. The claimed embodiments not only maintain a constant Quality of Service (QoS) for the user, but may also be employed to leverage higher-performing networks to reduce operational costs.

Owner:NVIDIA CORP

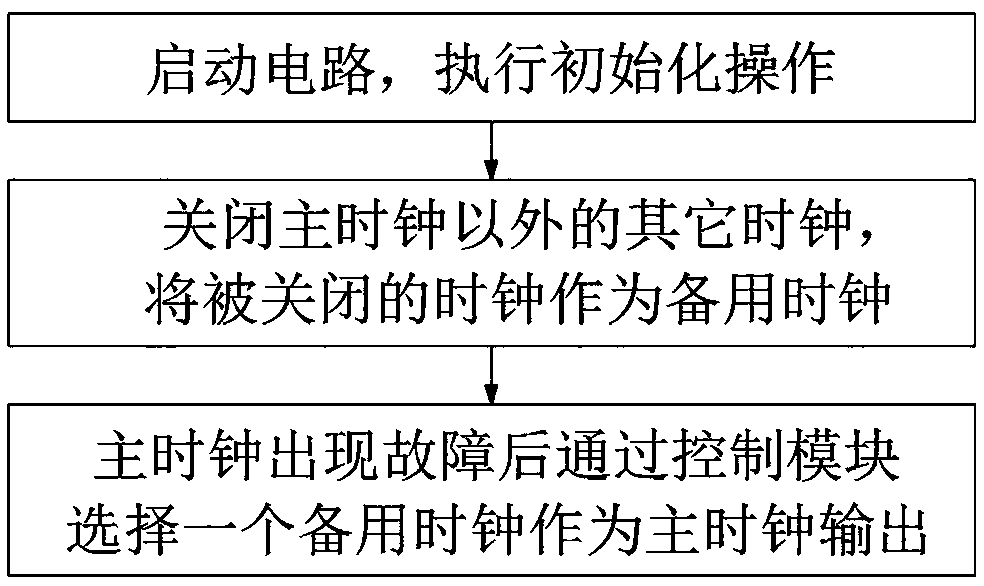

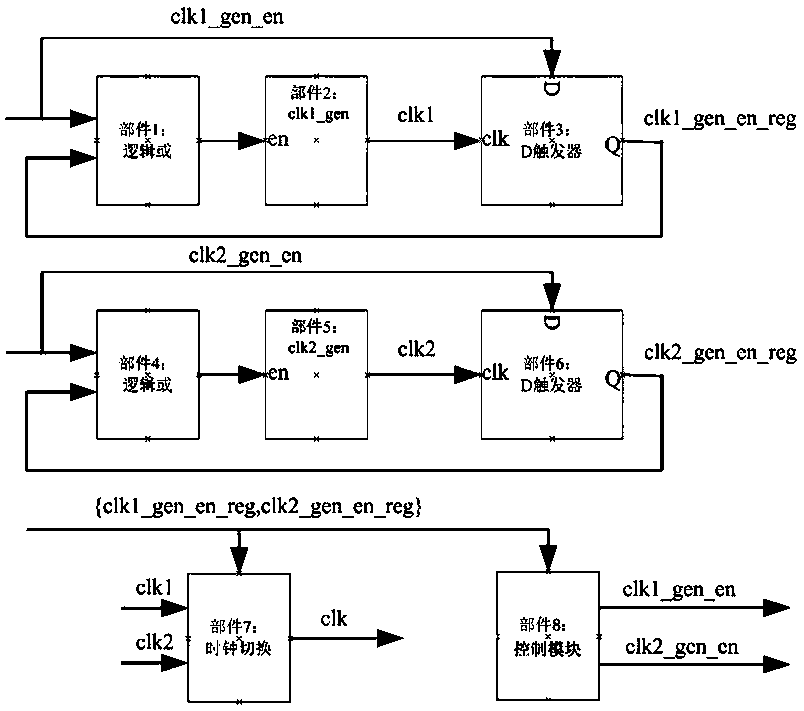

Chip clock circuit and control method thereof

ActiveCN110413041AImprove reliabilityLower power consumption levelsGenerating/distributing signalsComputer moduleCondition monitoring

The invention provides a chip clock circuit and a control method thereof. The chip clock circuit comprises a plurality of clocks, a clock switching module and a control module, the clocks comprise a logic OR module, a clock generation module and a trigger module, clock clk signals generated by the clocks are obtained through the input end of the clock switching module, and one clock is selected asa main clock to be output; and the control module monitors the state of each clock and controls the closing or opening of each clock. The state of a chip clock signal is monitored in real time through the control module; according to the real-time monitoring result, the clock signals are switched in time, high reliability of the clock signals of the chip is ensured, the chip is in a stable and reliable working state, the chip system can be ensured to run at a low power consumption level through a computer readable storage program, one more clock signal can be provided for the system selectively, and the flexibility of the clock of the chip system is improved.

Owner:EDGELESS SEMICON CO LTD OF ZHUHAI +1

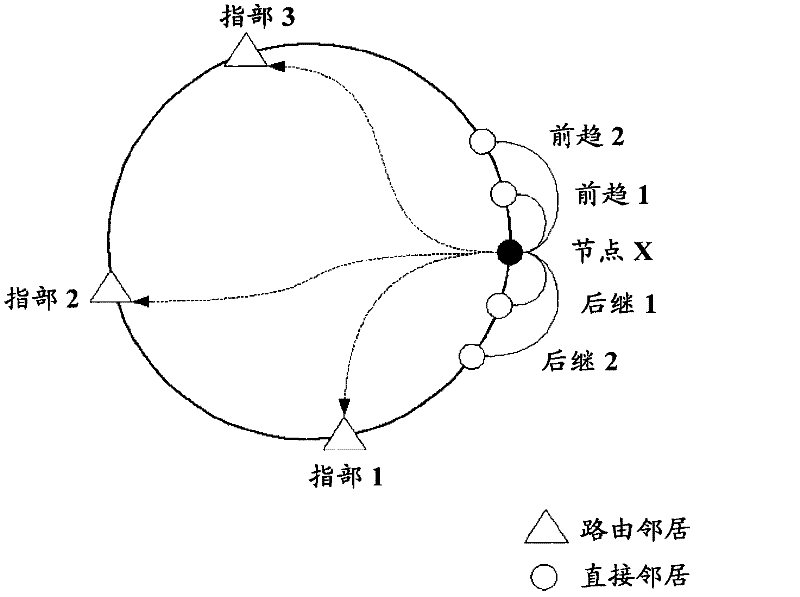

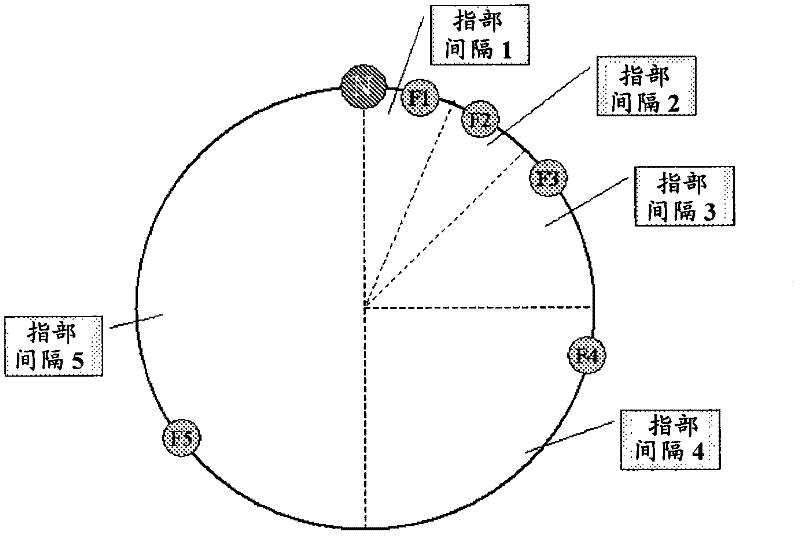

Routing mechanism for distributed hash table based overlay networks

InactiveCN102204346AOptimize Routing PerformanceExtended service lifePower managementEnergy efficient ICTRouting decisionDistributed hash table

A node for use within an overlay network, such as a Distributed Hash Table based overlay network, and which is configured to route packets across the overlay network. The node comprises means for making a routing decision based upon a knowledge of the power consumption levels and / or power availability of a set of peer nodes in the overlay network.

Owner:TELEFON AB LM ERICSSON (PUBL)

Artifical auris interna

InactiveUS20050234548A1Reduce power consumptionHigh resolutionElectrotherapyEar treatmentSwitching signalSignal amplification

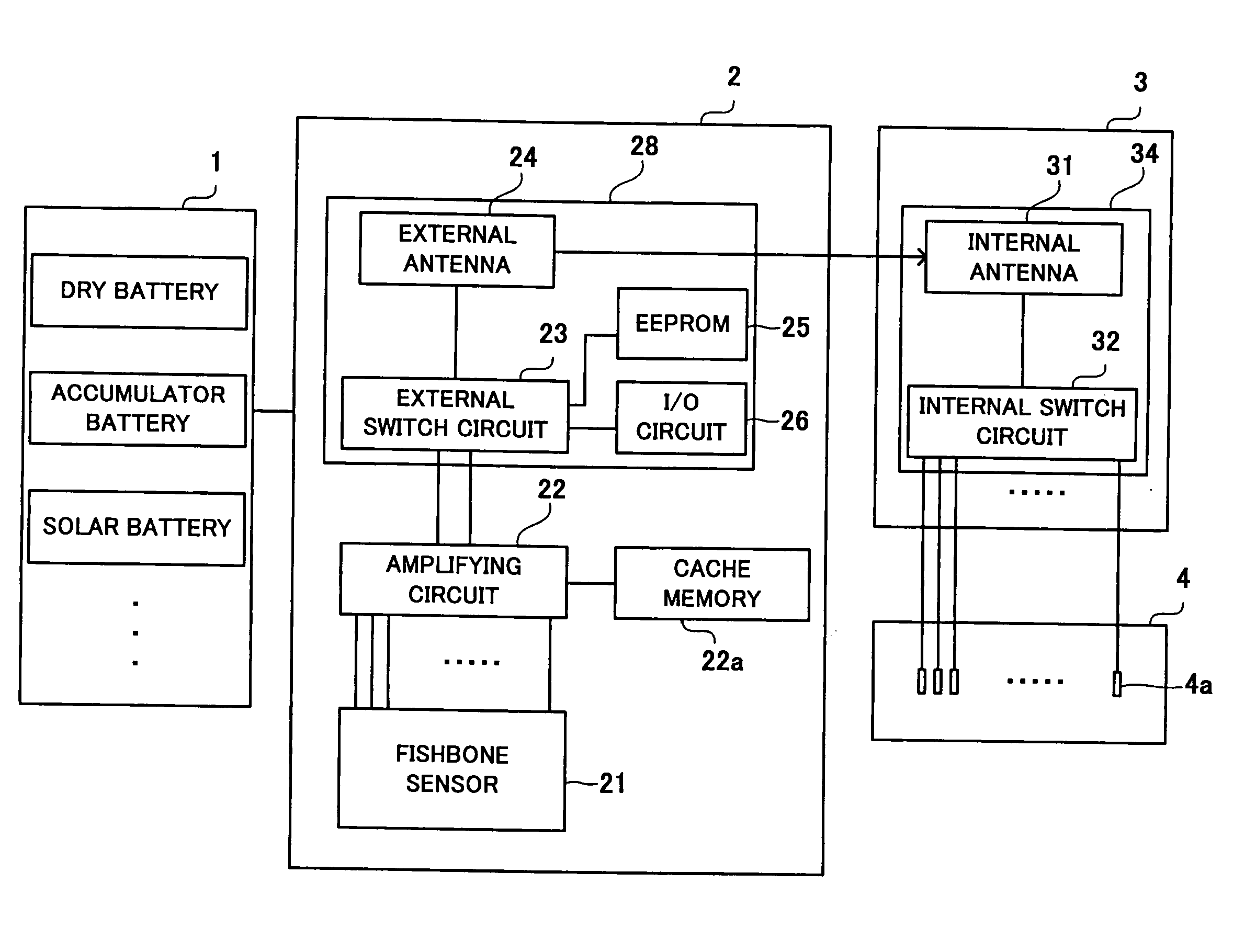

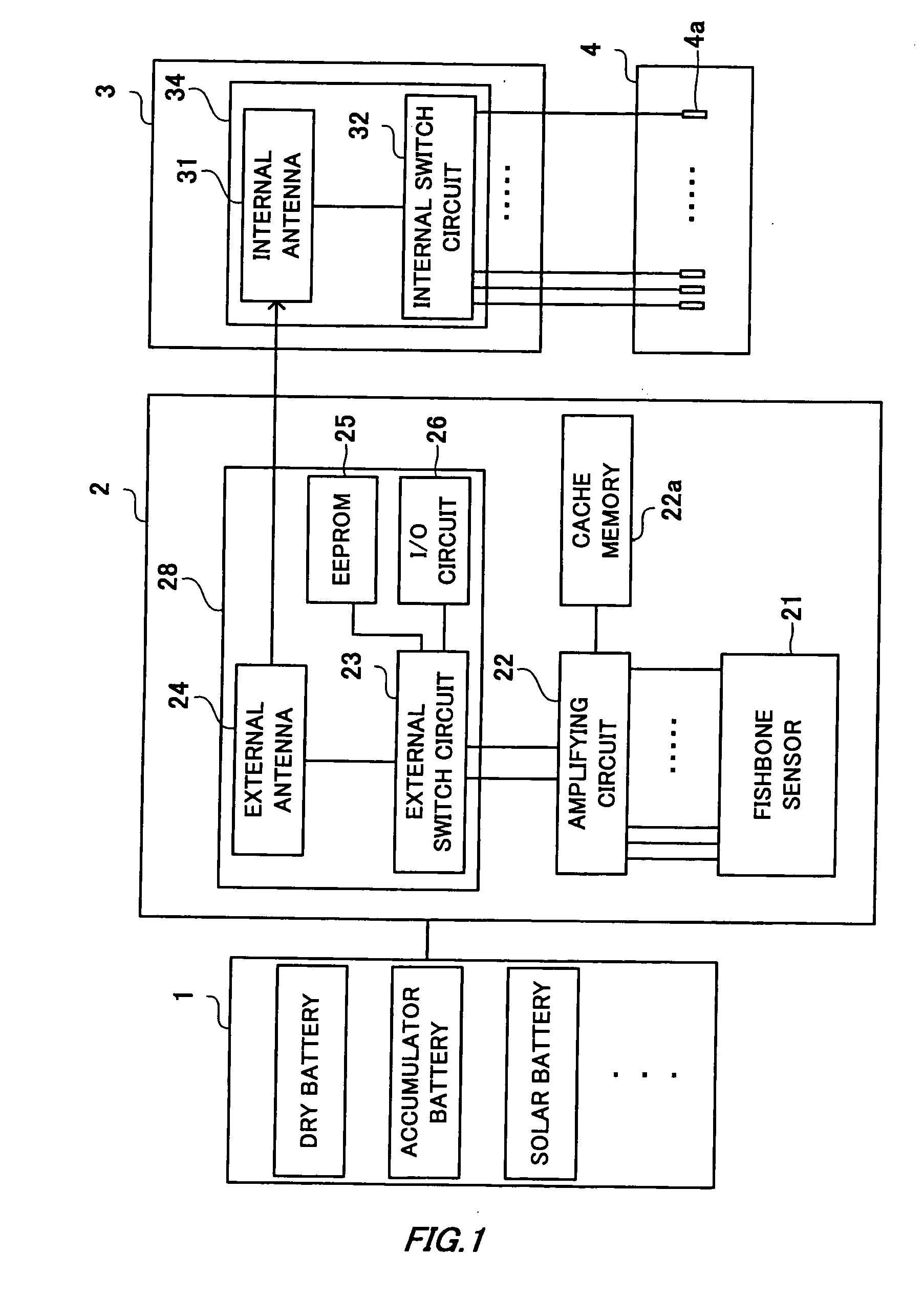

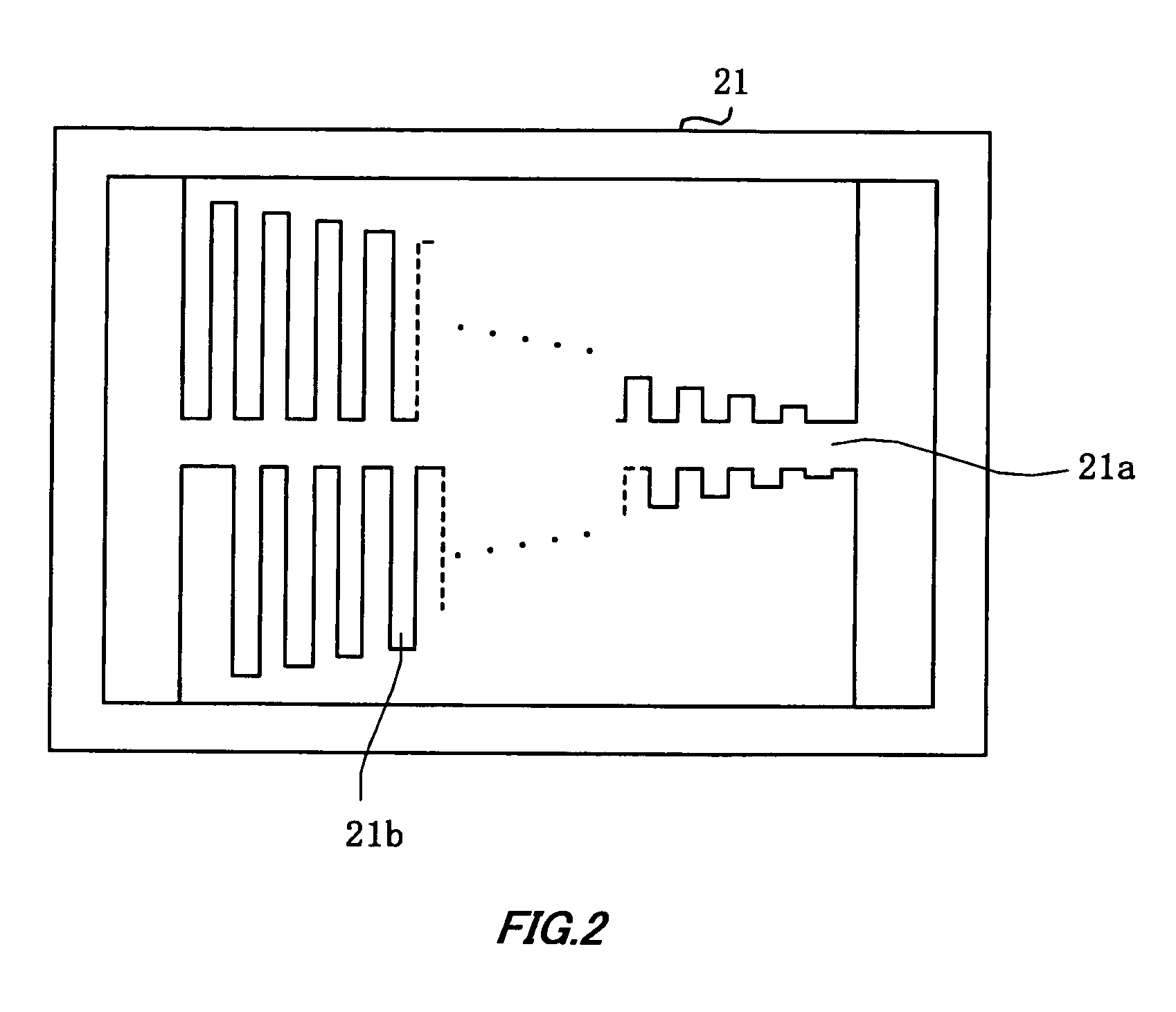

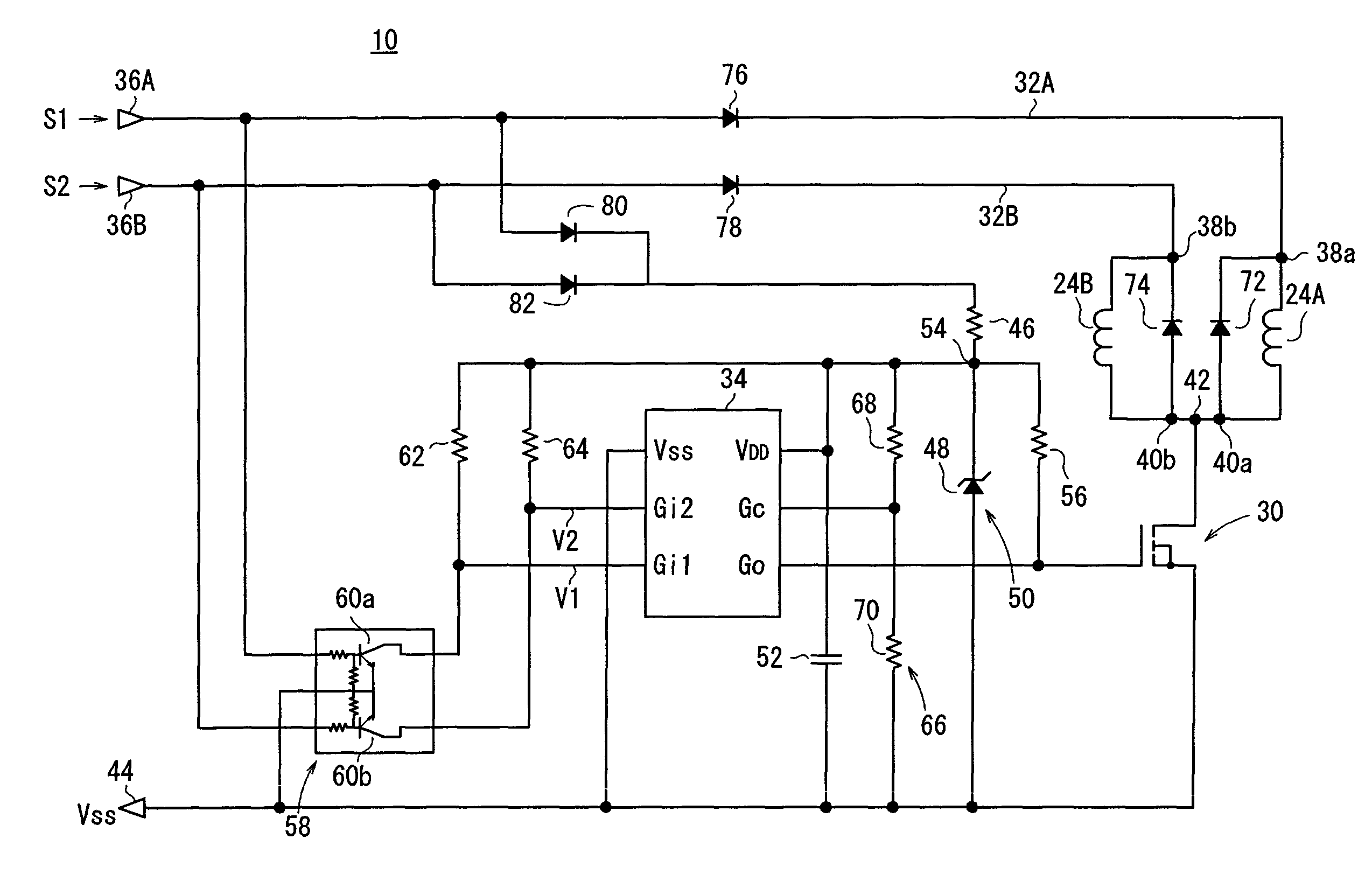

A fishbone sensor (21) has a plurality of resonators resonating with sounds having different frequencies from each other and converts the vibration of each resonator into a signal corresponding to each vibration level. An amplifying circuit (22) amplifies the signal converted by the fishbone sensor (21) by a predetermined gain and supplies it to an external switch circuit (23). The external switch circuit (23) switches signal supply paths and sequentially sends supplied signals via an external antenna (24). An internal switch circuit (32) switches signal supply paths and sequentially supplies the signals sent via an internal antenna (31) to a plurality of electrodes (4a), thereby stimulating the nerves in the cochlea.

Owner:TOKYO ELECTRON LTD

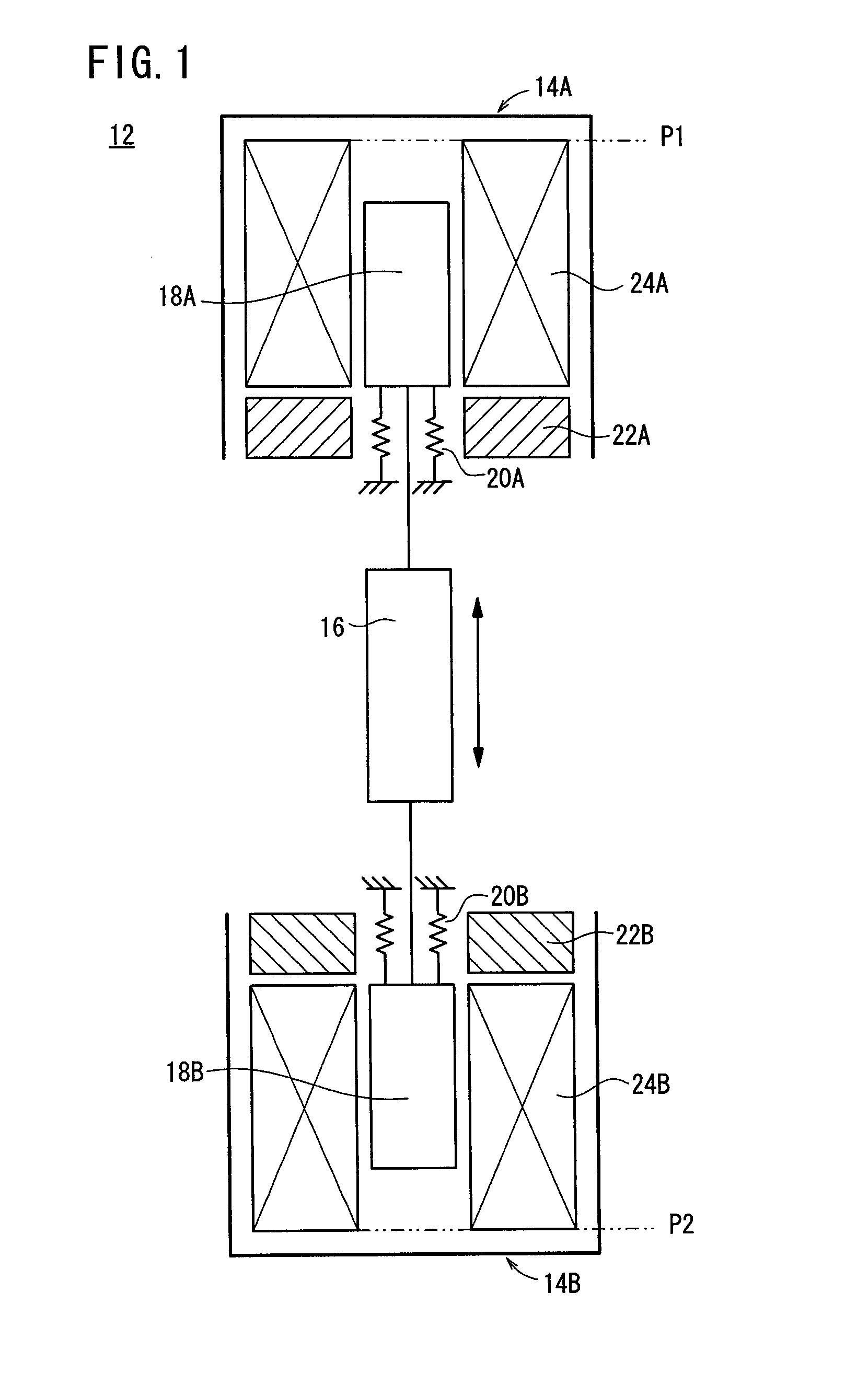

Solenoid-operated valve controller

ActiveUS7758015B2Small sizeReduce manufacturing costOperating means/releasing devices for valvesElectric switchesSolenoid valveElectromagnetic coil

A solenoid-operated valve controller includes a first signal line and a second signal line, which are connected respectively to ends of a first solenoid coil and a second solenoid coil. The first solenoid coil and the second solenoid coil have other ends, which are electrically connected in common to a switch. One of the first and second solenoid coils, which corresponds to signal states of a plurality of input signals that are supplied respectively to the first and second signal lines, is selected, and the switch is turned on and off to control the selected one of the first and second solenoid coils.

Owner:SMC CORP

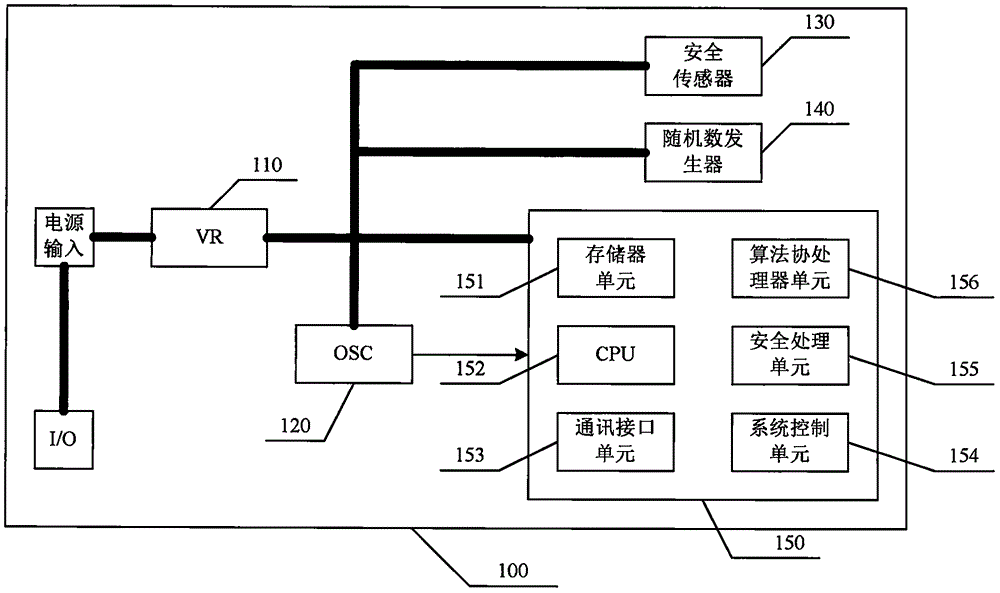

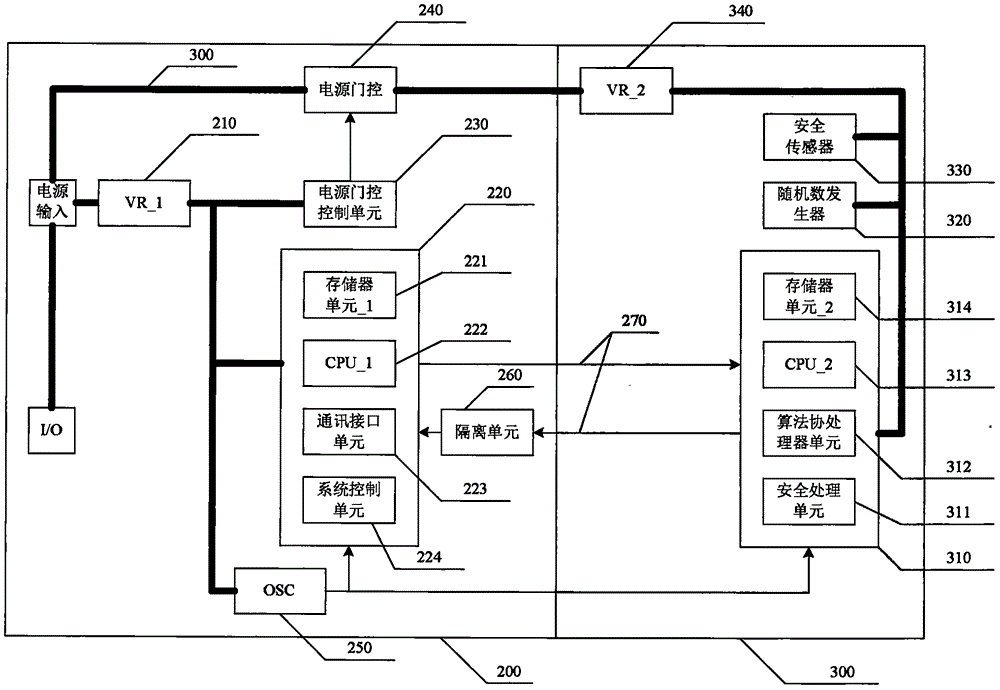

Low-electric-leakage bi-CPU core safe chip configuration

InactiveCN106066970AReduce overall power consumptionReduce power consumptionInternal/peripheral component protectionPower supply for data processingCommunication interfaceHigh complexity

The invention provides a low-electric-leakage bi-CPU core safe chip configuration, which realizes minimal safe physical isolation and static power consumption. The configuration employs two CPU subsystems, one of which is a low performance and low power dissipation logic gate count for processing communication interface and other non-security applications. The other CPU subsystem is a high-performance high-security CPU for providing complex and high performance cipher calculation, sensitive information processing and other high security applications. The high-performance CPU system is high in logic complexity, and a power supply is cut off by a gate control when a chip enters into a standby state to lower the integral electric leakage and power consumption of the chip.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

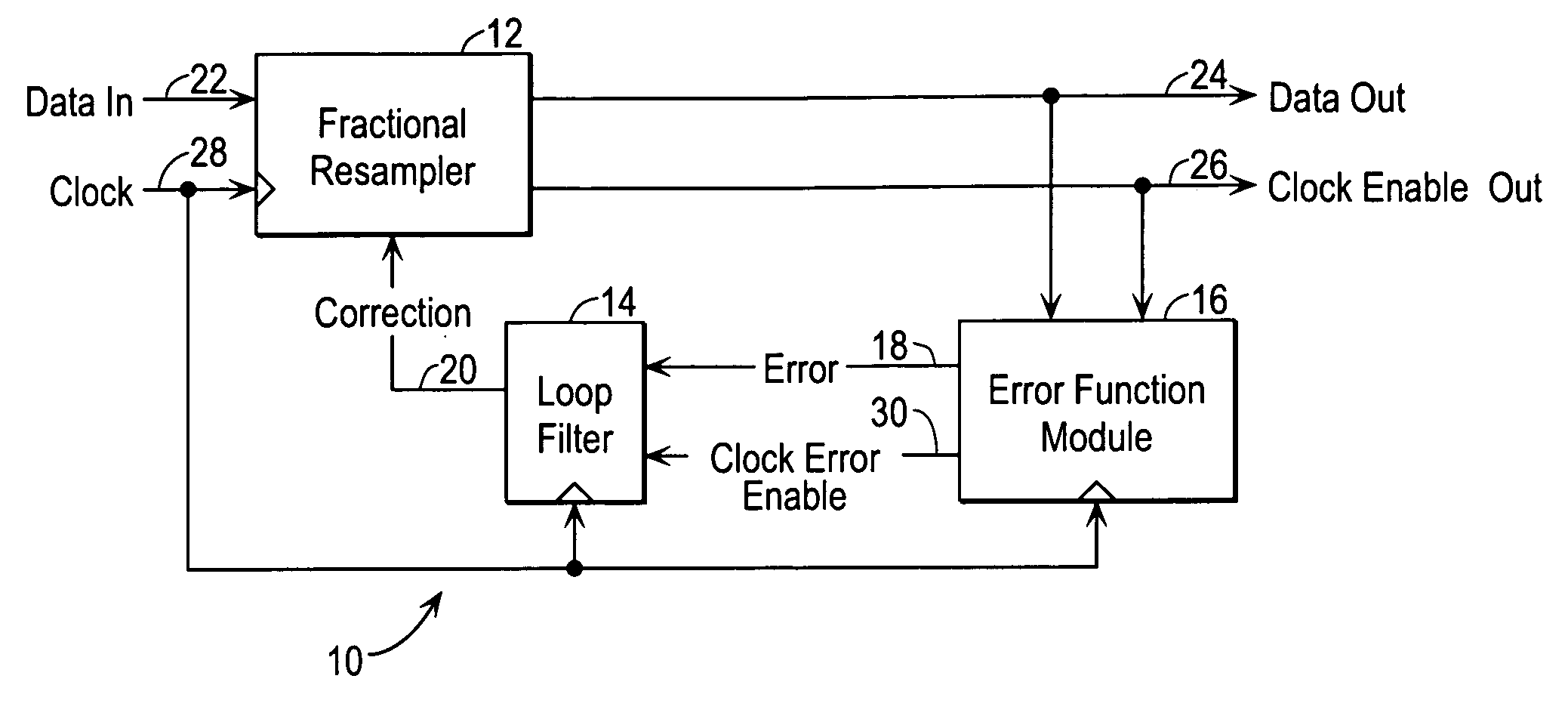

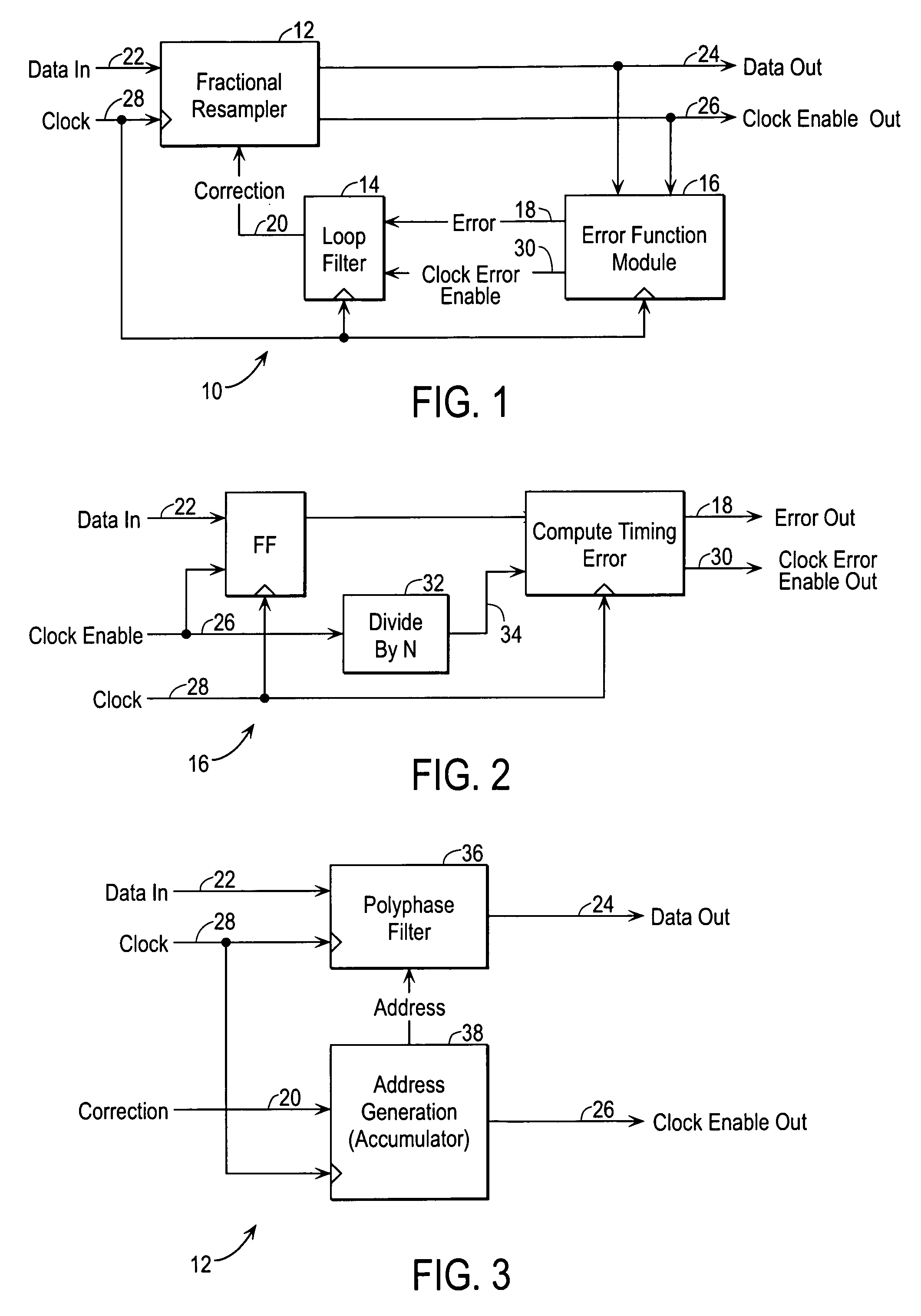

Method and system for providing adaptive timing recovery for low power application

ActiveUS7200189B1Execution rateLower power consumption levelsPulse automatic controlElectric pulse generatorPower applicationLoop filter

A system for providing adaptive timing recovery is provided. In an exemplary embodiment, the system includes a fractional resampler, an error function module and a loop filter, arranged collectively to form a timing recovery loop. In an initial mode, the error function module compares the output of the fractional resampler with a reference signal to determine an error, if any. An error signal is generated accordingly based on the error. The error signal is then provided to the loop filter allowing the loop filter to generate a correction signal. The correction signal is provided to the fractional resampler to allow the fractional resampler to generate an output which minimizes the error. When the error function module determines that the error is within an acceptable range, i.e., a timing lock is achieved, the system goes into a steady mode. In the steady mode, the error function module is directed to execute at a slower rate. By executing at a slower rate, the error function module is able to operate at a reduced level of power consumption.

Owner:AVAGO TECH INT SALES PTE LTD

A Positioning Method Based on Locator

ActiveCN103237292BSolve power consumptionSolve the problem of indoor positioning trackingEnergy efficient ICTNear-field systems using receiversAccelerometerGyroscope

The invention provides a locator-based locating method. A locator comprises a central processing unit, a wireless unit, a global positioning system (GPS) locating unit, an inertial navigation unit, a mobile communication unit and a storage unit. The method comprises the following steps that a corresponding external monitoring end is searched based on a wireless detection signal; whether the current distance between the locator and the external monitoring end exceeds a first distance threshold value is determined based on the current wireless signal intensity and a mapping table stored in the storage unit; the inertial navigation unit is started when the current distance exceeds the first distance threshold value; whether the current distance exceeds a second distance threshold value is determined by detecting whether wireless connection can be established between the locator and the external monitoring end; and the mobile communication unit and the GPS locating unit are started when the current distance exceeds the second distance threshold value. By combining low power consumption Bluetooth, wireless fidelity (WIFI), a gyroscope and an accelerometer, the problem of power consumption due to the sustained use of a mobile network and GPS locating is solved.

Owner:钟国峰

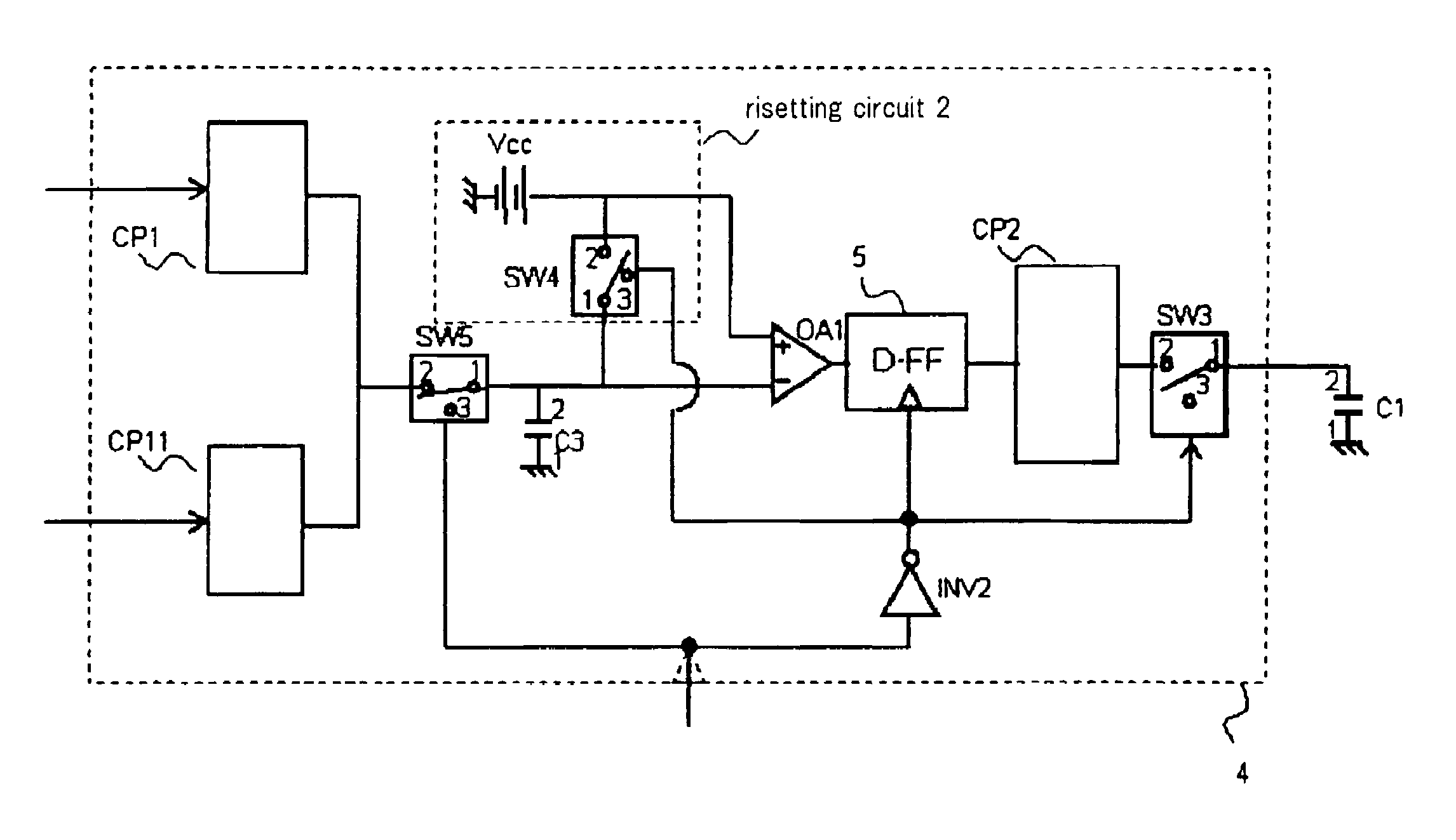

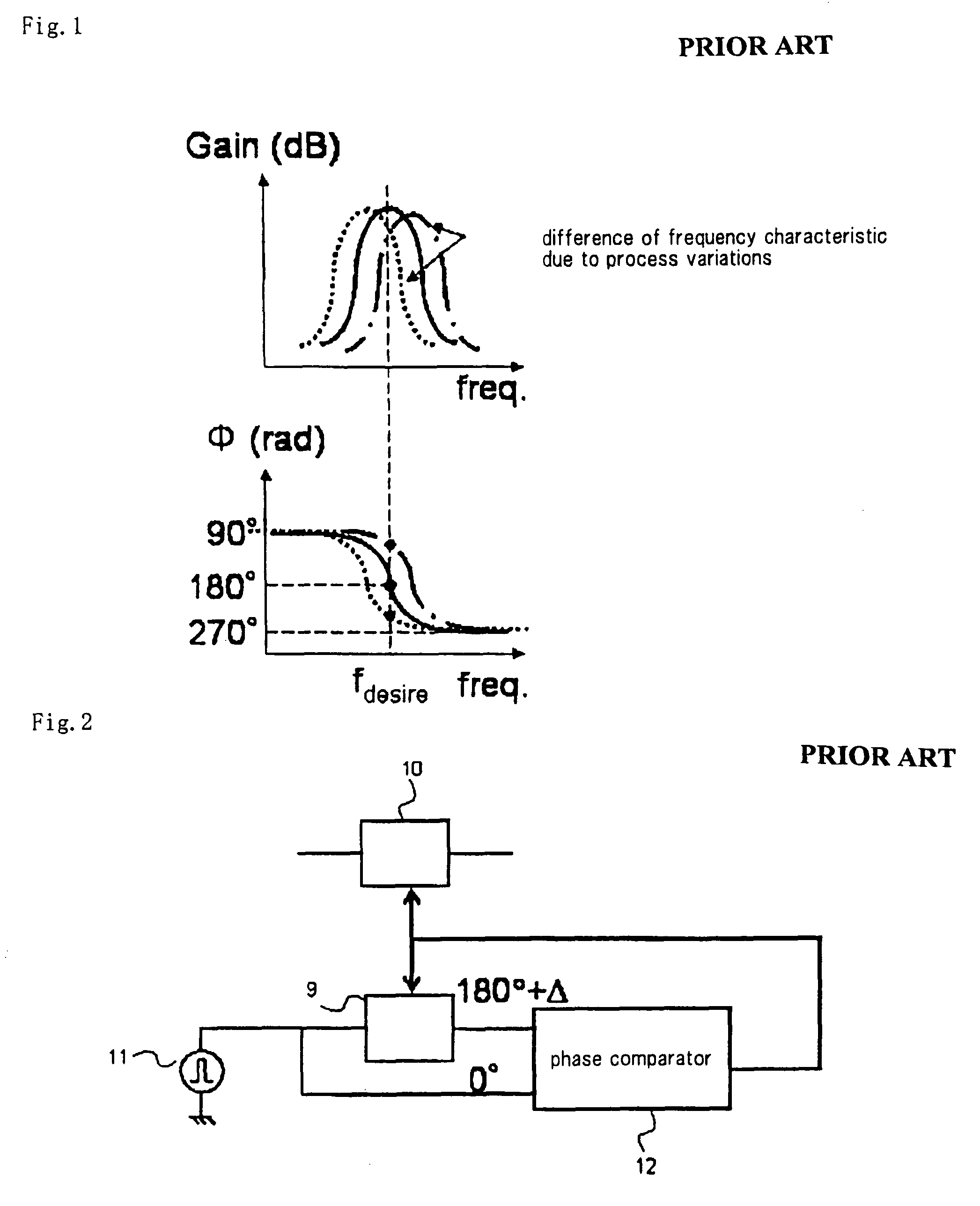

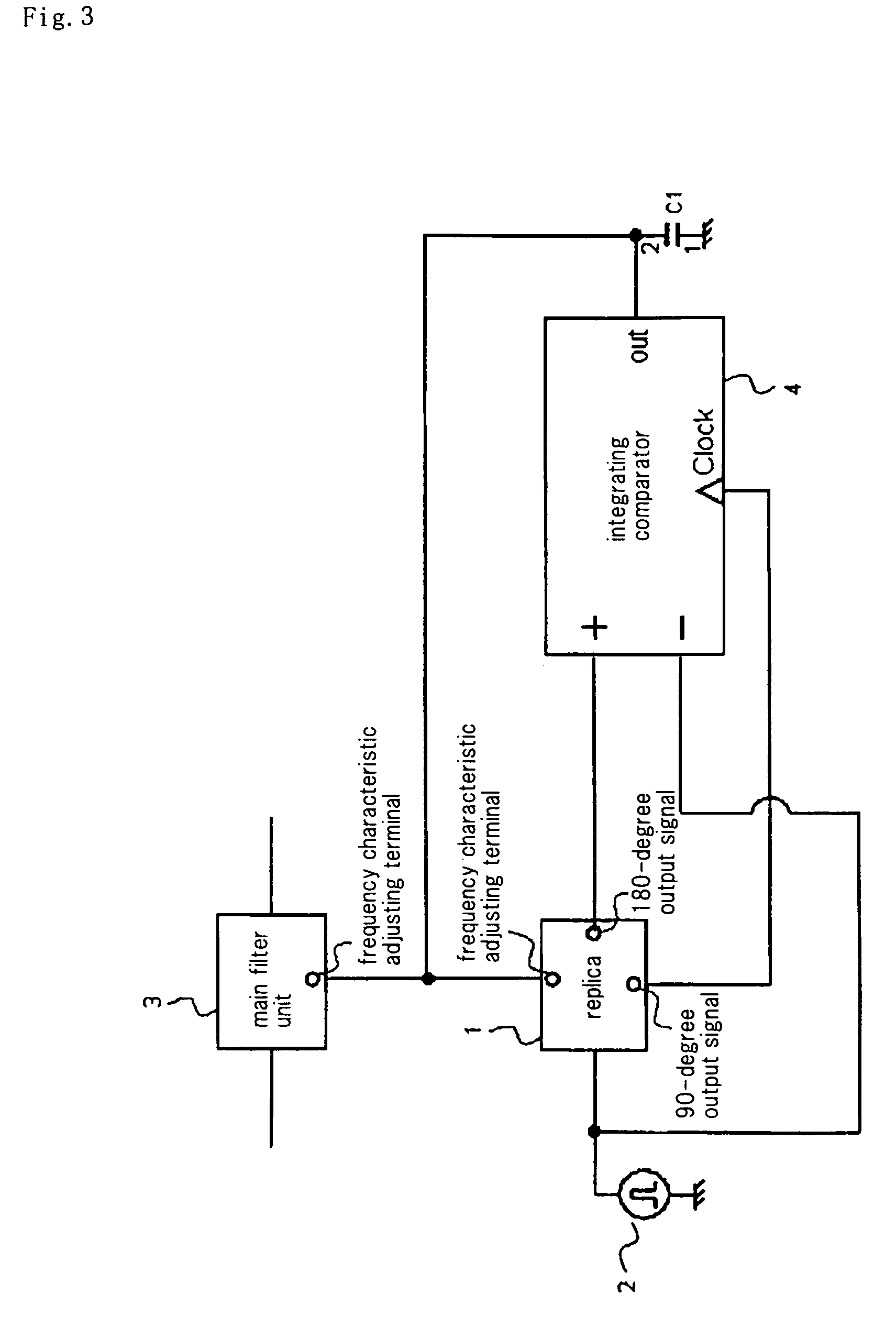

Automatic adjustment circuit, and filter circuit

ActiveUS7924068B2Reduce areaLower power consumption levelsOscillations generatorsTransmissionEngineeringFrequency characteristic

Owner:NEC CORP

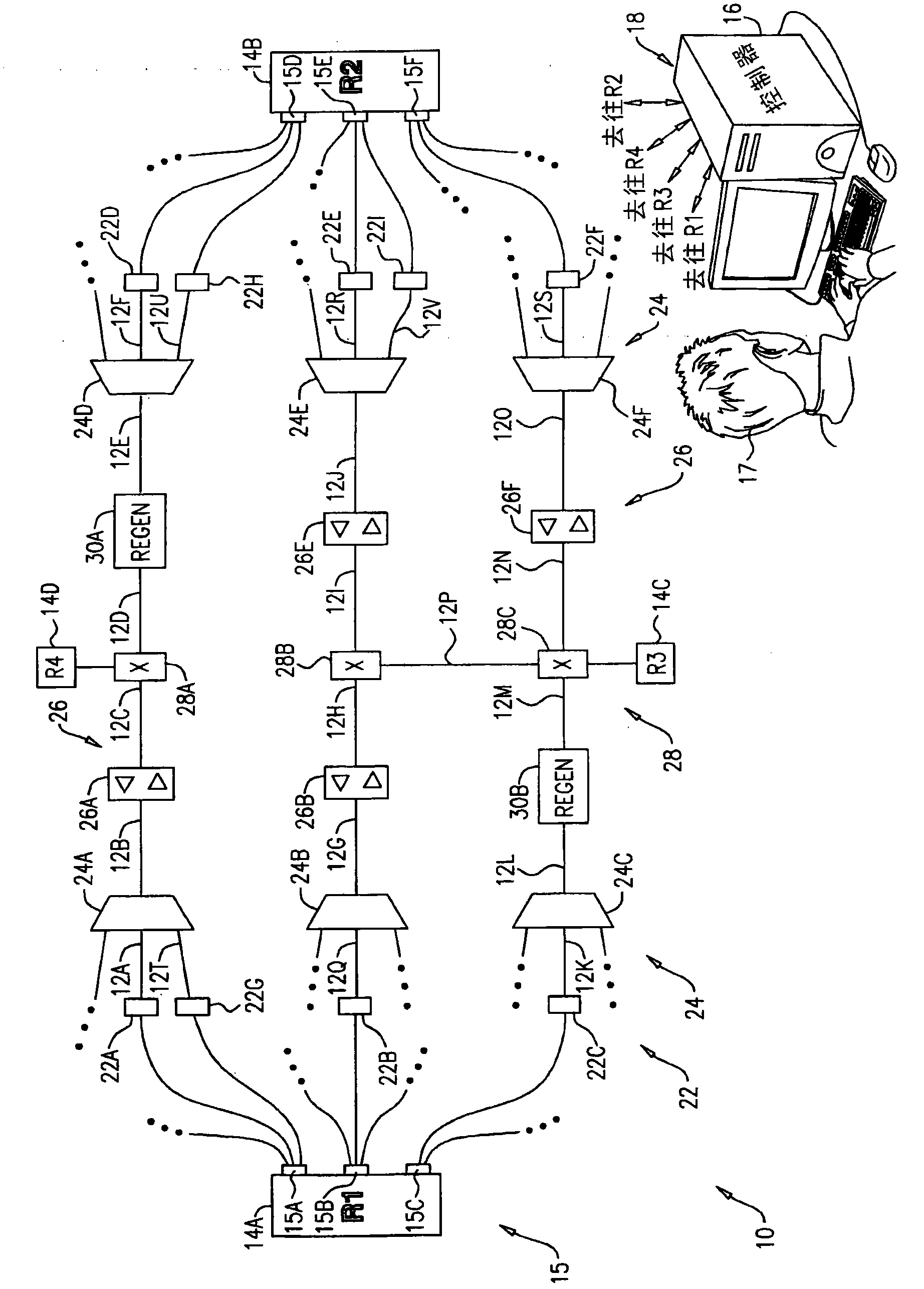

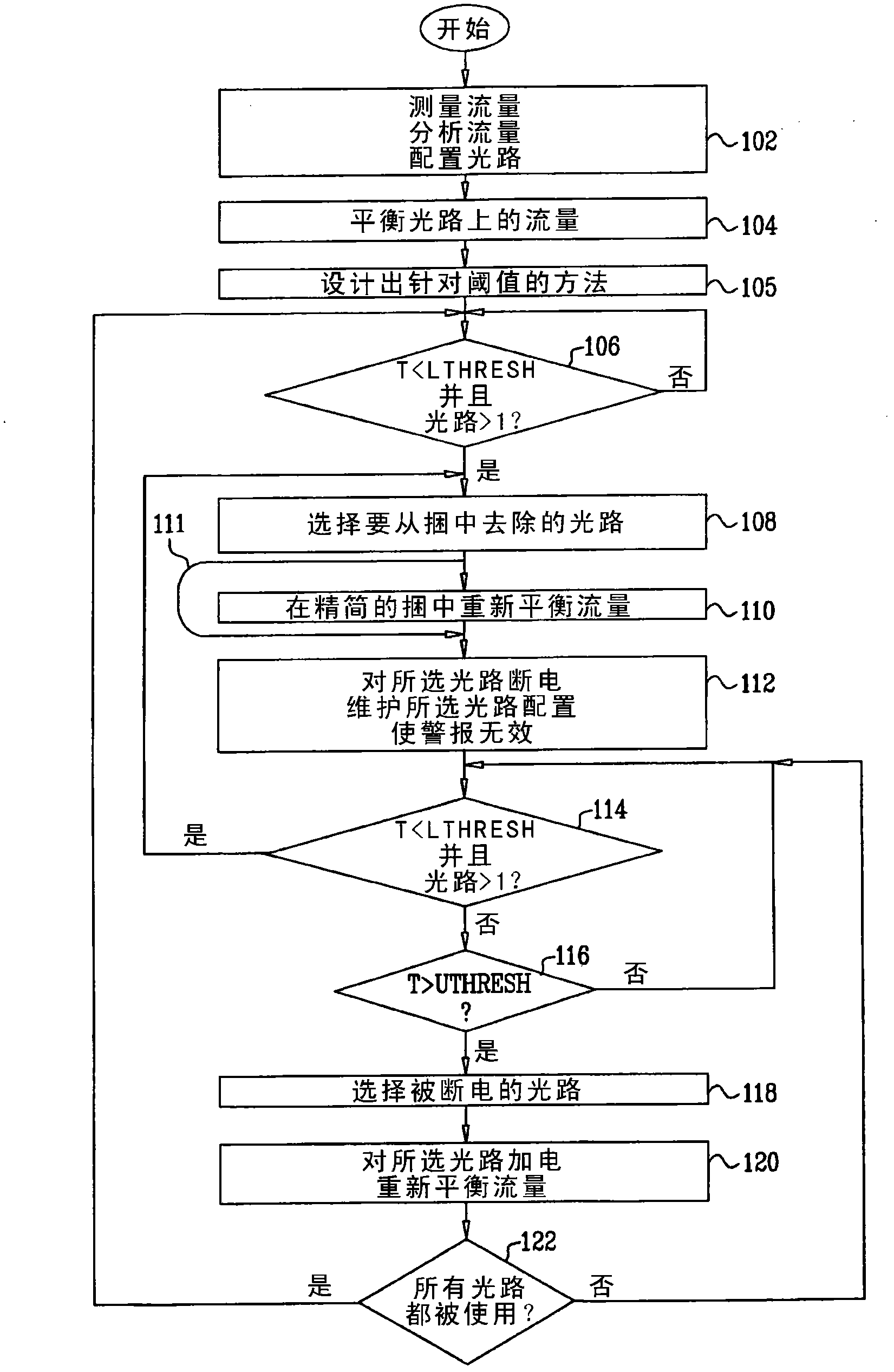

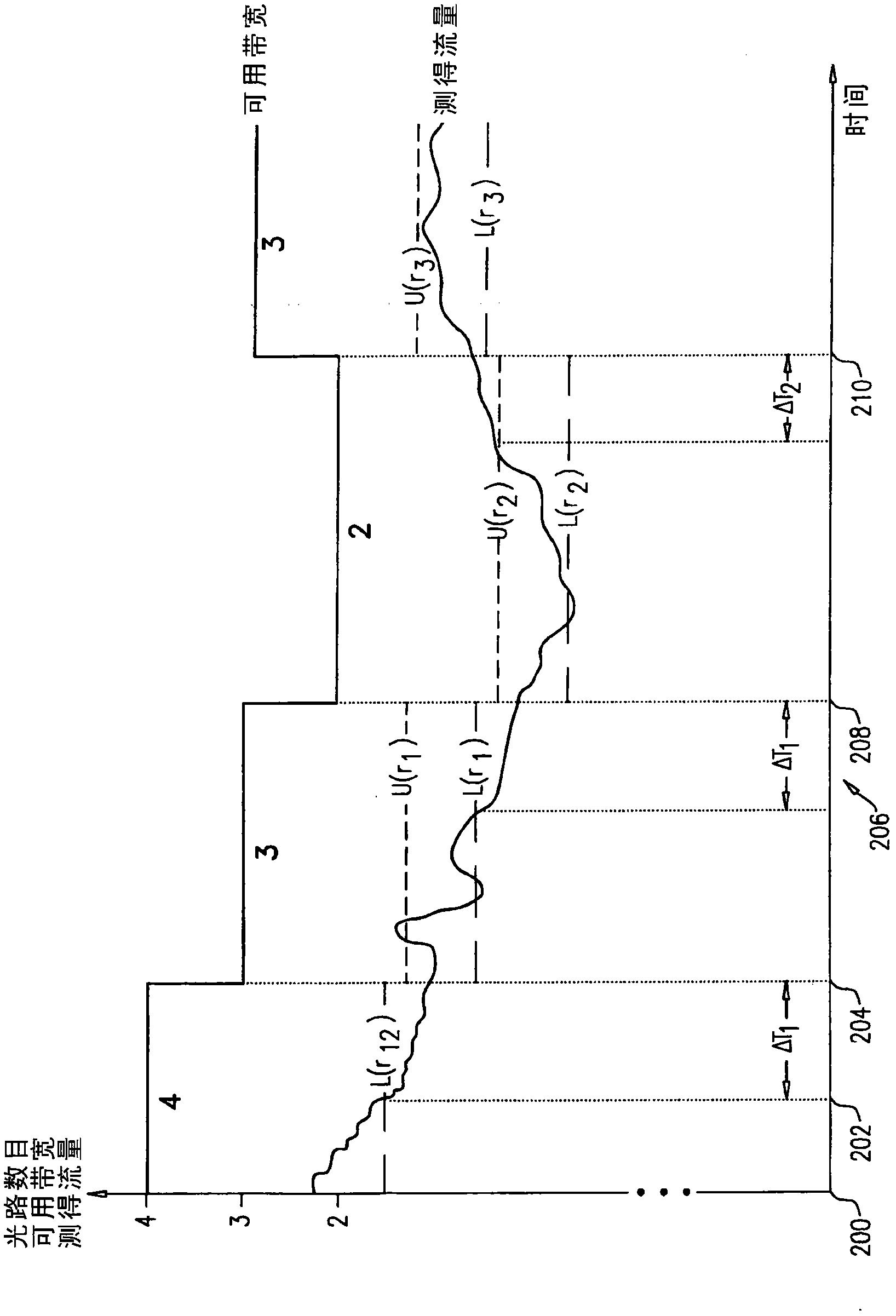

Power save mode for lightpaths

InactiveCN102498684ALower power consumption levelsEnergy efficient ICTWavelength-division multiplex systemsComputer networkPower consumption

A method for communicating optically between nodes of an optical network, including forming, between a first node and a second node of the network, a set of lightpaths, each of the set of lightpaths having a respective configuration, transferring communication traffic between the first and second nodes via the set of lightpaths, determining, for the set of lightpaths, that a communication traffic level associated therewith is less than a predetermined threshold, in response to the determining, removing at least one lightpath having a given configuration from the set of lightpaths to form a reduced set of lightpaths and transferring the communication traffic between the first and second nodes via the reduced set of lightpaths, while reducing the level of power consumption in the at least one lightpath and while maintaining the given configuration of the at least one lightpath.

Owner:CISCO TECH INC