Current integrating decision feedback equalizer used in high-speed serial interface

A technology of decision feedback equalization and high-speed serial interface, which is applied in the field of integrated circuits and can solve problems such as performance degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Below the present invention will be further described in conjunction with the embodiment in the accompanying drawing:

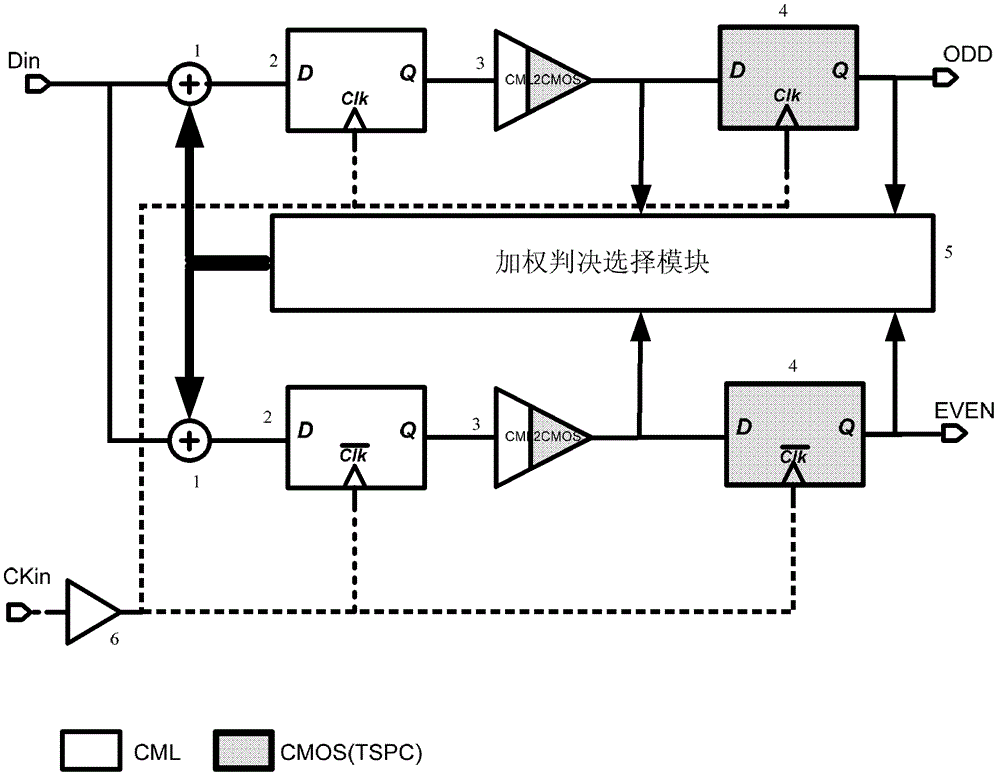

[0038] The DFE architecture proposed by the present invention is as follows image 3 As shown, the input signal Din, the clock input signal CKin, the output odd signal (ODD), the output even signal (EVEN). Its decision feedback equalizer includes: two analog weighters 1, two current mode (CML) D flip-flops 2, two CML to CMOS level conversion circuits 3, two TSPC D flip-flops 4, weighted decision selection module 5, input clock buffer Device module 6 and so on. This architecture includes upper and lower circuits, and their connections are similar: each analog weighter 1 is connected to a current mode D flip-flop 2, and then connected to a CML-to-CMOS level converter 3, and the output signal of this converter is connected to to a TSPC-type D flip-flop 4, and then get two output signals (ODD and EVEN) of odd and even, the output signal of the CML-to-CMO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More