A kind of semiconductor device and its manufacturing method, electronic device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, electric solid state devices, circuits, etc., can solve the problems of control gate short circuit or breakdown, easy contact and damage control gate, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

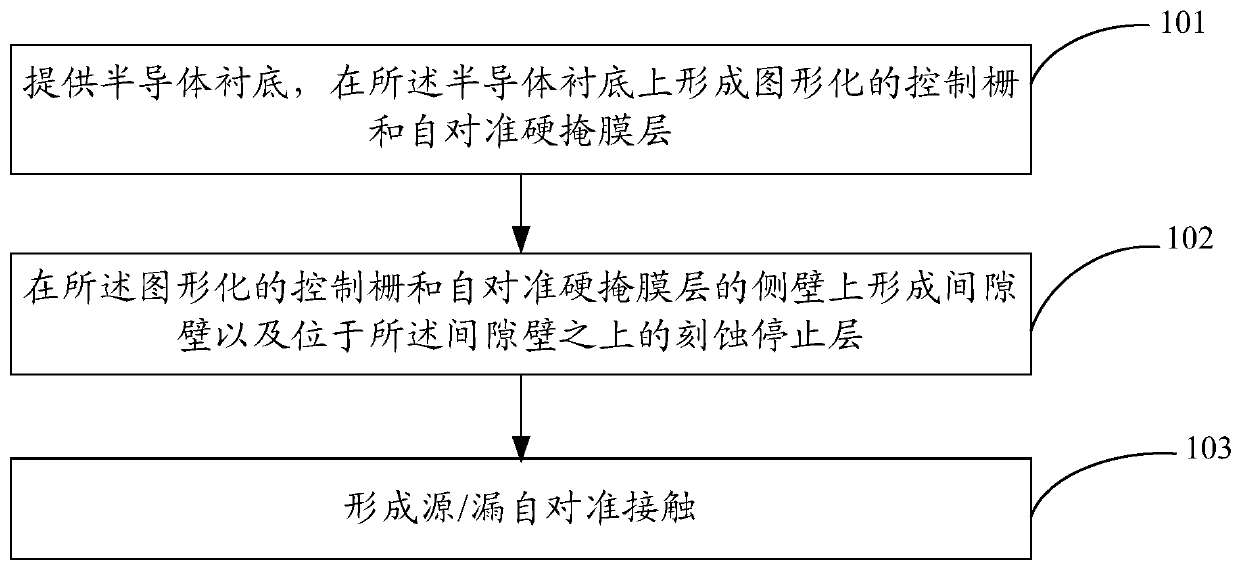

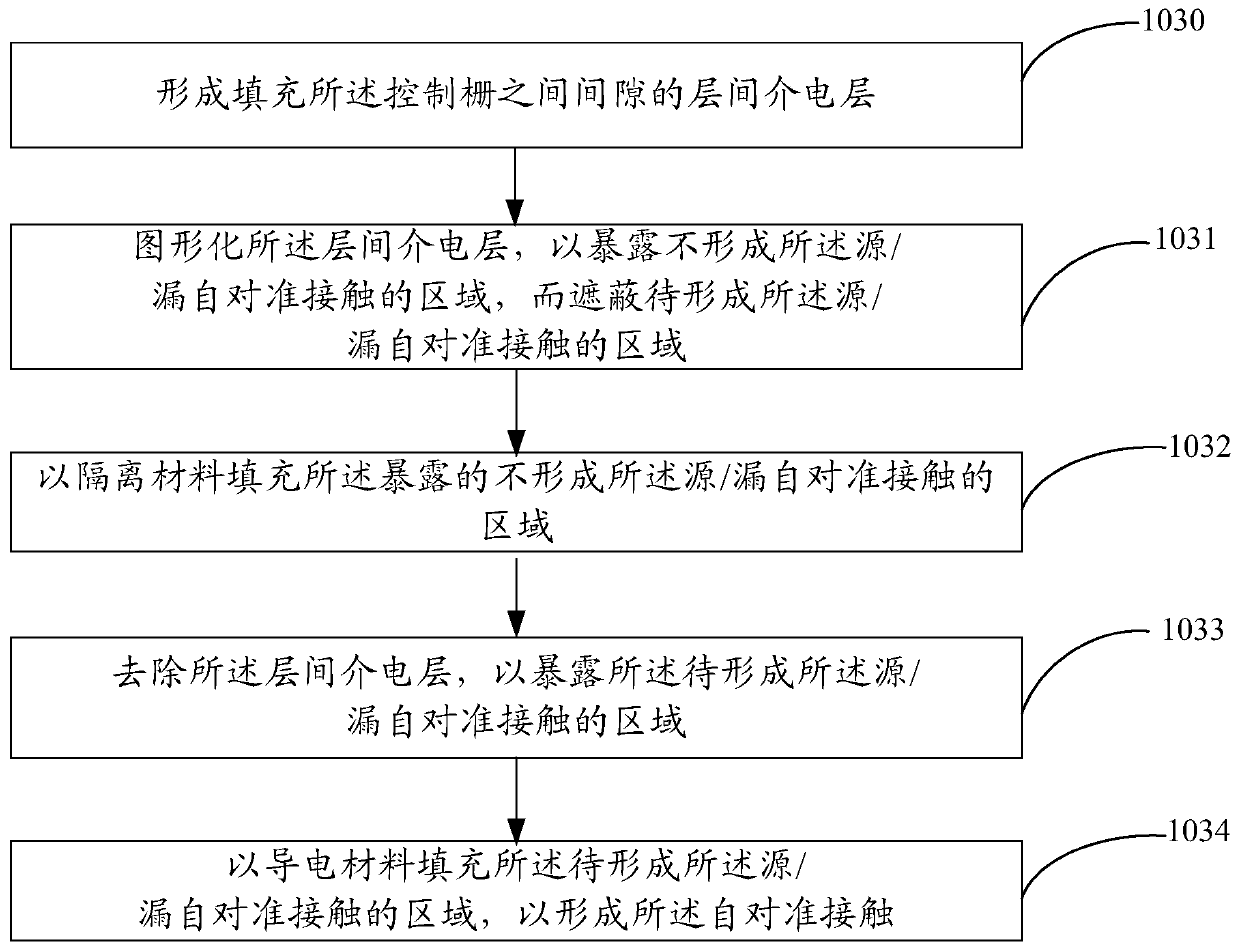

[0042] The following will refer to Figure 2A ~ Figure 2N as well as Figure 3A ~ Figure 3H A method for manufacturing a semiconductor device according to an embodiment of the present invention is described in detail, wherein, Figure 2A ~ Figure 2N It shows a schematic cross-sectional view in the direction of the active region of the semiconductor device obtained by sequentially implementing each step of the manufacturing method of the semiconductor device according to an embodiment of the present invention; Figure 3A ~ Figure 3H A schematic cross-sectional view of the active region direction and the isolation region direction of the semiconductor device obtained by sequentially implementing various steps in the method for manufacturing a semiconductor device according to an embodiment of the present invention is shown. in Figure 3A ~ Figure 3H corresponds to Figure 2G to Figure 2N ,and Figure 2A ~ Figure 2F Corresponding cross-sectional view of the isolation zone dir...

Embodiment 2

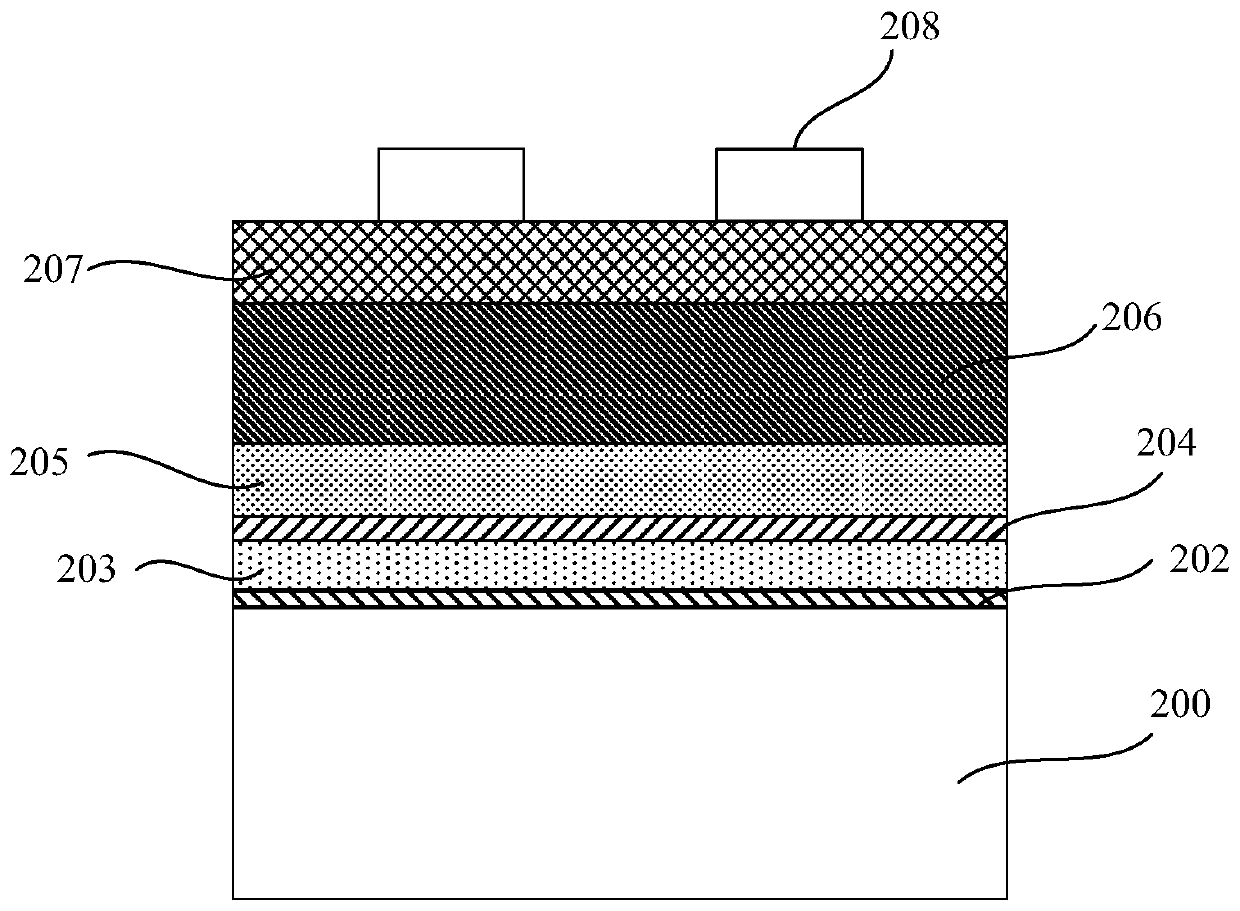

[0088] The present invention also provides a semiconductor device fabricated by the above method, such as Figure 4A with Figure 4BAs shown, the semiconductor device includes: a semiconductor substrate 400, an isolation structure 401 is formed in the semiconductor substrate 400, an active region is separated and defined by the isolation structure 401, and a gate stack is formed in the active region, so The gate stack includes a tunnel oxide layer 402, a floating gate 403, a gate dielectric layer 404, a control gate 405 and a hard mask layer 406, and the gate dielectric layer 404, the control gate 405 and a hard mask layer 406, a first spacer 407 and a second spacer 408 are formed on the sidewall of the gate stack and / or the sidewall of the control gate 405, A source / drain is formed on the side of the source / drain, and a self-aligned contact 409 located above the source and drain, and an isolation layer 410 is formed in a region outside the self-aligned contact 409 to isolate...

Embodiment 3

[0096] Still another embodiment of the present invention provides an electronic device, including a semiconductor device and an electronic component connected to the semiconductor device. Wherein, the semiconductor device includes: a semiconductor substrate, an isolation structure is formed in the semiconductor substrate, an active area is separated and defined by the isolation structure, a gate stack is formed in the active area, and the gate stack Including a tunnel oxide layer, a floating gate, a gate dielectric layer, a control gate and a hard mask layer, a gate dielectric layer, a control gate and a hard mask layer are formed on the isolation structure, and the gate A first spacer and a second spacer are formed on the sidewall of the stacked layer and / or the sidewall of the control gate, and source / drain electrodes are formed on both sides of the gate stack layer, and are located between the source and drain electrodes. self-aligned contacts on the self-aligned contacts, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com