An integrated process method for norflash devices without cldd mask

A process method and device technology, applied in the field of semiconductor integrated circuit manufacturing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The specific embodiments of the present invention are given below in conjunction with the accompanying drawings, but the present invention is not limited to the following embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in very simplified form and use imprecise ratios, which are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

[0028] The present invention proposes a kind of NorFlash device integration technique method that saves CLDD photomask, comprises the following steps:

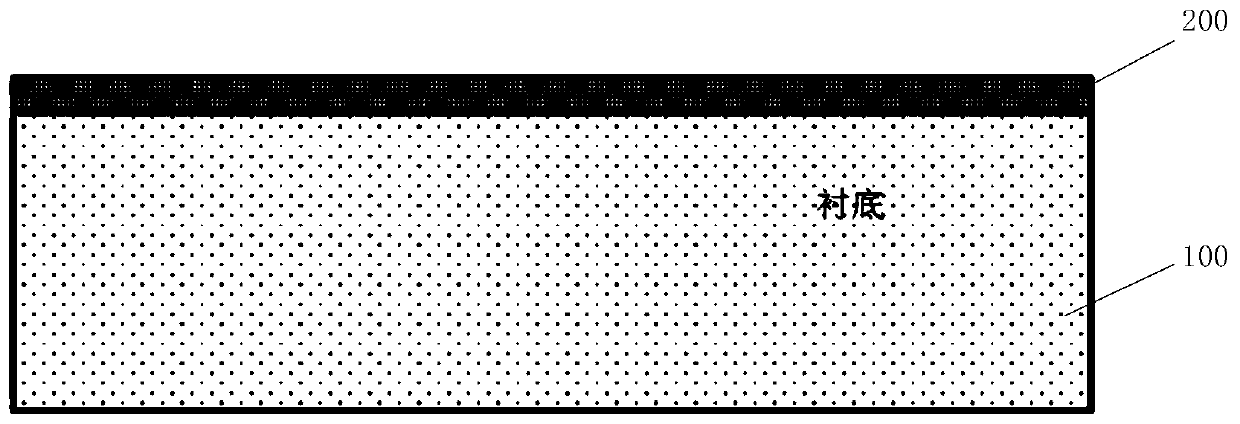

[0029] A tunnel oxide layer 200 is formed on the substrate 100, such as figure 1 shown;

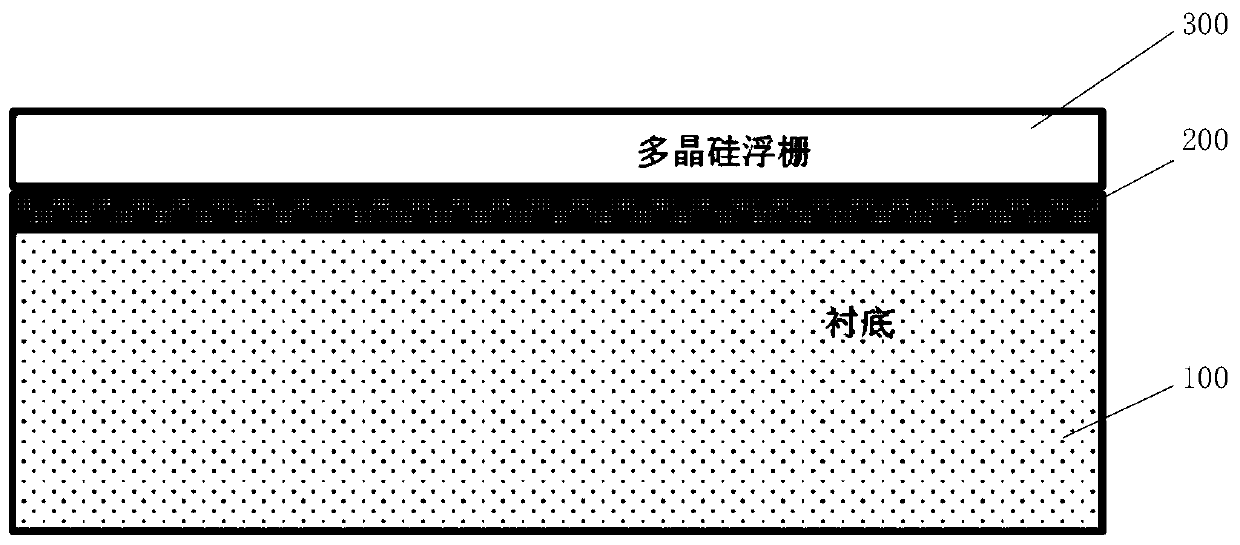

[0030] A polysilicon floating gate layer 300 is formed on the above structure, such as figure 2 shown;

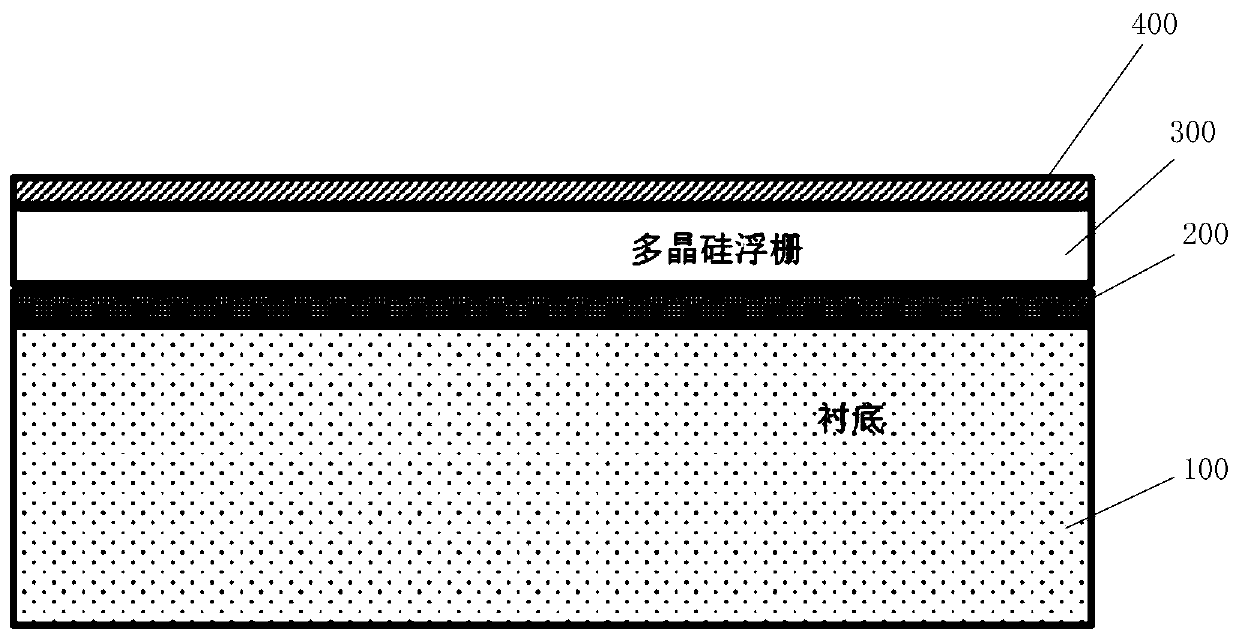

[0031] A dielectric layer 400 is formed on the above structure, such as image 3 shown;

[0032] A polysilic...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More