Full waveguide lateral polysilicon optical interconnection system based on standard cmos process

A polysilicon, optical interconnect technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of design structure loss, energy loss, low luminous efficiency, etc., to reduce energy loss, increase responsivity, and improve responsivity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The full-waveguide lateral polysilicon optical interconnection system based on the standard CMOS process of the present invention will be described in detail below with reference to the embodiments and the accompanying drawings.

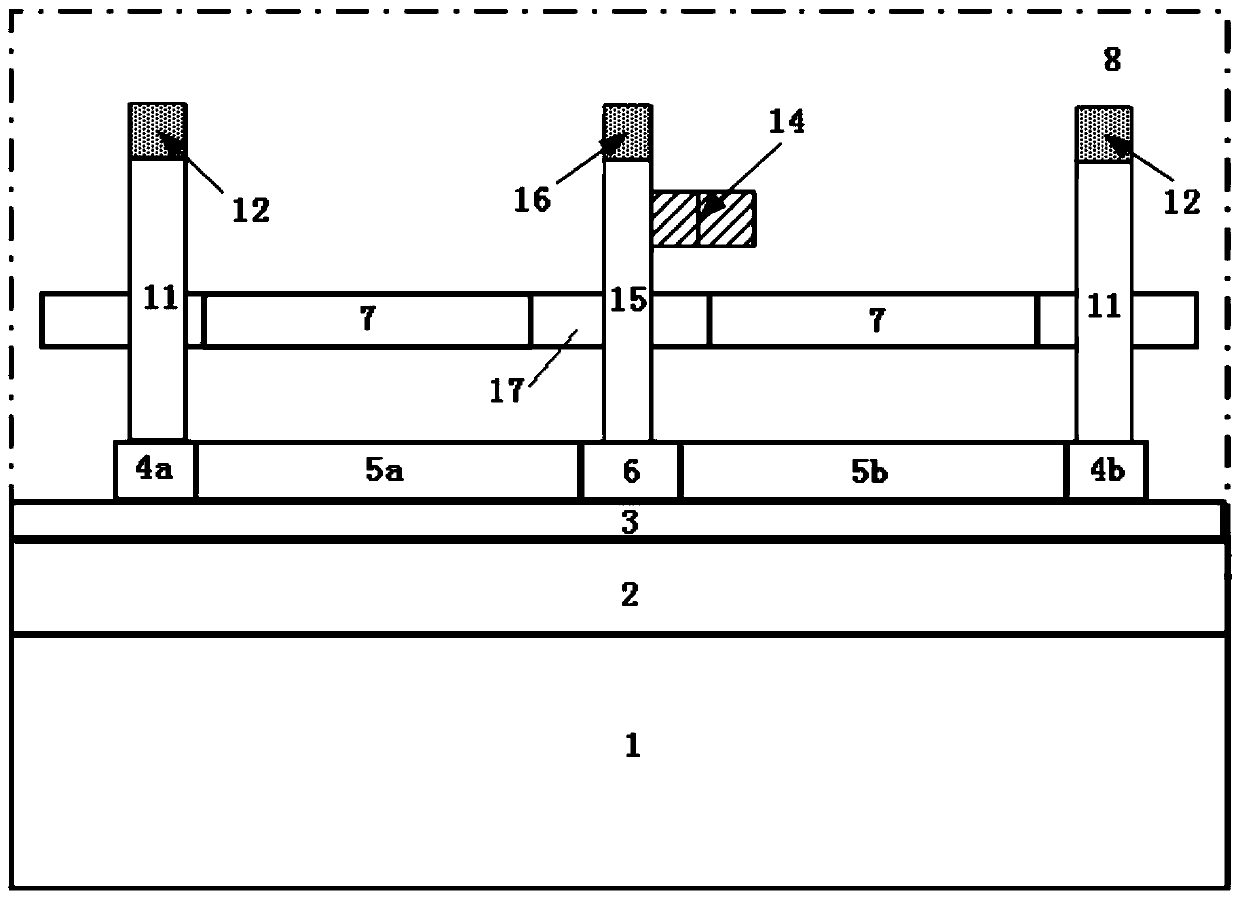

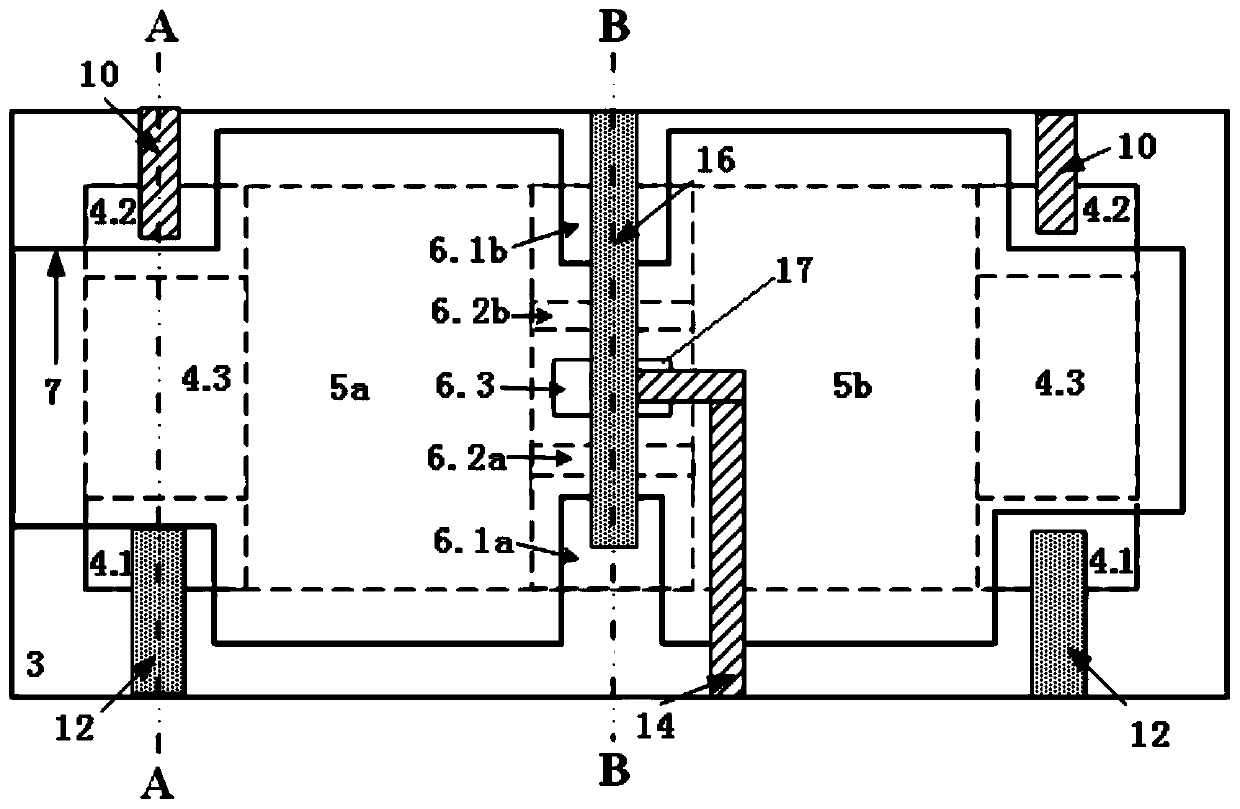

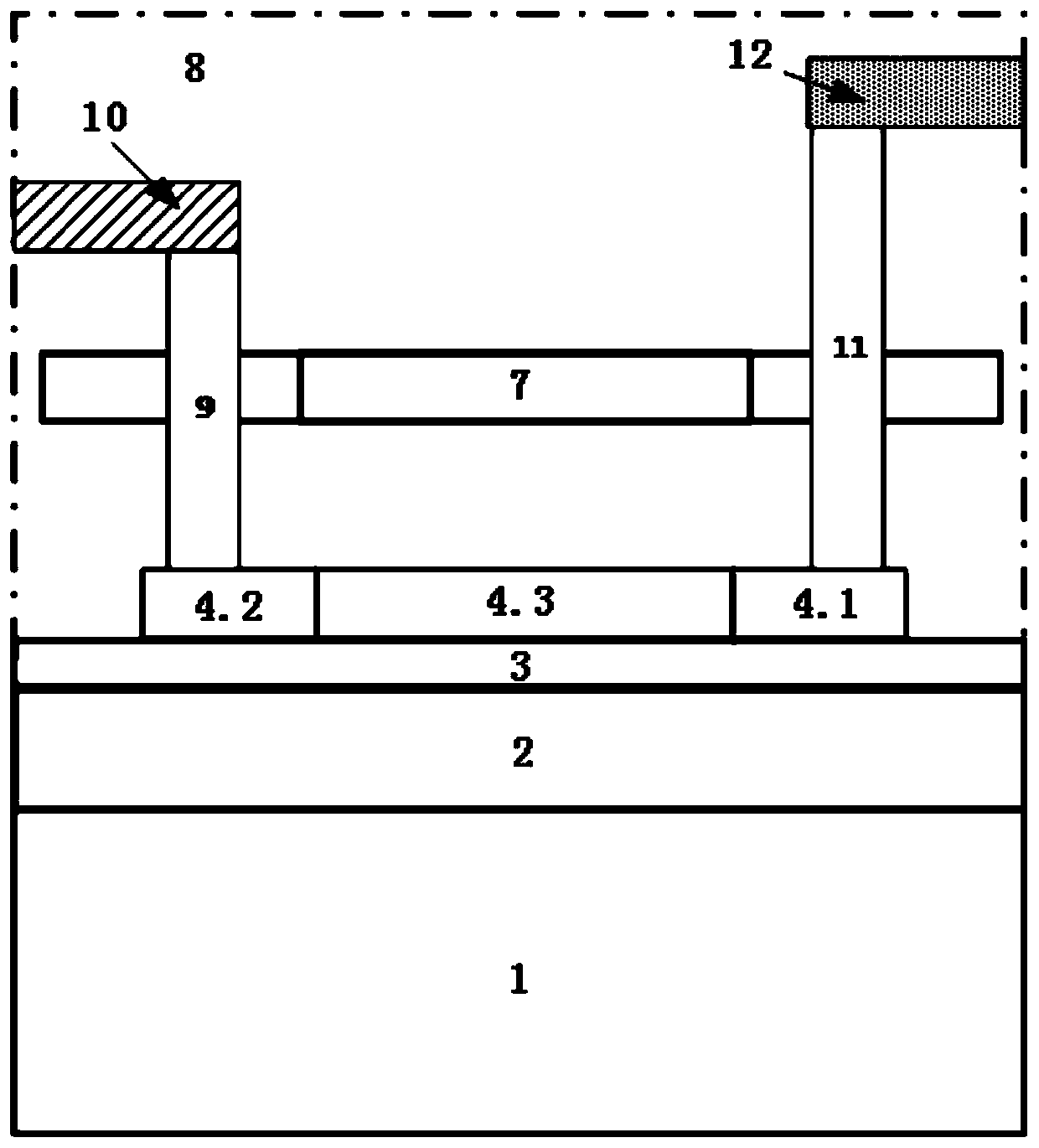

[0035] like figure 1As shown, the full-waveguide lateral polysilicon optical interconnection system based on the standard CMOS process of the present invention includes a P-Sub substrate 1, a shallow trench isolation (field oxygen) layer 2 and a gate oxide layer 3 arranged in sequence from bottom to top , the upper end surface of the gate oxide layer 3 is provided with SiO 2 isolation layer 8, the SiO 2 The isolation layer 8 is respectively embedded with: an optical interconnection layer located on the upper end of the gate oxide layer 3 and a metal light reflection plate 7 located above the optical interconnection layer, wherein the optical interconnection layer includes a The first polysilicon photodetector 4a, the first polysilicon optica...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More