High-speed high-precision comparator circuit design

A comparator circuit, high-precision technology, applied in CAD circuit design, instruments, calculations, etc., can solve the problems of increasing clock load and slowing down the comparator speed, so as to reduce clock load, improve driving ability, and equivalent input offset The effect of voltage reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings.

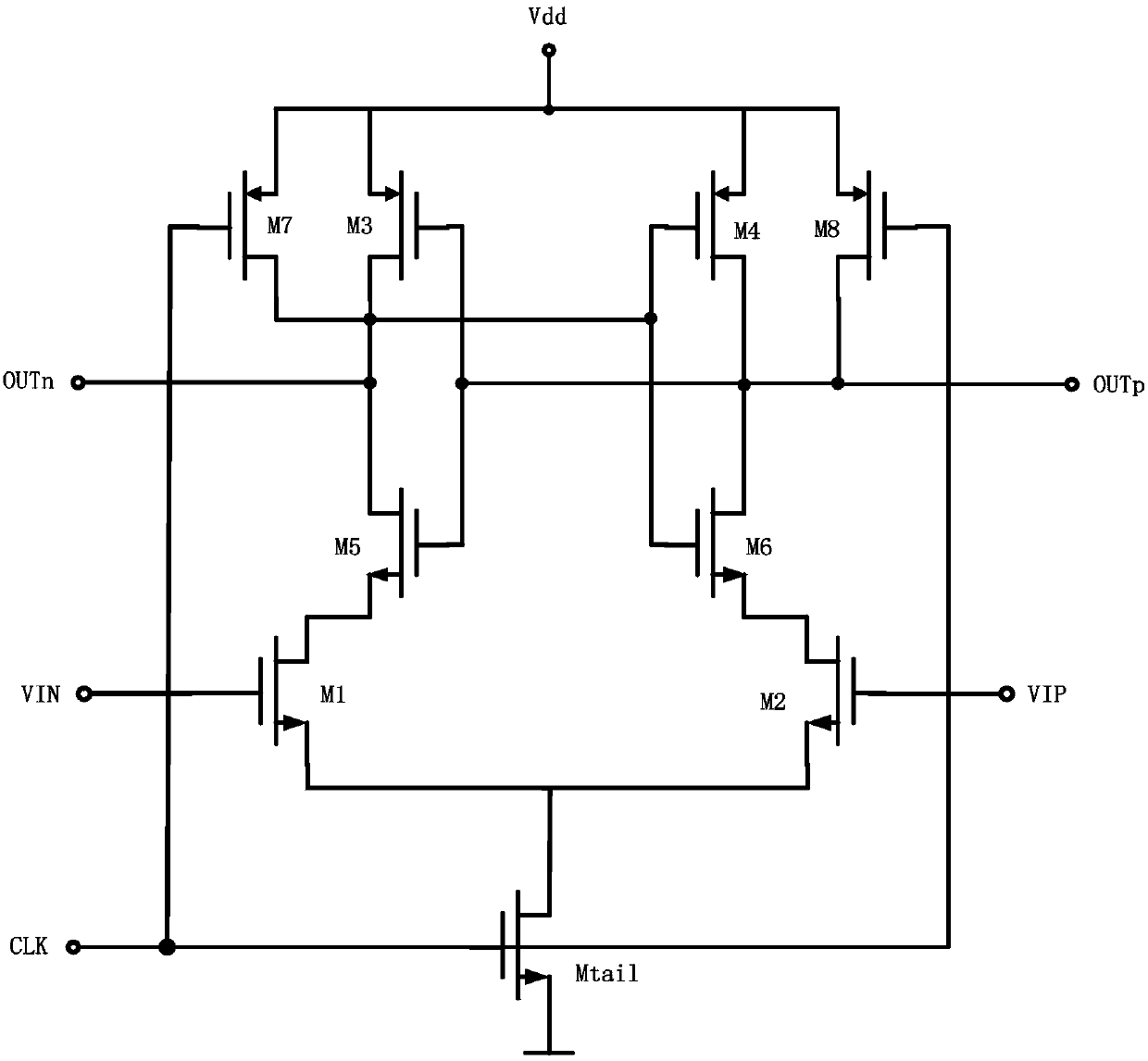

[0020] Such as figure 1 Shown is a traditional dynamic comparator, which mainly completes the reset and comparison processes of the comparator by the clock signal CLK. In the reset phase, the CLK signal is low level, the tail current tube Mtail is disconnected, and the power supply voltage Vdd pulls the output OUTp and OUTn to high level Vdd through the comparator reset tubes M7 and M8; in the comparison phase, the CLK signal is high level At this time, the reset tube is cut off, and the difference between the input signal VIN and VIP is quickly amplified by the positive feedback latch stage composed of M3-M5, and one end of the output is pulled down to a low level, and the other end is kept at a high level.

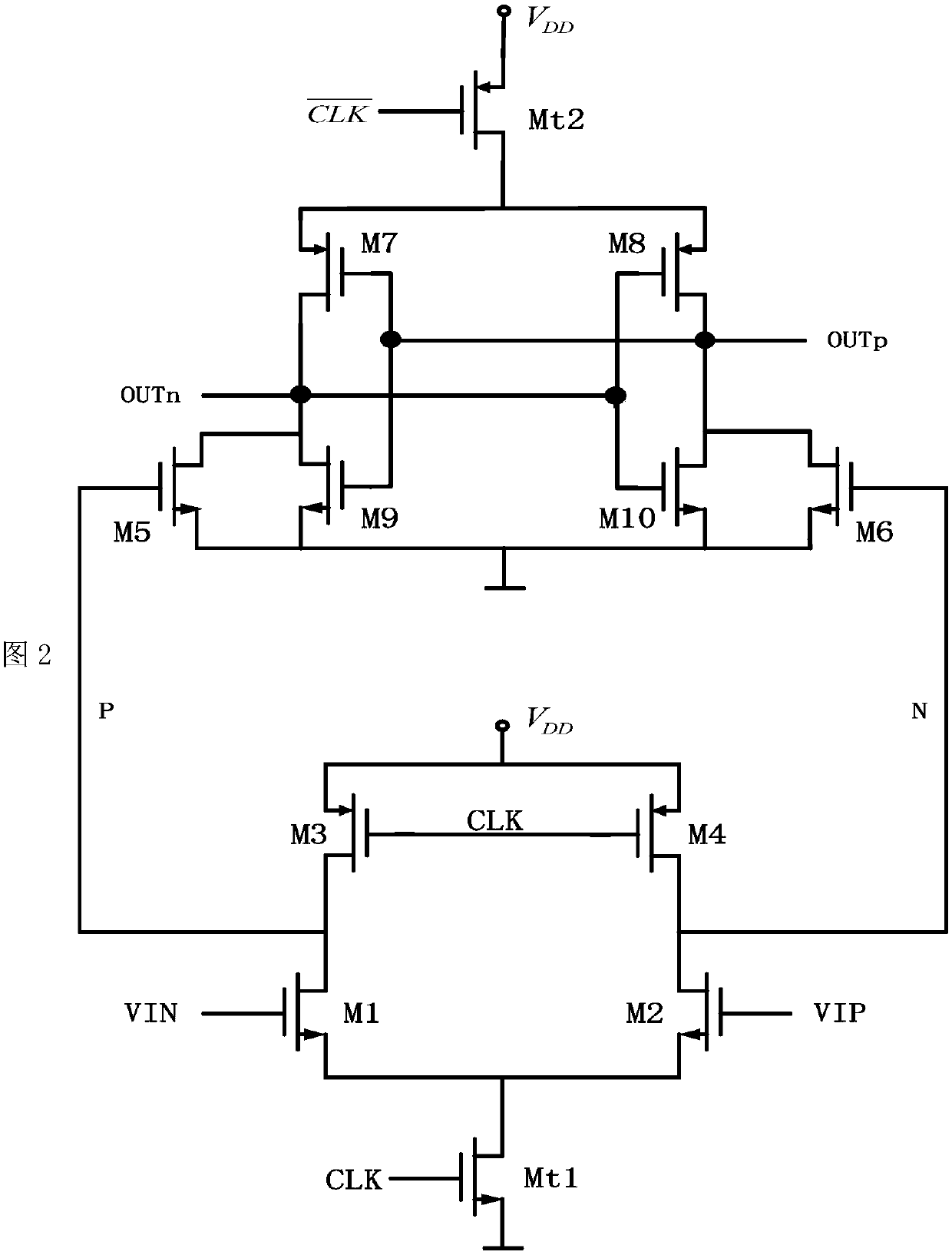

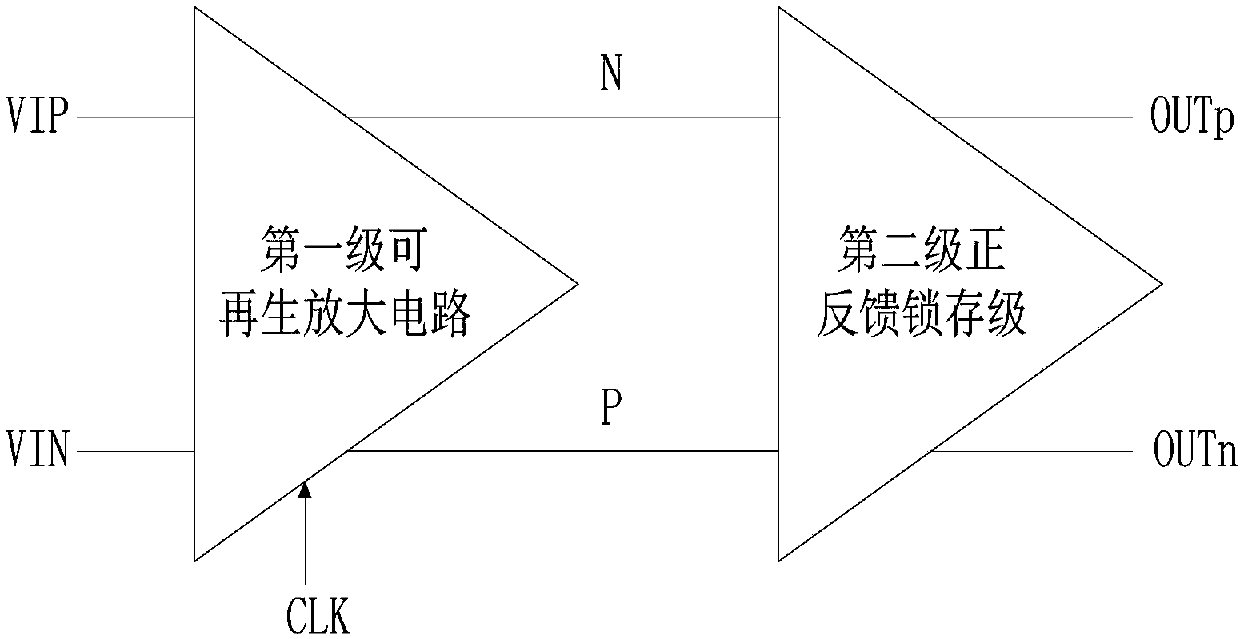

[0021] Such as figure 2 Shown is a second-order dynamic comparator, which mainly includes a preamplifier and a positive feedback latch stage with a reset term...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More