DSP data memory active fault-tolerant method and device

A data memory and processor technology, applied in the field of microelectronics, can solve the problems of memory error accumulation effect, large memory access delay, instruction waste, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0074] The present invention will be further described in detail below in conjunction with specific embodiments, which are to explain but not limit the present invention.

[0075] The DSP processor data memory fault tolerance device and method provided by the present invention are oriented to the field of high-reliability processor design, and provide hardware structural support and software solution methods for application-oriented processor reliability design.

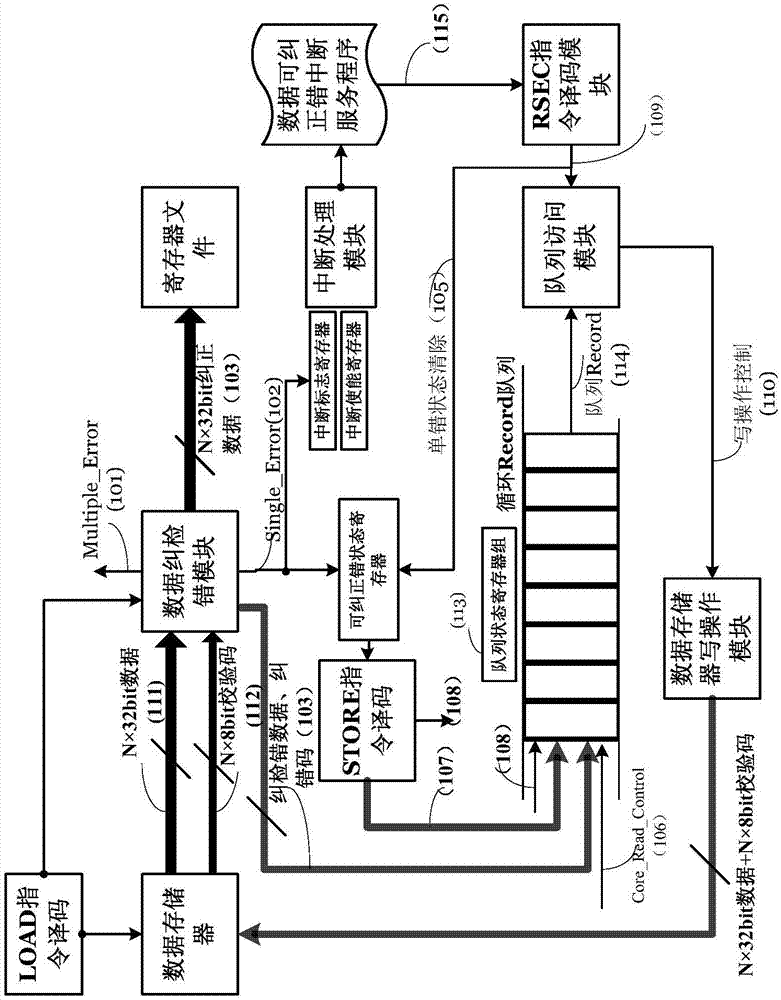

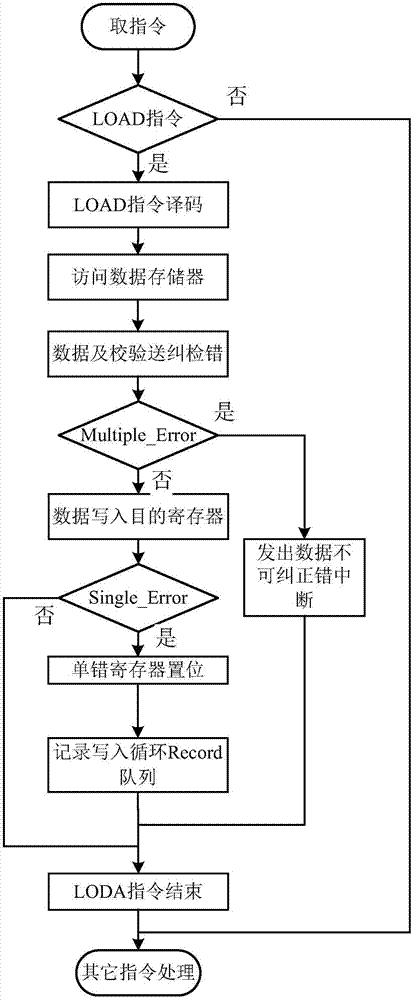

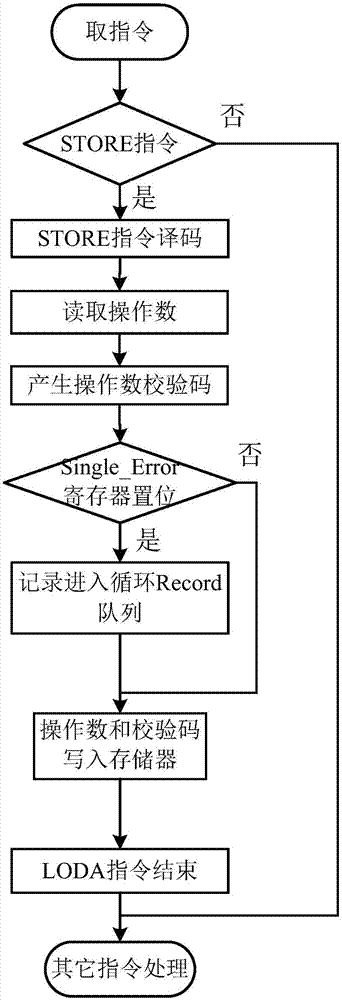

[0076] The DSP processor data memory active fault-tolerant device of the present invention is a circuit arranged between the DSP processor core pipeline and the data memory in the core and used for the active fault-tolerant refresh of the data memory. The active fault-tolerant device includes the following circuit modules: LOAD instruction decoding for loading data memory, STORE instruction decoding for writing data memory, queue access module, queue access write-back instruction decoding module (RSEC instruction decoding ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More