Automatic chip simulation and verification system

A chip system, simulation and verification technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of time-consuming, labor-intensive, time-consuming and labor-intensive, and low degree of automation, and achieve high efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

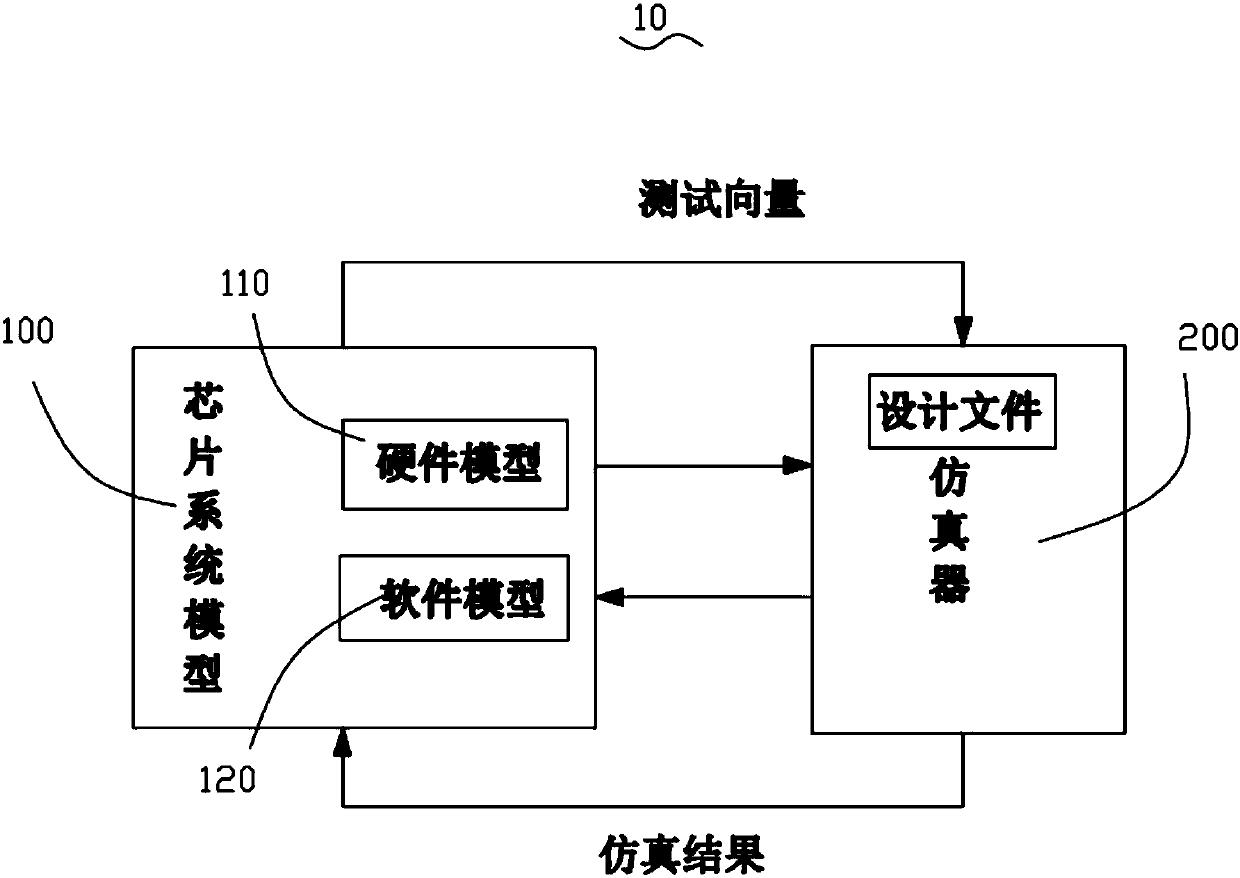

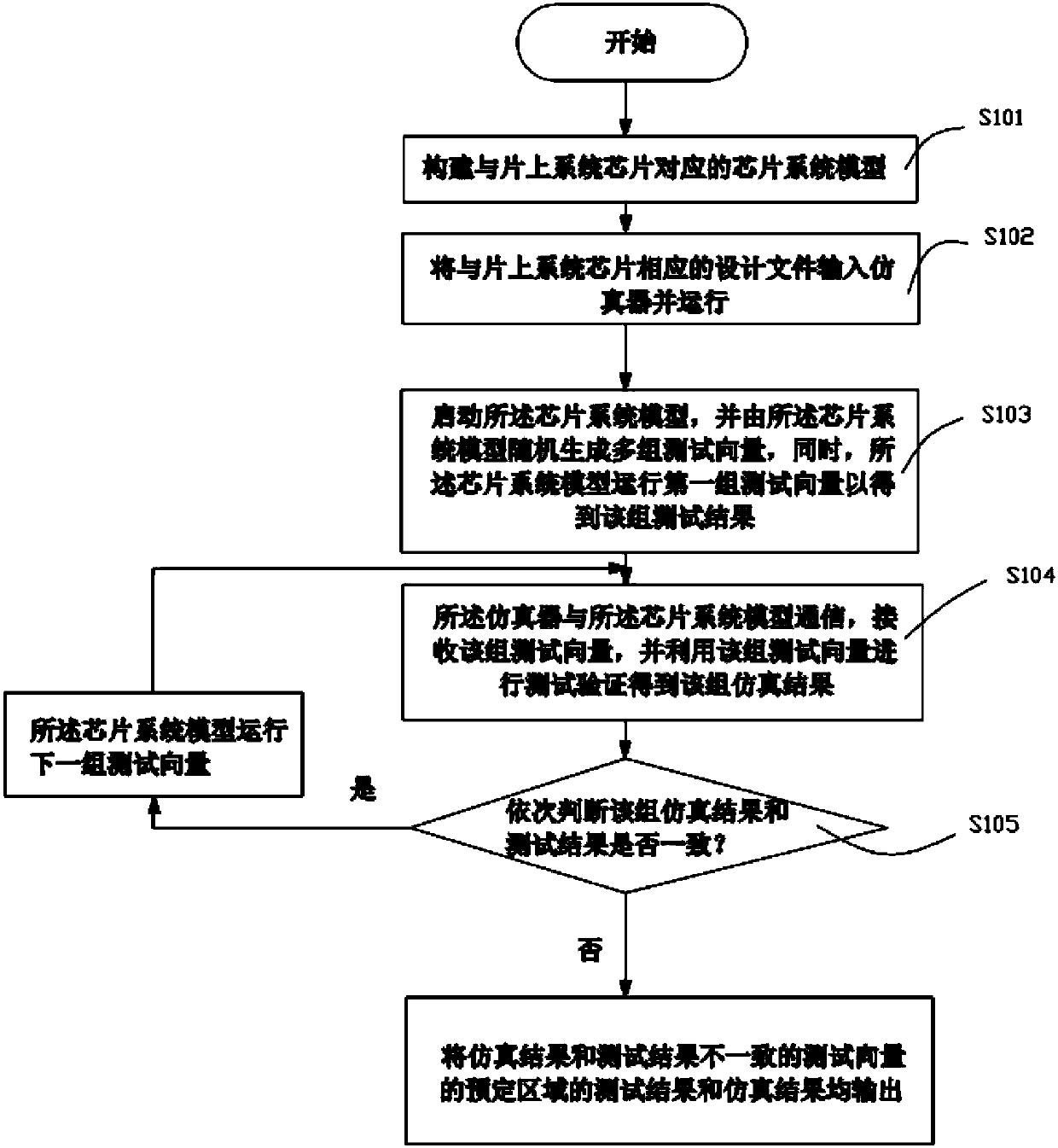

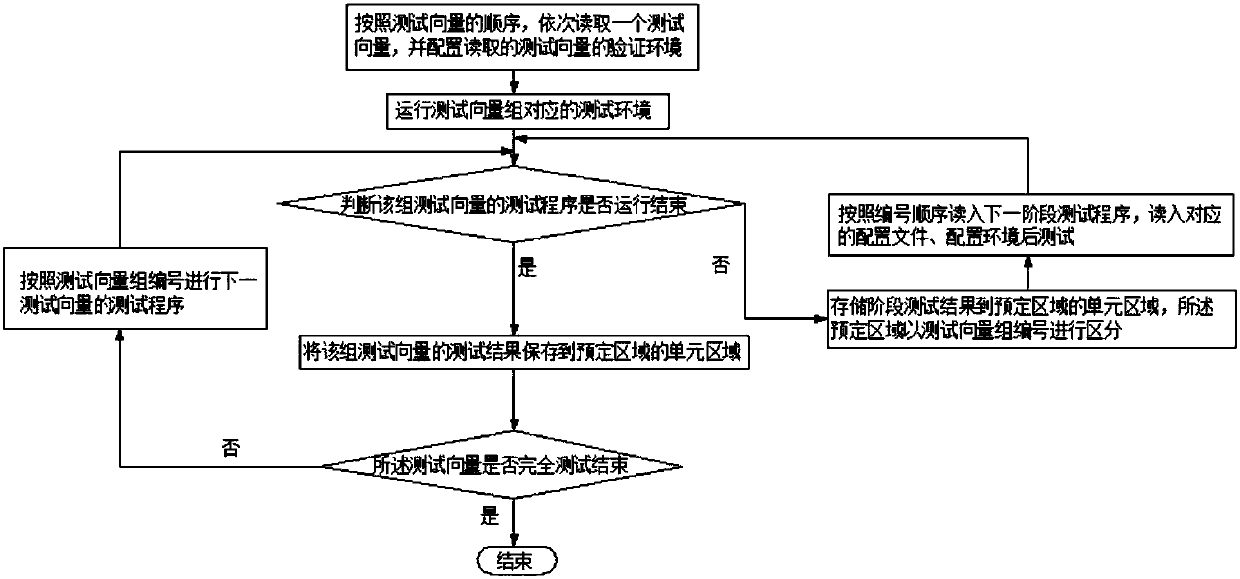

[0030] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0031] Schematic diagram of the SoC development process. The system-on-chip needs to go through the following main stages from the initial requirements to the final product: functional design, design description and behavior-level verification, logic synthesis, gate-level verification, layout and wiring, etc. The purpose of verification (verification) is to confirm that the functional correctness and performance (speed and power consumption, etc....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More