Semiconductor transistor preparation method and structure

A semiconductor and transistor technology is applied in the field of preparation method and structure of semiconductor transistors to achieve the effects of improving stability and reliability, reducing resistance-capacitance delay, and reducing parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

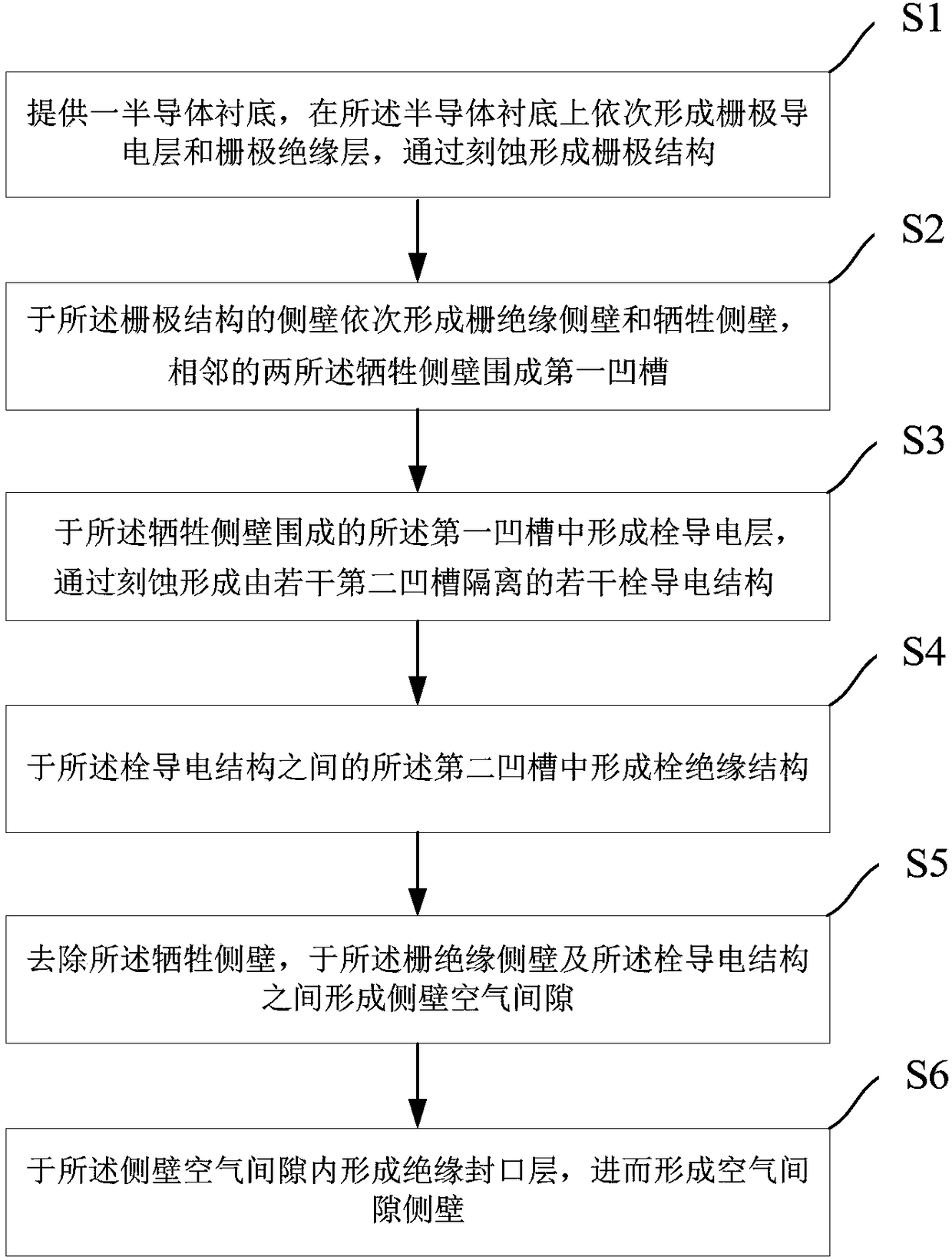

[0115] Such as Figure 2 to Figure 17 As shown, in order to effectively reduce the parasitic capacitance between the gate and the plug conductive structure, reduce the resistance-capacitance delay, increase the switching speed, and reduce the switching energy, this embodiment provides a method for preparing a semiconductor transistor structure. The semiconductor transistor structure The preparation method comprises the following steps at least:

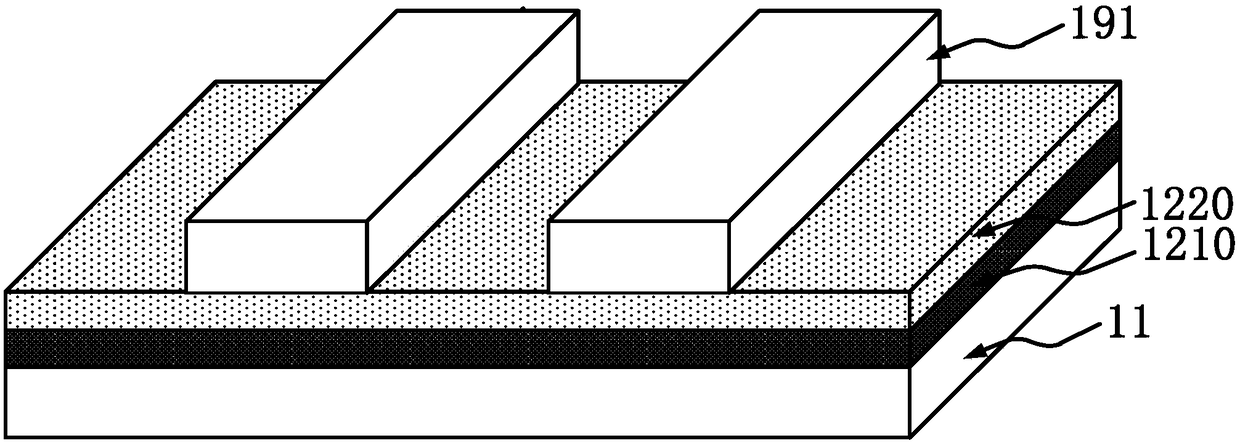

[0116] Step S1 is executed to provide a semiconductor substrate 11 on which a gate conductive layer 121 and a gate insulating layer 122 are sequentially formed, and a gate structure is formed by etching.

[0117] Specifically, such as image 3 As shown, in this embodiment, the semiconductor substrate 11 adopts a silicon substrate; an oxide layer (not shown in the figure) is oxidized on the silicon substrate as a dielectric layer of the gate structure, with a thickness of Between 1 nanometer and 10 nanometers; using physical vapor de...

Embodiment 2

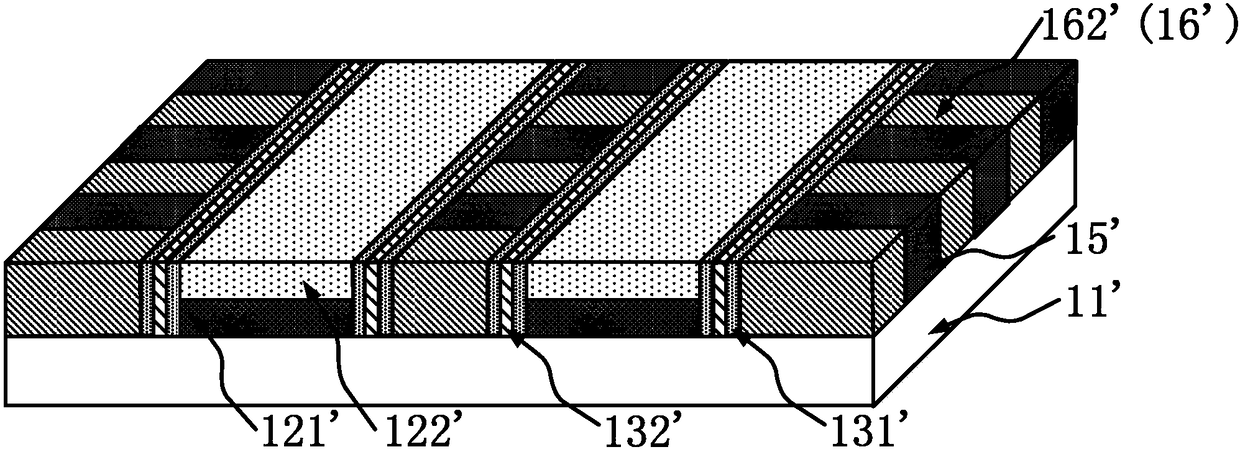

[0153] Such as Figure 2 to Figure 13 with Figure 18 ~ Figure 22 As shown, this embodiment provides a method for preparing a semiconductor transistor structure, and the method for preparing a semiconductor transistor structure at least includes the following steps:

[0154] Step S1 is executed to provide a semiconductor substrate 11 on which a gate conductive layer 121 and a gate insulating layer 122 are sequentially formed, and a gate structure is formed by etching.

[0155] Executing step S2 , forming gate insulating sidewalls 13 and sacrificial sidewalls 140 on the sidewalls of the gate structure in sequence, and two adjacent sacrificial sidewalls 140 enclose a first groove 151 .

[0156] Step S3 is executed, forming a plug conductive layer 150 in the first groove 151 surrounded by the sacrificial sidewall 140 , and forming a plurality of plug conductive structures 15 isolated by a plurality of second grooves 161 by etching.

[0157] The specific implementation manners o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More