Multi-mode POR circuit for FPGA

A multi-mode and circuit technology, applied in the field of FPGA, can solve the problems that POR circuits cannot meet the delay requirements, and achieve the effects of simple design, flexible application, and reduced dynamic power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

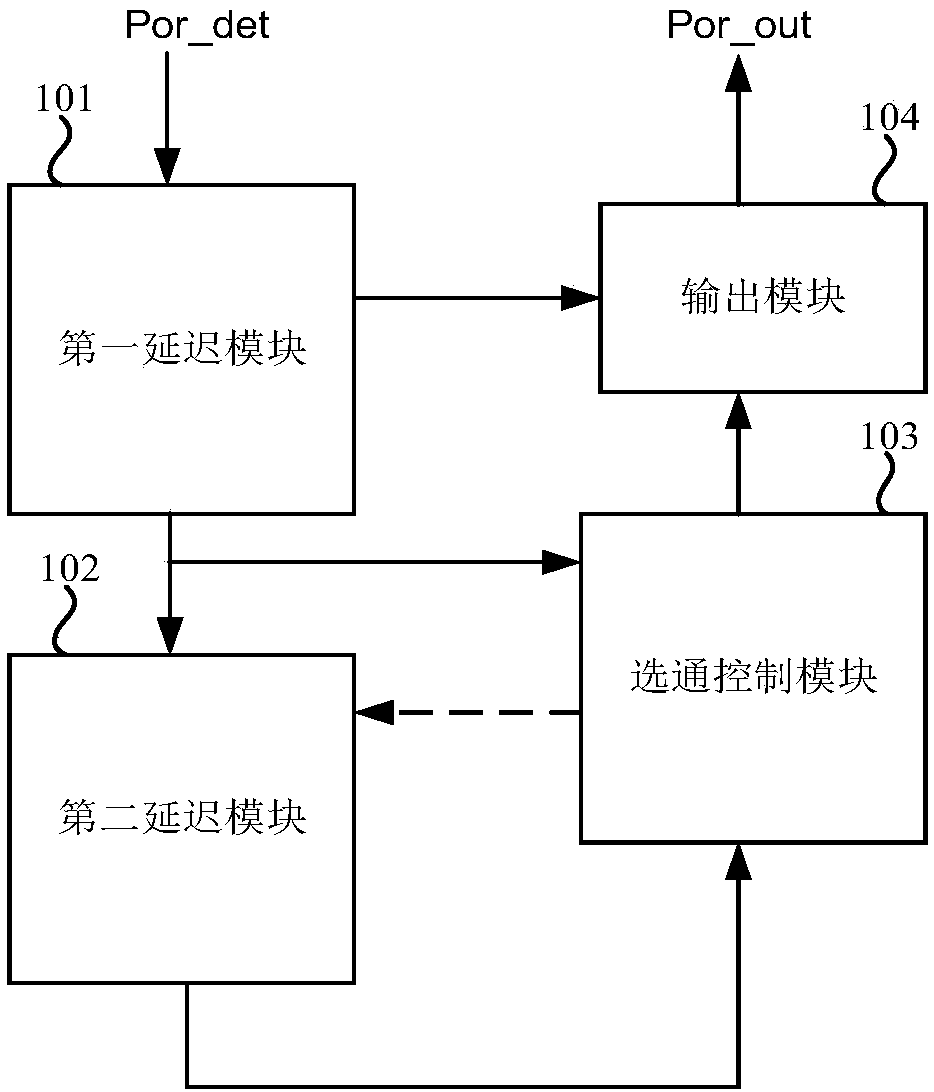

[0039] See figure 1 , figure 1 A schematic diagram of a multi-mode POR circuit for FPGA provided by an embodiment of the present invention, including: a first delay module 101, a second delay module 102, a gating control module 103 and an output module 104; wherein,

[0040] The first output end of the first delay module 101 is electrically connected to the second delay module 102 and the gating control module 103 respectively, and the second output end of the first delay module 101 is electrically connected to the output module 104 The second delay module 102 is electrically connected to the gating control module 103; the gating control module 103 is electrically connected to the output module 104.

[0041] Specifically, the delay length of the second delay module 102 is greater than the delay length of the first delay module 101 .

[0042] Preferably, the first delay module 101 is a microsecond-level delay circuit; the second delay module 102 is a millisecond-level D flip-...

Embodiment 2

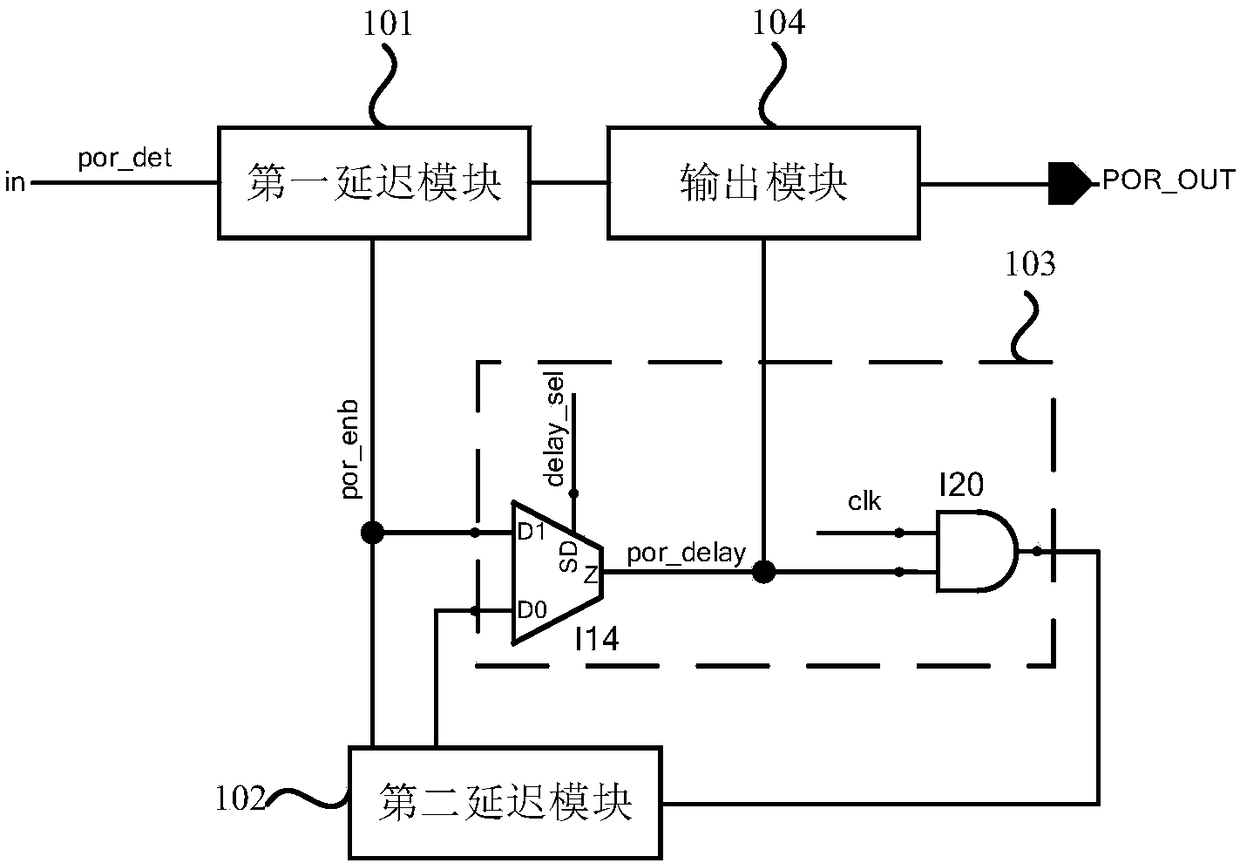

[0045] In order to facilitate the understanding of the working principle of the present invention, this embodiment describes in detail the optimized structure of the gating control module of the POR circuit on the basis of the above embodiments.

[0046] Specifically, see figure 2 , figure 2 A schematic diagram of a gating control module circuit structure provided by an embodiment of the present invention, the gating control module 103 may include a one-two selector I14; wherein, the first input terminal D1 of the one-two selector I14 is electrically Connect the first output terminal of the first delay module 101, the second input terminal D0 of the two-choice selector I14 is electrically connected to the output terminal of the second delay module 102; the two-choice selector I14 The output terminal Z is electrically connected to the output module 104 .

[0047] Further, the gate control module 103 also includes an AND gate I20; wherein, the first input end of the AND gate...

Embodiment 3

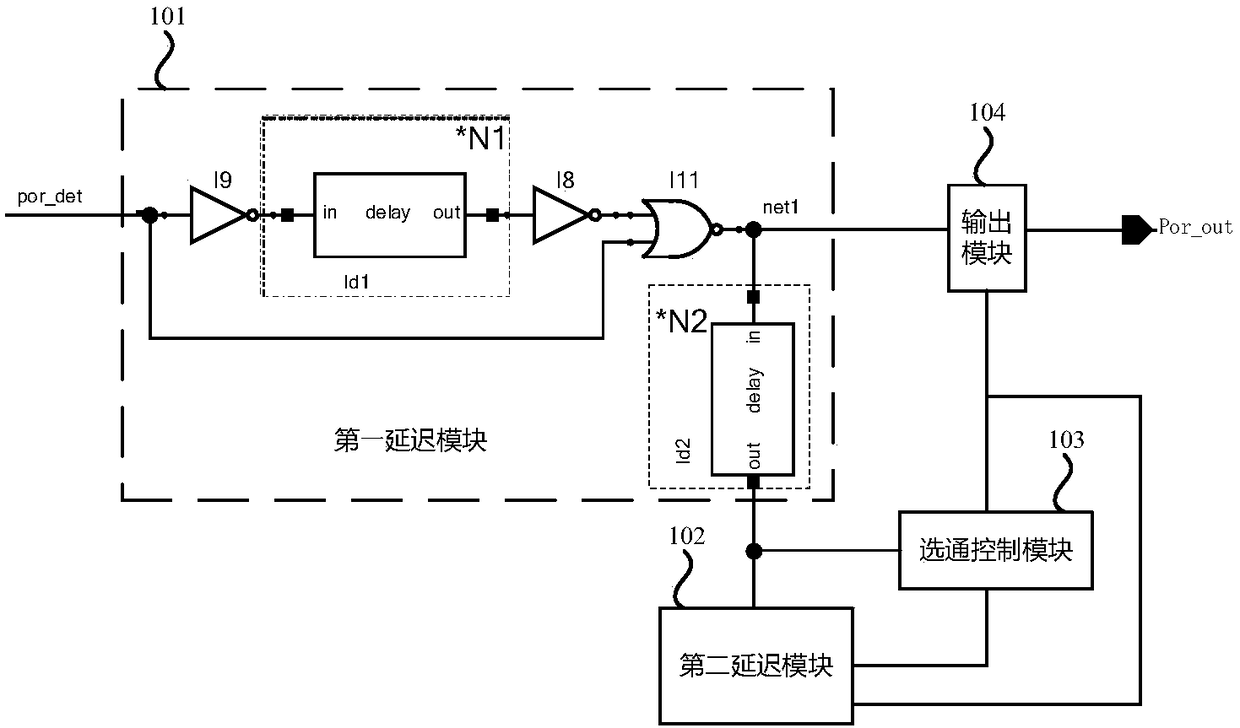

[0051] In order to facilitate the understanding of the working principle of the present invention, this embodiment describes in detail the optimized structure of the first delay module of the POR circuit on the basis of the above embodiments.

[0052] Specifically, see image 3 , image 3 The first delay module circuit structure schematic diagram provided for the embodiment of the present invention includes: a first inverter I9, a first delay unit Id1, a second inverter I8, a first NOR gate I11 and a second delay unit Id2; in,

[0053] The first inverter I9, the first delay unit Id1, and the second inverter I8 are sequentially connected in series to an input end of the first NOR gate I11, and the first NOR gate I11 The other input end of the first inverter I9 is electrically connected to the input end of the multi-mode POR circuit, and the output end of the first NOR gate I11 is electrically connected to the second delay unit Id2 and the The output module 104; the second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More