Low Latency Polar Code Decoder

A polar code and low-latency technology, applied in the field of fast computing, can solve problems such as consumption, and achieve the effects of improving throughput, shortening computing unit paths, and improving hardware efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] The present invention will be further described below in conjunction with accompanying drawing.

[0010] In the existing literature, formula (1) in polar code decoding algorithm can be simplified to formula (2)

[0011] d=a+ln[(1+e b+c ) / (e b +e c )] (1)

[0012] d=a+Sign(b)*Sign(c)*g(b,c) (2)

[0013] Among them, g(b,c)=s*Min(|b|,|c|). a, b and c are the input data of the calculation unit of mode 1,

[0014] And it is expressed in the form of sign bit (Sign) and absolute value (Mag) separation; s=0.9375 is the multiplication correction factor introduced, which is used to reduce the approximation error to the original nonlinear function expression (1), which can be passed on the hardware A shift-subtractor implementation. Min(|b|,|c|) means finding the smaller value between two absolute values |b| and |c|.

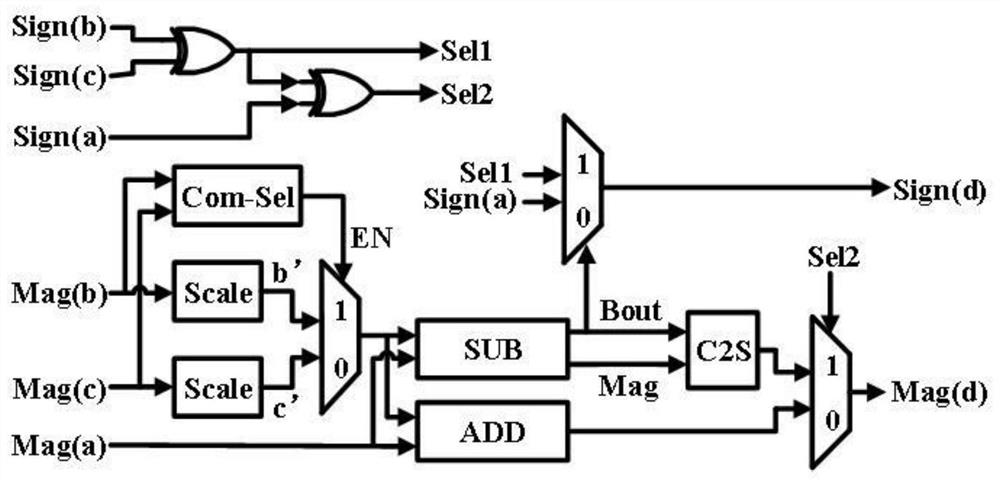

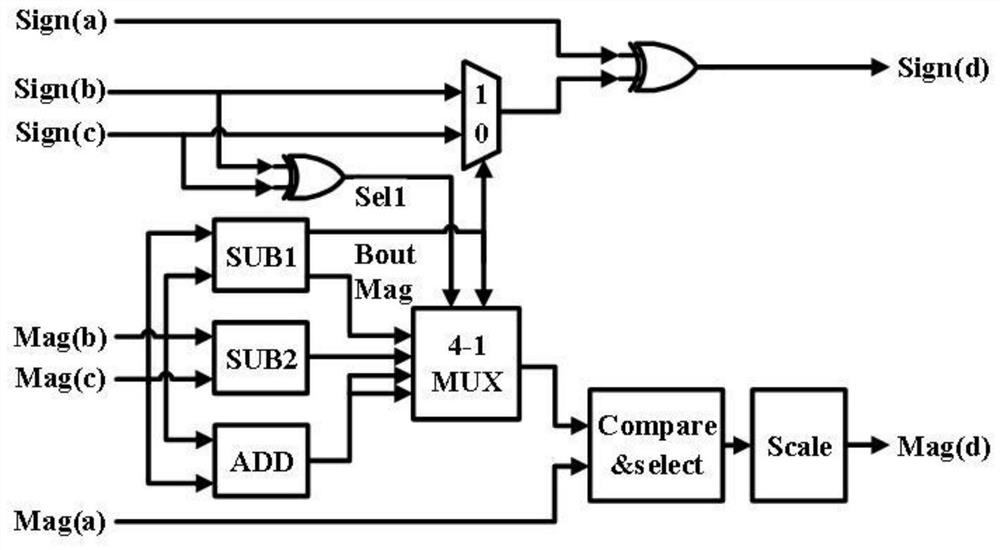

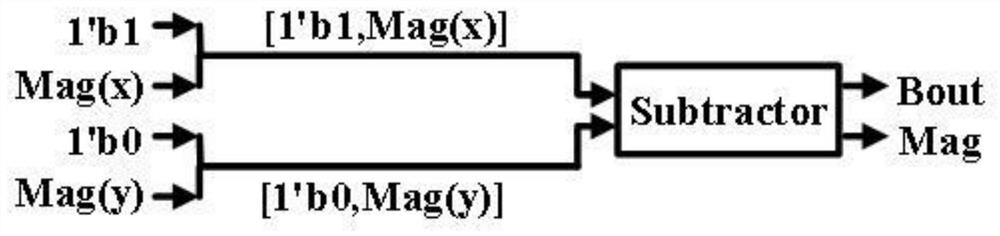

[0015] The calculation unit structure designed by the present invention for formula (2) is as follows figure 1 As shown, the steps of the entire calculat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com