Automatic Generation Method of Customizable Logic Device Layout and Netlist

A technology for automatically generating and customizing logic, applied in the fields of instrumentation, computing, electrical and digital data processing, etc., can solve the problems of not supporting user customization, spending a lot of repetitive time, and unfavorably seizing the market, reducing a lot of workload and facilitating structural analysis. , the effect of easy to market quickly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present disclosure provides a method for automatically generating a customizable logic device layout and netlist, which supports user customization, and is simple in operation, fast in speed, capable of batch processing, and strong in scalability, helping to reduce back-end The large workload of the layout personnel facilitates the structural analysis of the software engineers, and facilitates the rapid launch of the chips and seizes the market.

[0033] In order to make the purpose, technical solutions and advantages of the present disclosure clearer, the present disclosure will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

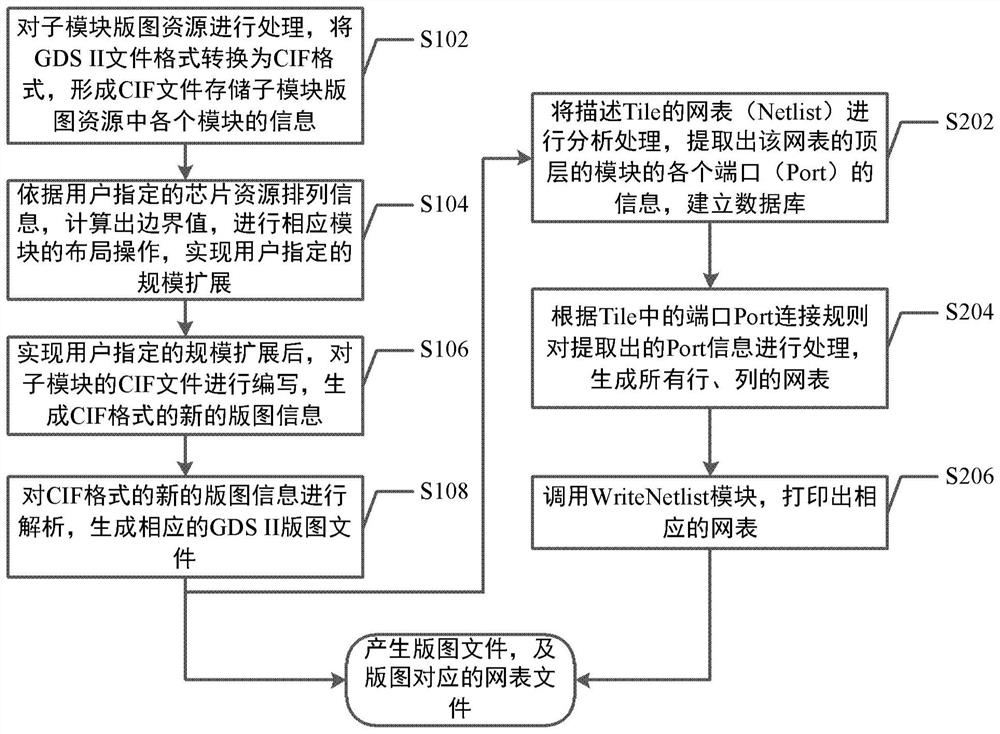

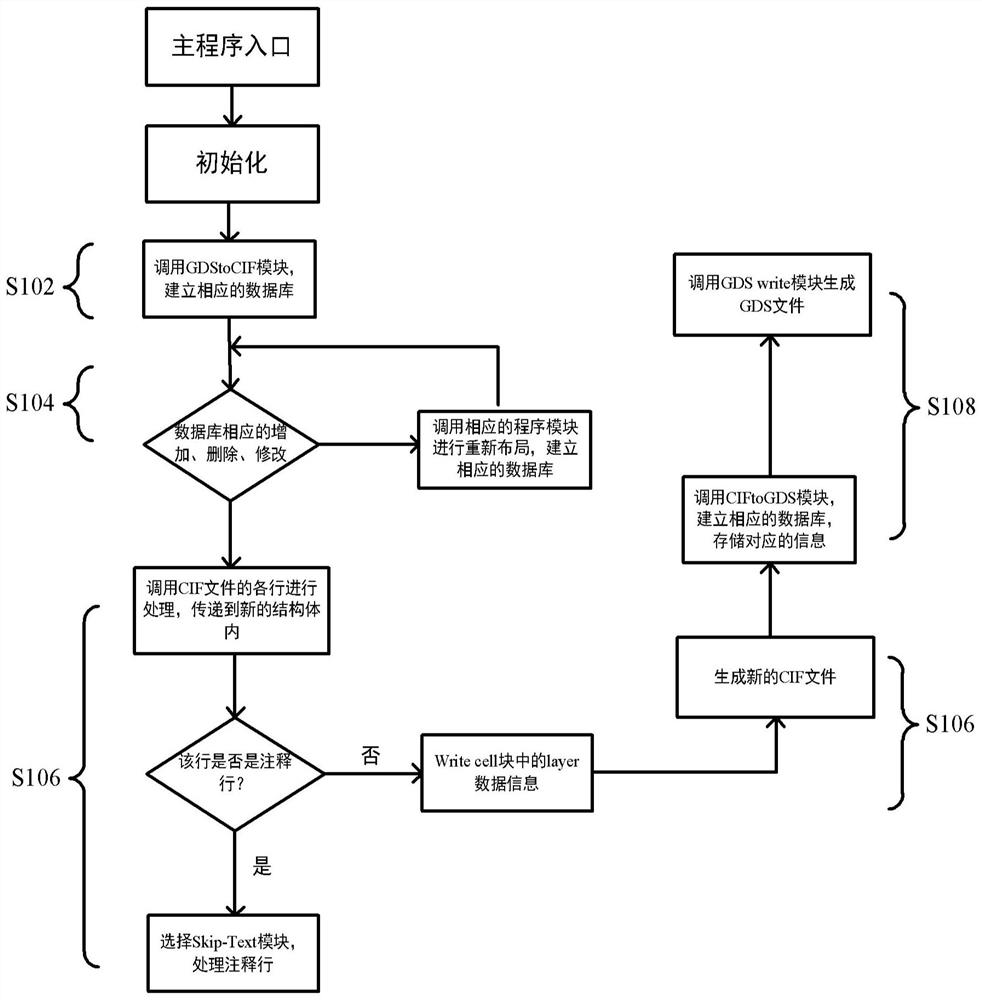

[0034] In a first exemplary embodiment of the present disclosure, a method for automatically generating a customizable logic device layout and netlist is provided.

[0035] figure 1 It is a flowchart of a method for automatically generating a layout of a customiz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More