Fin field effect transistor and method of forming the same

A technology of fin field effect transistors and fins, which is applied to semiconductor devices, electrical components, circuits, etc., can solve problems affecting the electrical performance of FinFET devices, achieve the effect of improving self-heating effects and improving electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The electrical performance of the fin field effect transistor formed according to the background technology needs to be improved.

[0035] The reason why the electrical performance of the FinFET needs to be improved is analyzed in conjunction with a FinFET.

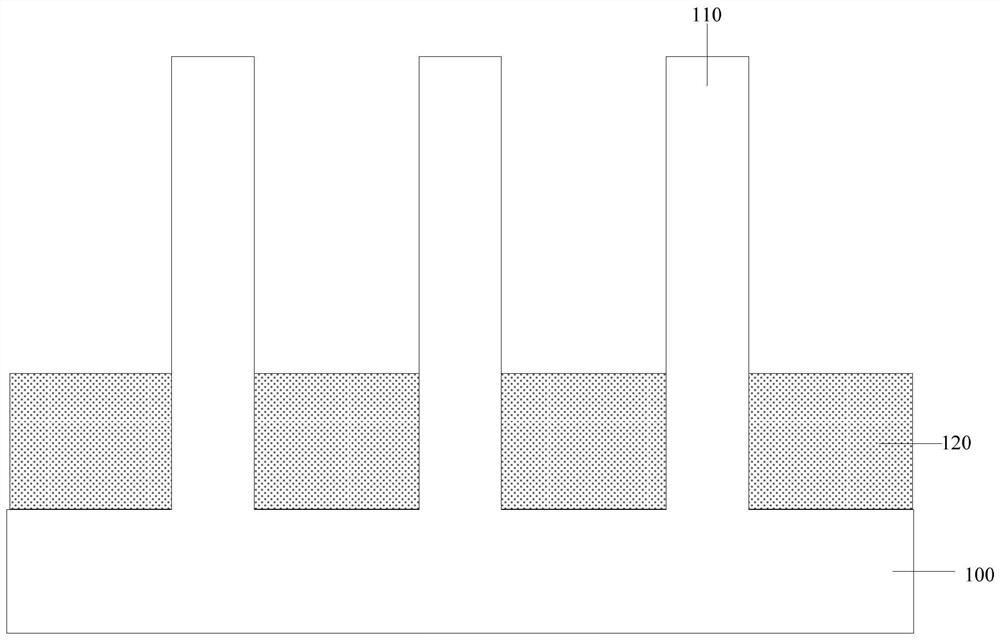

[0036] refer to figure 1 , figure 1 It is a schematic cross-sectional structure diagram of a fin field effect transistor, which includes: a substrate 100 ; and a plurality of fins 110 protruding from the substrate 100 . The isolation structure 120 is located on the substrate 100 exposed by the fin 110 , the isolation structure 120 covers part of the sidewall surface of the fin 110 , and the top of the isolation structure 120 is lower than the top of the fin 110 . across the gate structure (not shown) on the fin portion 110 .

[0037] When the above-mentioned FinFET is in operation, there will be a problem of self-heating effect, thereby reducing the electrical performance of the FinFET.

[0038]After analysis, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More