Cellular neural network hardware architecture optimization method

A neural network and hardware architecture technology, applied in biological neural network models, physical implementation, etc., can solve the problems of redundant computing performance, slow memory reading, lack of reconfigurable design space exploration, etc., to achieve optimal computing performance, The effect of memory bandwidth reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described below in conjunction with the accompanying drawings.

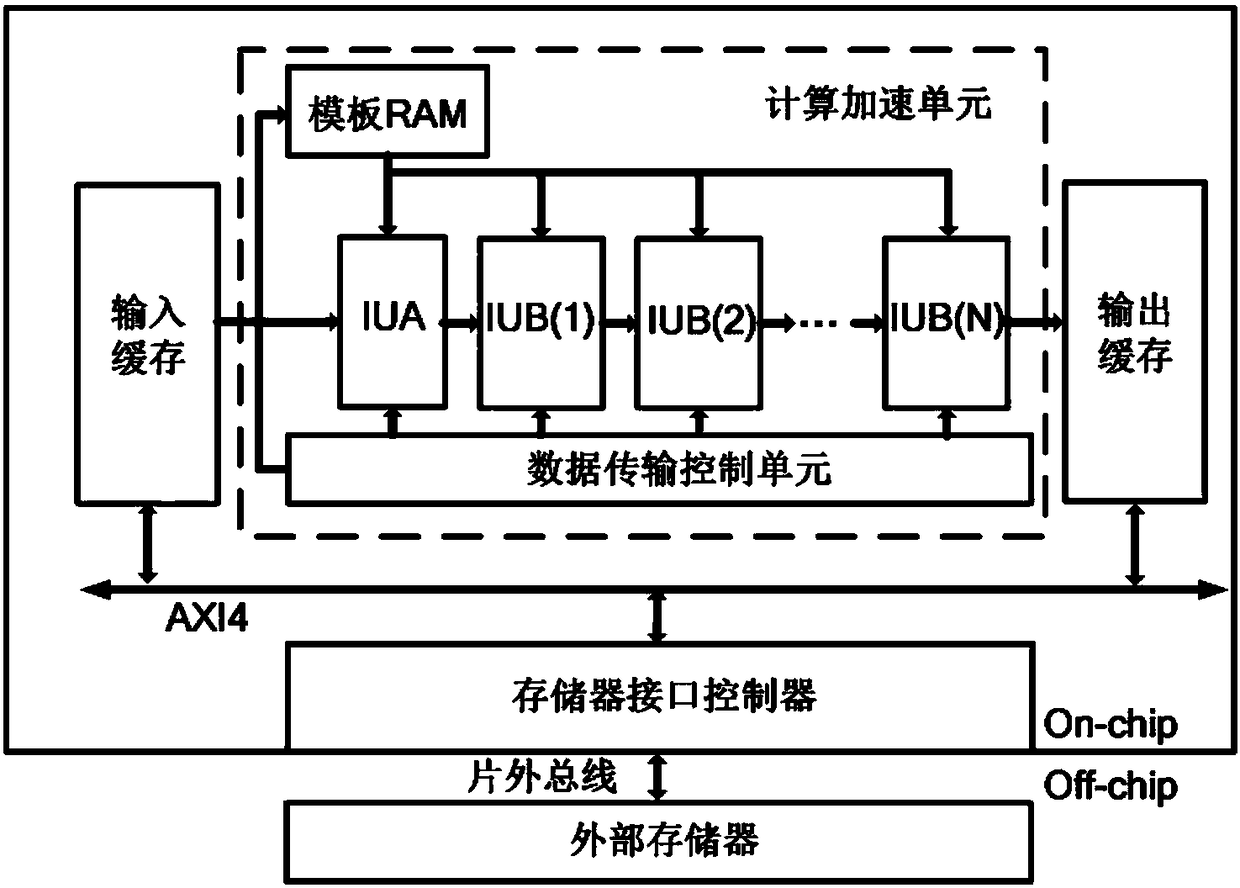

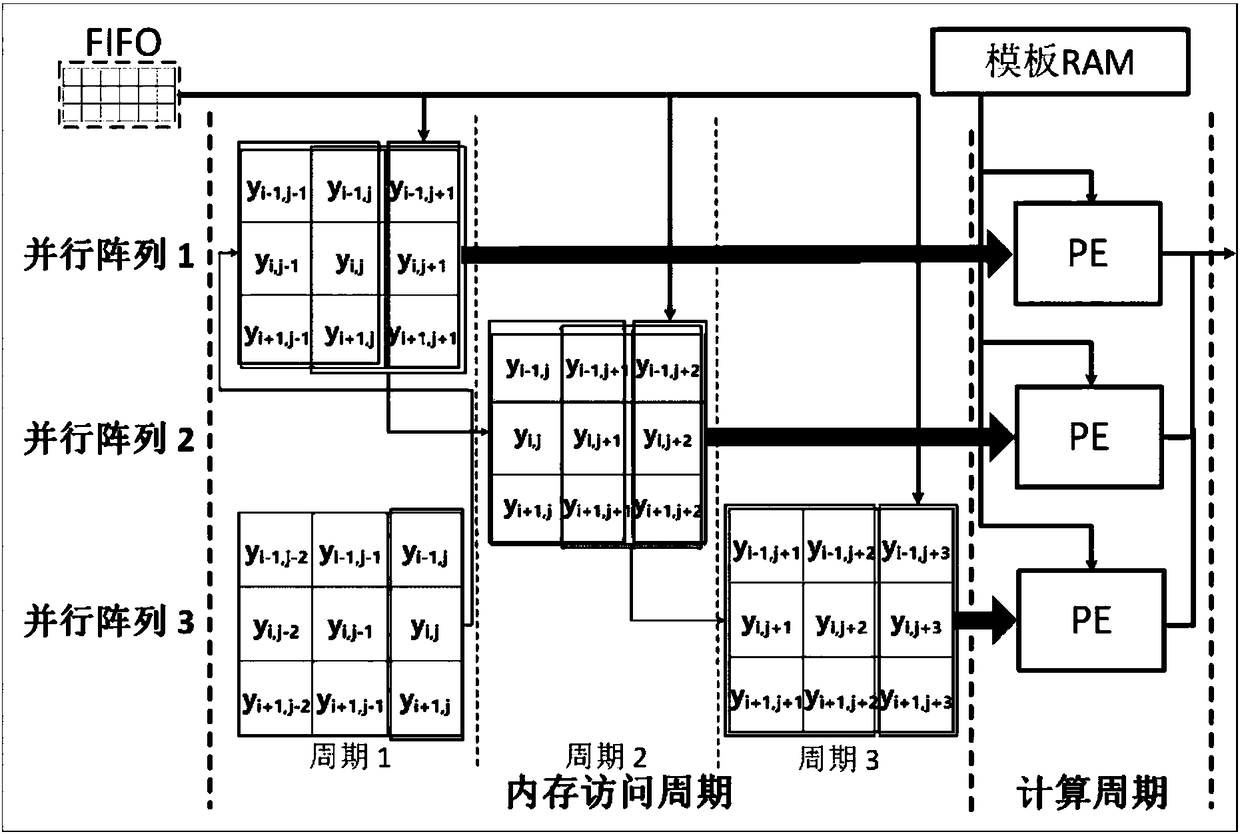

[0044] Such as figure 1 As shown, the cellular neural network hardware architecture is composed of external memory, memory interface controller, on-chip input cache, on-chip output cache, computing acceleration unit and AXI4 bus. Due to the limited on-chip storage resources, the data is first read from the external memory into the on-chip input buffer through the memory interface controller and the AXI4 bus, and the calculation operation is performed in the computing acceleration unit. The calculation acceleration unit includes a template RAM, a data transmission control unit, an iterative unit A and several iterative units B connected in sequence, and the operation of the entire cellular neural network is completed through the iterative unit pipeline. The details are as follows:

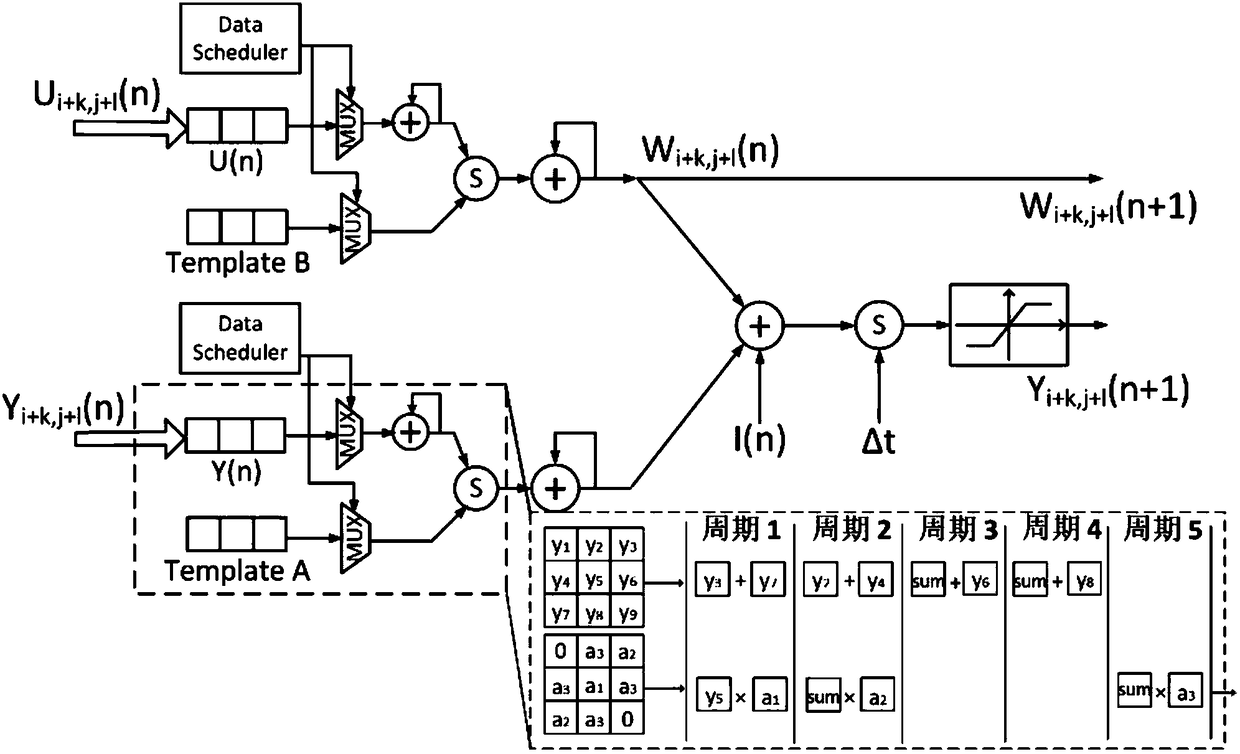

[0045] Iteration unit A (IU A): perform the initial calculation operation in the iterativ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More