Semiconductor structure and formation method thereof

A semiconductor and transistor area technology, applied in the field of semiconductor structure and its formation, can solve the problems affecting the performance of semiconductor structure, etc., and achieve the effects of reducing leakage current, high quality, and convenient process operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The wafer test structure of the present invention will be described in more detail below in conjunction with schematic diagrams, wherein a preferred embodiment of the present invention is represented, it should be understood that those skilled in the art can modify the present invention described here, and still realize the beneficial effects of the present invention . Therefore, the following description should be understood as the broad knowledge of those skilled in the art, but not as a limitation of the present invention.

[0033] There are many problems in the formation method of the semiconductor structure, and it is difficult to guarantee the stable performance of the formed semiconductor structure.

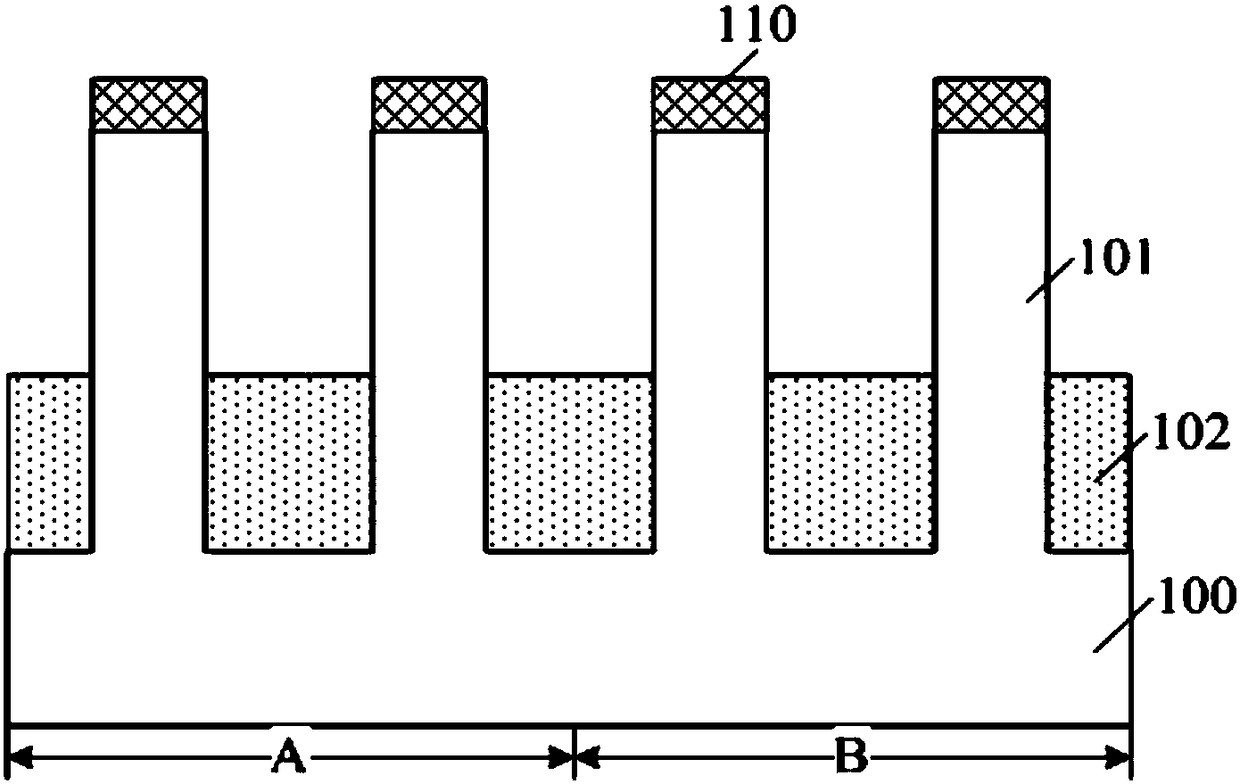

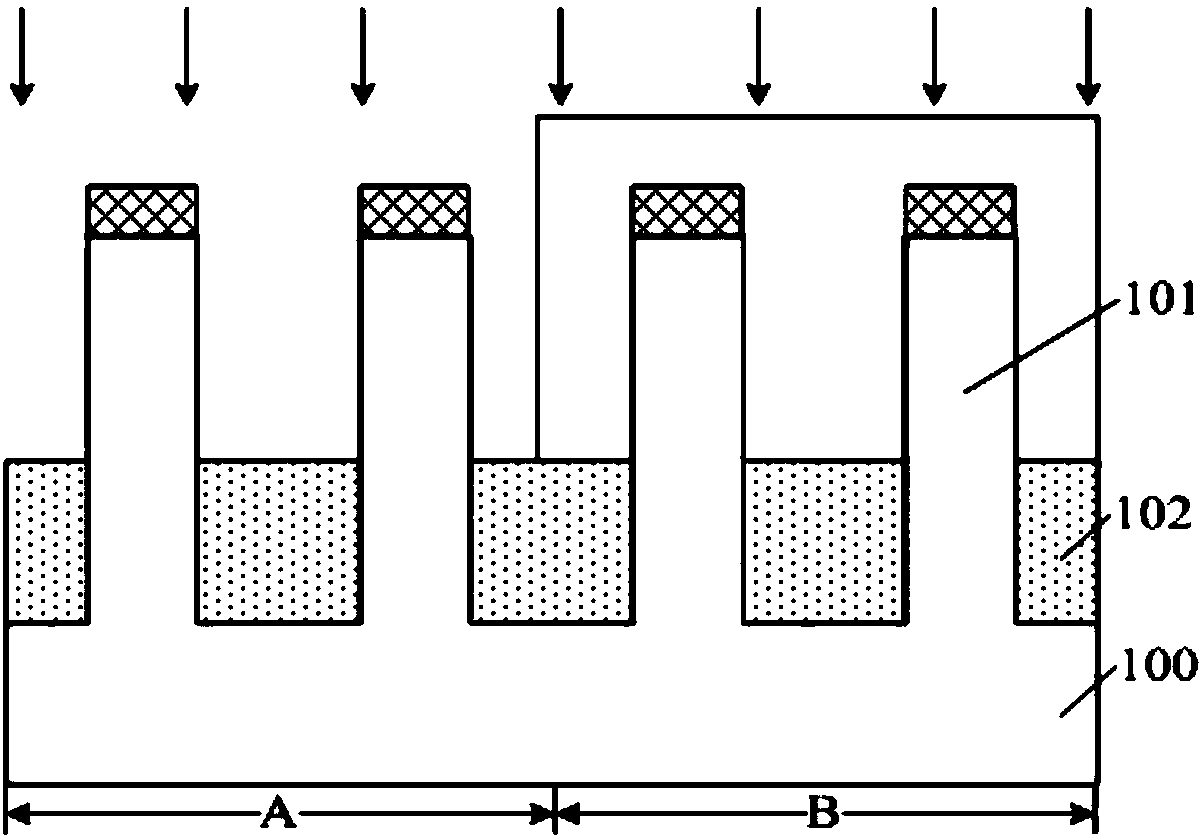

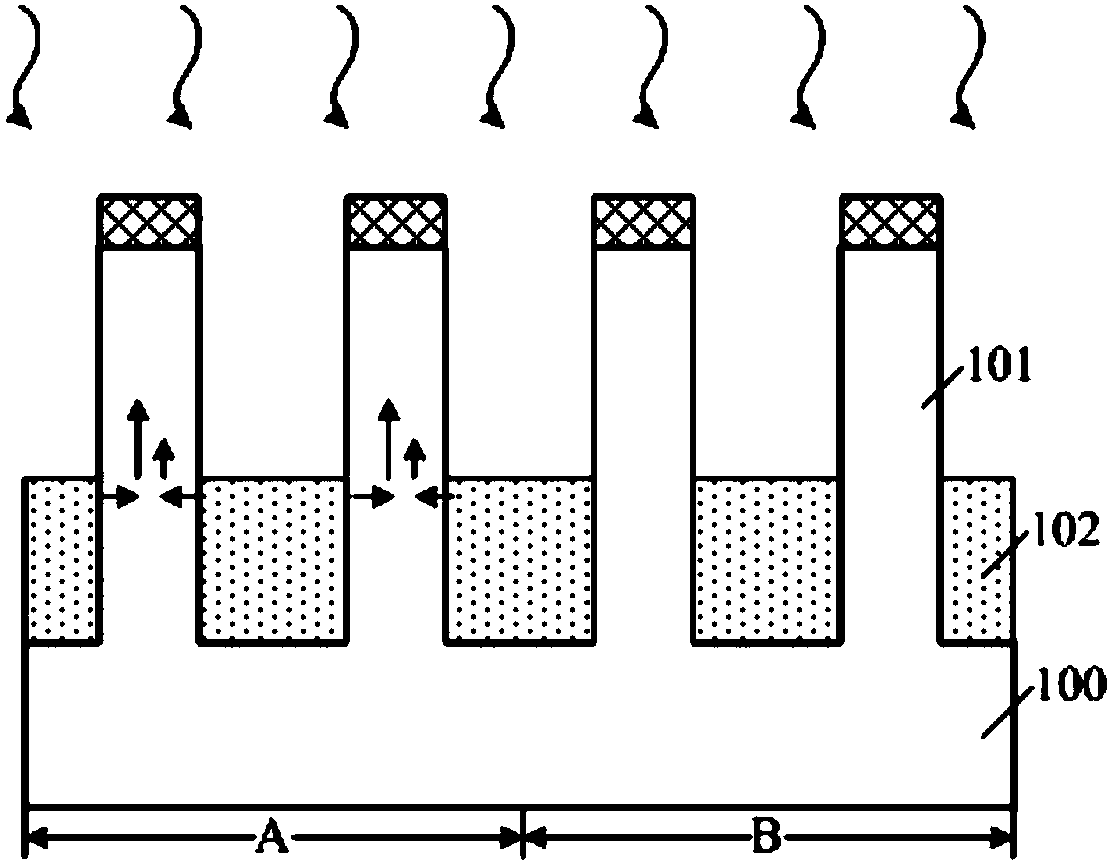

[0034] After research, it is found that as the size of the fin used to form the fin field effect transistor continues to shrink, the bottom of the source region and the drain region formed in the fin is prone to bottom punch through (punch through), that is, the sou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More