A trench-gate dmos device with a dielectric barrier

A dielectric barrier and gate dielectric layer technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as the inability to eliminate parasitic BJT turn-on, the inability to infinitely reduce the parasitic BJT base resistance, and increase the device threshold voltage. Effects of UIS failure capability, improved UIS tolerance, and improved reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

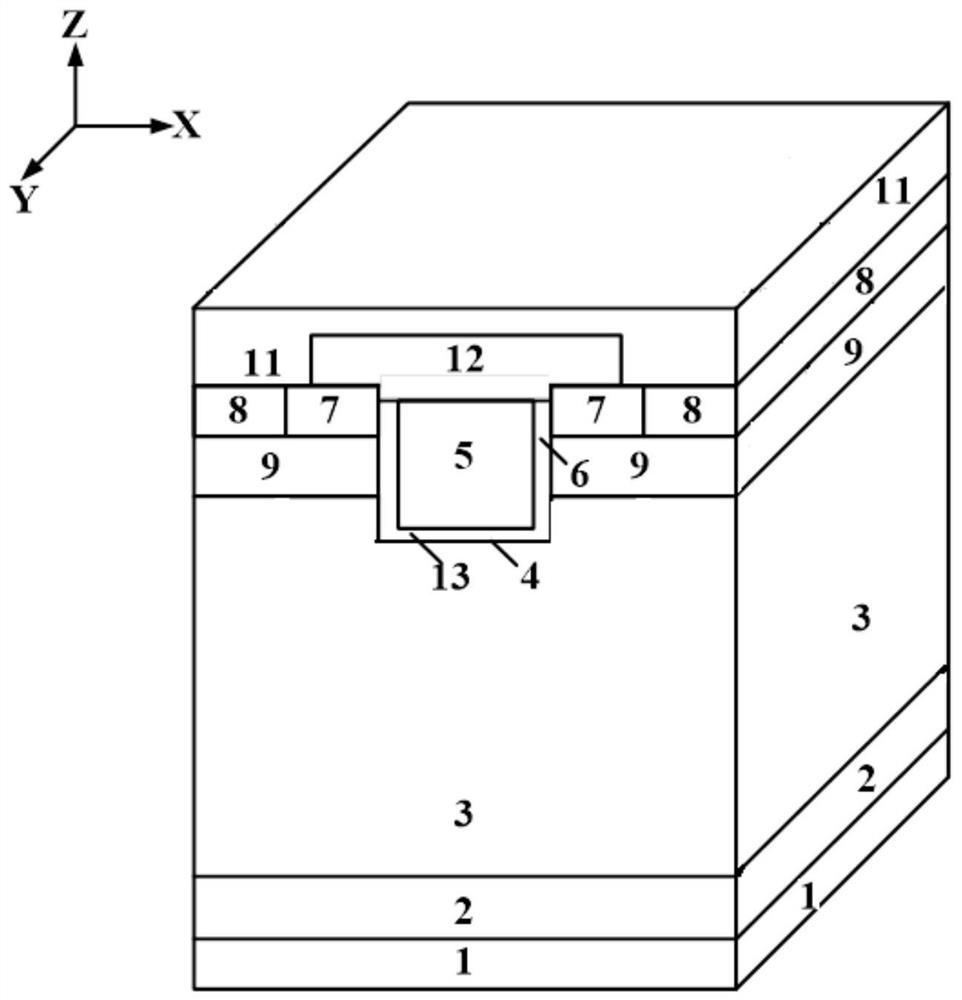

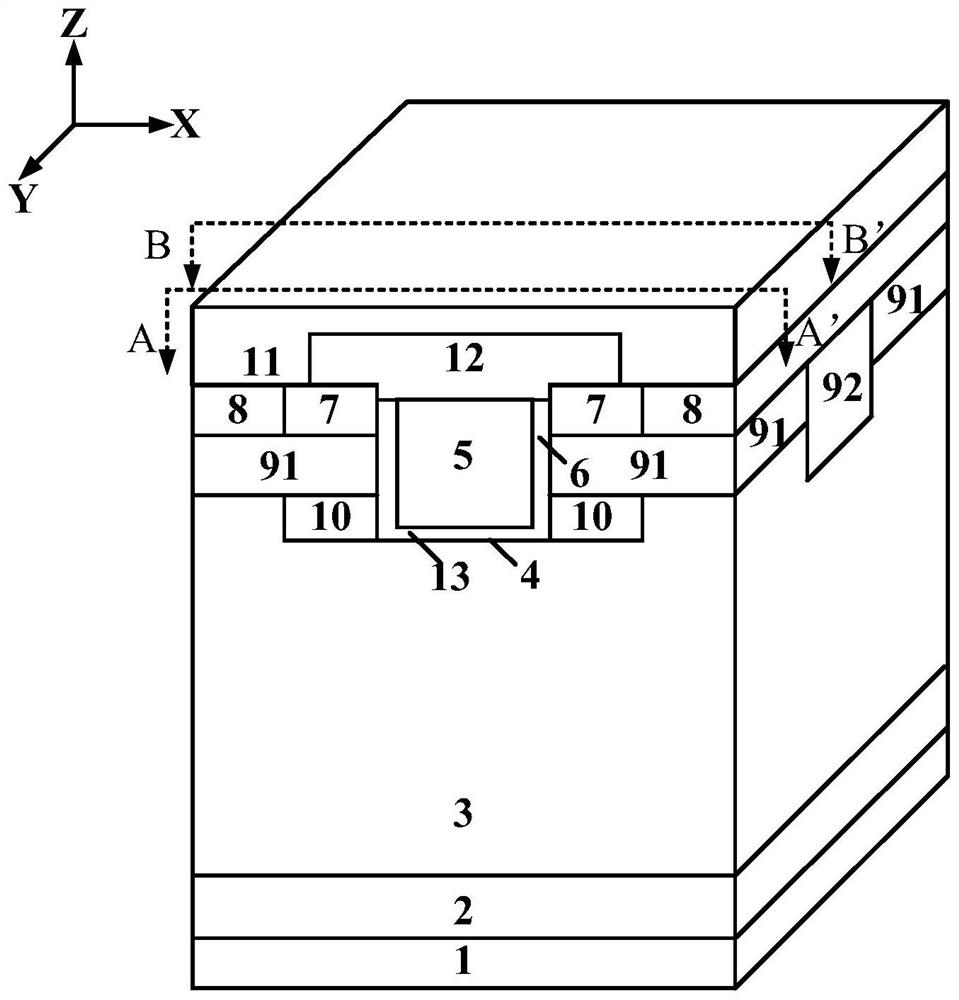

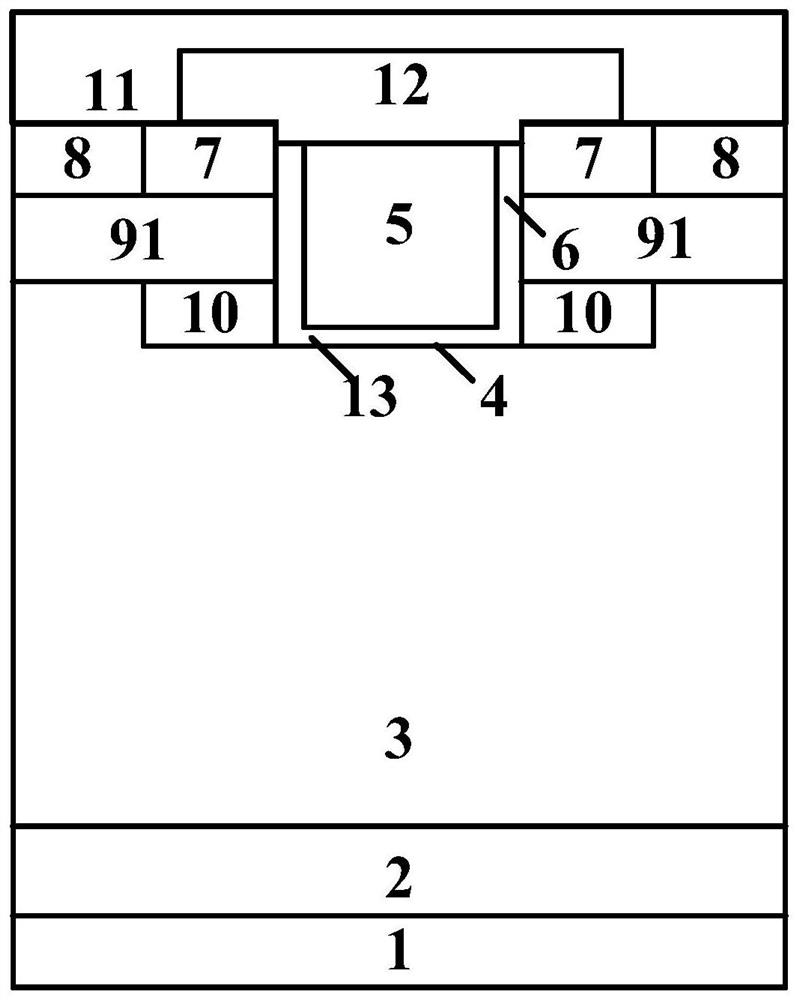

[0024] This embodiment provides a trench gate DMOS device with a dielectric barrier layer, the three-dimensional schematic diagram of its cell structure is as follows figure 2 As shown, the schematic diagrams of the sections obtained along the cell structure line AA' and BB' are as follows image 3 with Figure 4 As shown, it includes a metallized drain 1, a first conductivity type semiconductor doped substrate 2, a first conductivity type semiconductor doped drift region 3, a gate electrode 5, a gate dielectric layer 6, a second conductivity type semiconductor body region, and a second conductivity type semiconductor body region. A semiconductor doped source region 7 of one conductivity type, a semiconductor doped contact region 8 of a second conductivity type and a metallized source 11;

[0025]The metallized drain 1 is located on the back side of the first conductivity type semiconductor doped substrate 2; the first conductivity type semiconductor doped drift region 3 is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More