Automatic test system and method for chip ADC performance

An automated test and chip technology, applied in the field of instruments and meters, can solve the problems of single chip output pin compatibility, high time and cost of debugging instruments, and expensive high-precision instruments, so as to achieve convenient operation, reduce R&D costs and manpower Effect of cost input and measurement accuracy guarantee

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The patent of the present invention will be described in detail below in conjunction with specific software and hardware operation construction as an example.

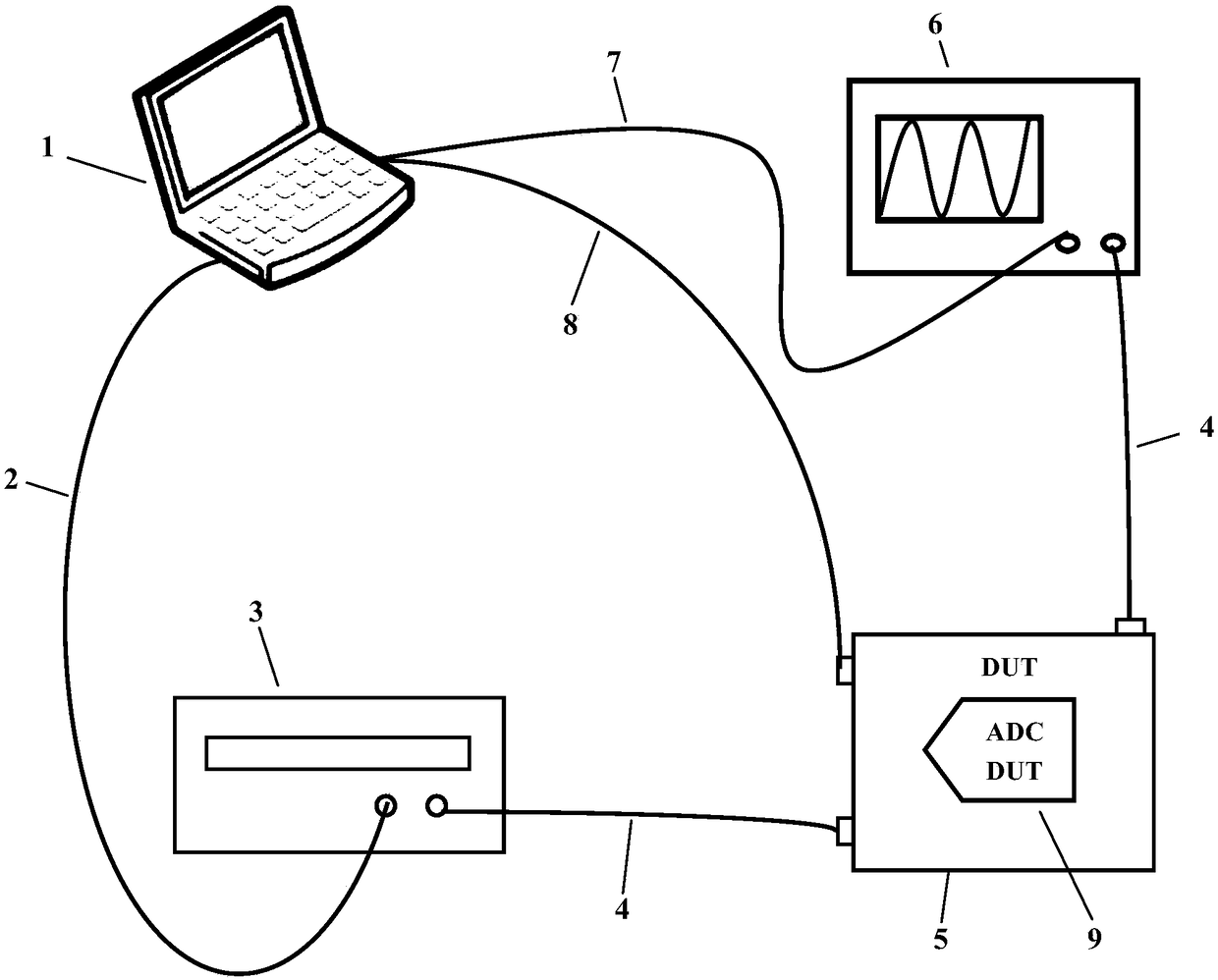

[0020] figure 1 Including 1. PC terminal, 2. RS232 connection line, 3. Programmable signal source, 4. Clip line, 5. Motherboard to be tested, 6. Programmable logic analyzer, 7. USB connection line, 8. Serial port connection 9. The sub-board to be tested can be plugged and plugged.

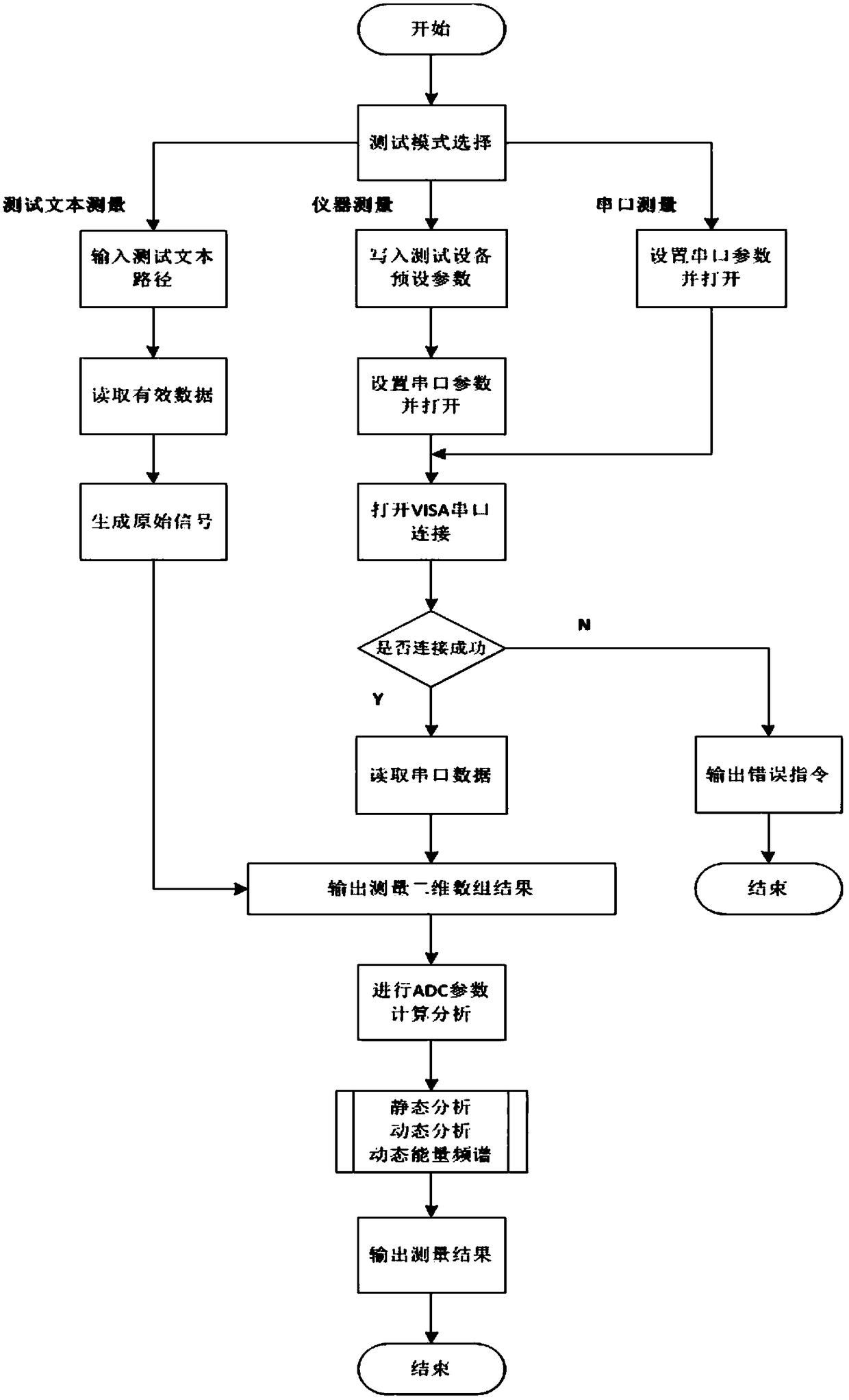

[0021] combine figure 1 , figure 2 Shown:

[0022] Step 1: Before the measurement starts, the signal input port of the motherboard 5 to be tested is connected to the signal source 3 using the clamp line 4, and the applicable pluggable sub-board 9 to be tested is selected and directly plugged into the unified pin reserved on the motherboard 5 to be tested , the serial port output end of the motherboard 5 to be tested is connected to the programmable logic analyzer 6 by using the clamp line 4 . The programmable signal source 3 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More