Organic field-effect multilevel transistor memory on basis of light regulation and control and method for preparing organic field-effect multilevel transistor memory

An organic field and light regulation technology, which is applied in the fields of organic semiconductor device materials, semiconductor/solid-state device manufacturing, and electric solid-state devices, etc., can solve the problems of potential safety hazards, large operating voltage, waste of resources, etc. The effect of reducing the dependence on operating voltage and reducing labor costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

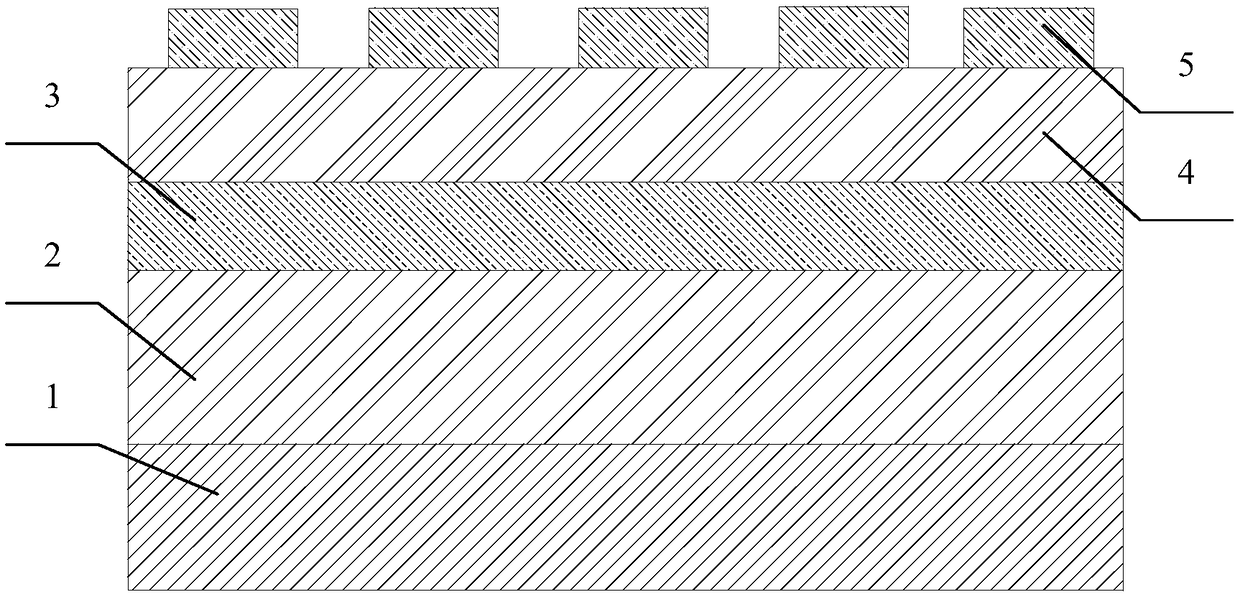

[0038] The organic field effect transistor memory structure, its structure schematic diagram is as follows figure 1 shown, including:

[0039] A substrate 1 with a gate electrode formed on its surface;

[0040] a gate insulating layer 2 covering the gate electrode;

[0041] A quantum dot-doped thin film layer 3 formed on the gate insulating layer 2;

[0042]A photosensitive semiconductor layer 4 formed on the quantum dot-doped thin film layer 3; and

[0043] The source and drain electrodes 5 are formed on both sides of the channel region on the surface of the photosensitive semiconductor layer 4 .

[0044] In the technical solution of this embodiment, a highly doped silicon wafer with a gate electrode formed on its surface is used as the substrate, and the thickness of the substrate 1 is about 650 μm (the silicon wafer is a commercial product, purchased from Suzhou Jingsi Electronic Technology Co., Ltd.); A layer of 50nm silicon dioxide is used as a gate insulating layer; ...

Embodiment 2

[0062] In the technical scheme of this embodiment, a heavily doped silicon wafer is used as a substrate, and a gate electrode is formed on the surface substrate; a layer of 300nm silicon dioxide is used as a gate insulating layer; doped with lead selenide quantum dots (PbSe) The polystyrene (PS) film is a quantum dot-doped thin film layer, its thickness is 25nm, as a charge transport layer; a layer of 30nm thick pentacene is vapor-deposited on the quantum dot-doped thin film layer as a photosensitive semiconductor layer; Metal copper is vapor-deposited on both sides of the conductive channel of the photosensitive semiconductor layer as source and drain electrodes.

[0063] During actual preparation, the room temperature in the laboratory is kept at about 25°C, and the indoor humidity is kept at about 40%.

[0064] The specific preparation steps of the memory described in this embodiment are as follows:

[0065] (1) configure lead selenide (PbSe) solution, the solution concent...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Membrane thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More