Multi-step deposition-based efficient crystalline silicon heterojunction solar cell electrode structure and preparation method thereof

A solar cell, multi-step deposition technology, applied in the direction of circuits, photovoltaic power generation, electrical components, etc., can solve the problems of many dangling bond defects in the intrinsic layer of amorphous silicon, less H atom content, and reduce the density of interface defect states, etc., to achieve Improve the photoelectric conversion efficiency, increase the H atom content, and reduce the effect of defect state density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

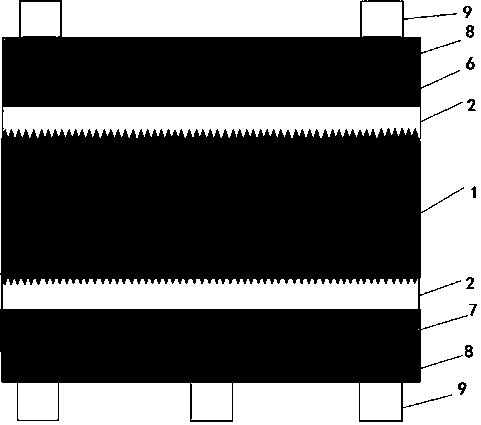

[0030] see figure 2 , the present invention relates to a multi-step deposition high-efficiency crystalline silicon heterojunction solar cell electrode structure, which includes an N-type crystalline silicon wafer 1, and the front and back sides of the N-type crystalline silicon wafer 1 are provided with two layers of amorphous Intrinsic silicon layer, that is, the first intrinsic layer 2 of amorphous silicon and the second intrinsic layer 4 of amorphous silicon are provided on the front and back sides of the N-type crystalline silicon wafer 1;

[0031] An n-type amorphous silicon doped layer 6 is provided on the outside of the second layer 4 of the intrinsic layer of amorphous silicon on the front side, and a TCO conductive film 8 is provided on the outside of the n-type amorphous silicon doped layer 6. A number of Ag electrodes 9 are provided on the outside of the front TCO conductive film 8;

[0032] A p-type amorphous silicon doped layer 7 is provided outside the second l...

Embodiment 2

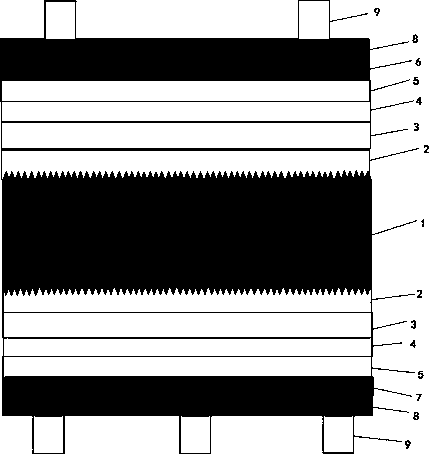

[0046] see figure 2 , the present invention relates to a multi-step deposited high-efficiency crystalline silicon heterojunction solar cell electrode structure, which includes an N-type crystalline silicon wafer 1, and the front and back sides of the N-type crystalline silicon wafer 1 are provided with three layers of amorphous silicon Intrinsic layer, that is, the front and back sides of the N-type crystalline silicon wafer 1 are provided with a first layer 2 of an intrinsic layer of amorphous silicon, a second layer 4 of an intrinsic layer of amorphous silicon and a third layer of an intrinsic layer of amorphous silicon;

[0047] The outside of the third layer of the intrinsic layer of amorphous silicon on the front is provided with an n-type amorphous silicon doped layer 6, and the outside of the n-type amorphous silicon doped layer 6 is provided with a TCO conductive film 8. The outside of the TCO conductive film 8 is provided with several Ag electrodes 9;

[0048] The o...

Embodiment 3

[0062] see figure 2 , the present invention relates to a multi-step deposited high-efficiency crystalline silicon heterojunction solar cell electrode structure, which includes an N-type crystalline silicon wafer 1, and the front and back sides of the N-type crystalline silicon wafer 1 are provided with four layers of amorphous The silicon intrinsic layer, that is, the front and back of the N-type crystalline silicon wafer 1 are provided with the first layer 2 of the intrinsic layer of amorphous silicon, the second layer 4 of the intrinsic layer of amorphous silicon, and the third layer of the intrinsic layer of amorphous silicon and the fourth layer of the intrinsic layer of amorphous silicon;

[0063] An n-type amorphous silicon doped layer 6 is provided on the outside of the fourth layer of the intrinsic layer of amorphous silicon on the front side, and a TCO conductive film 8 is provided on the outside of the n-type amorphous silicon doped layer 6. The outside of the TCO ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More