A Fast Load Response LDO Based on Dual Power Rails

A dual power supply and power supply voltage technology, applied in the direction of adjusting electrical variables, instruments, control/regulation systems, etc., can solve the problems that affect the response speed of LDO, reduce the undershoot, and accelerate the response speed of the output terminal, so as to speed up the loop response The effects of speed, high stability, and fast load response

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

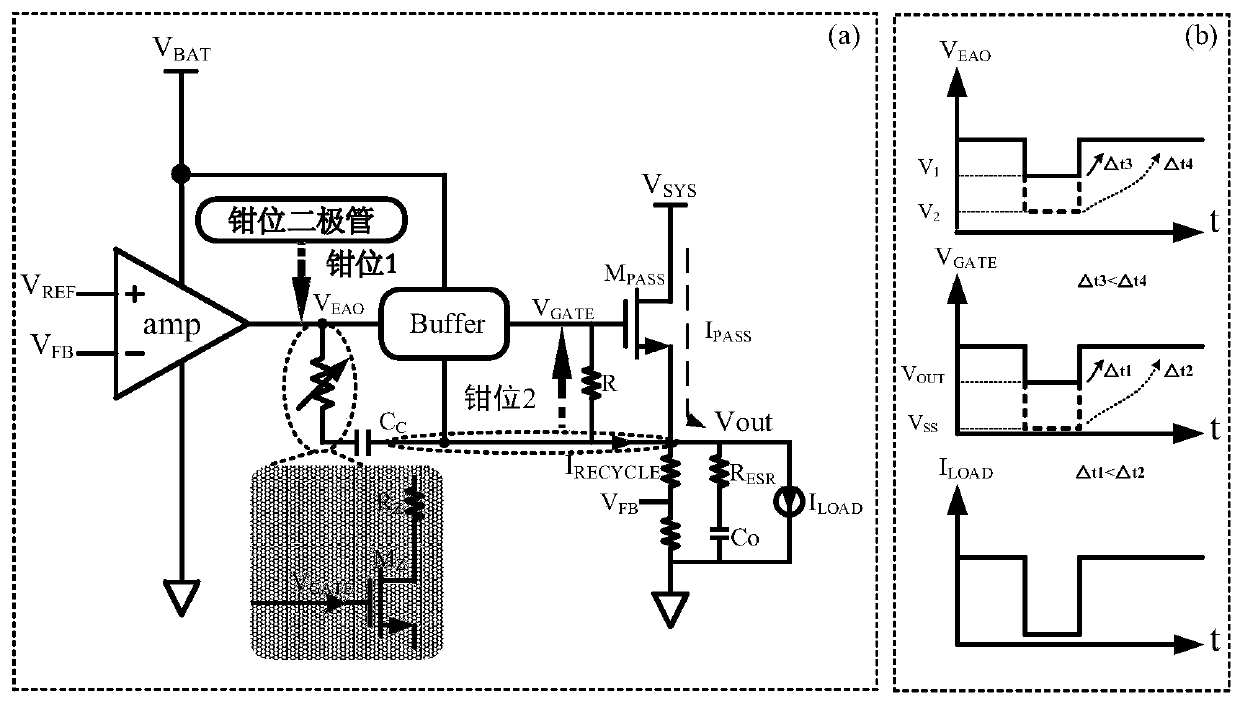

[0037] For NMOS LDO, the overshoot of the output voltage will be directly affected by the power transistor M PASS Gate-to-source voltage V GS This process is far ahead of the response of the loop, so the present invention speeds up the response speed of the loop when the output voltage undershoots by properly sacrificing the response speed of the loop when the output voltage overshoots. According to this idea, the LDO can The feedback loop is clamped when the output voltage is in an overshoot condition.

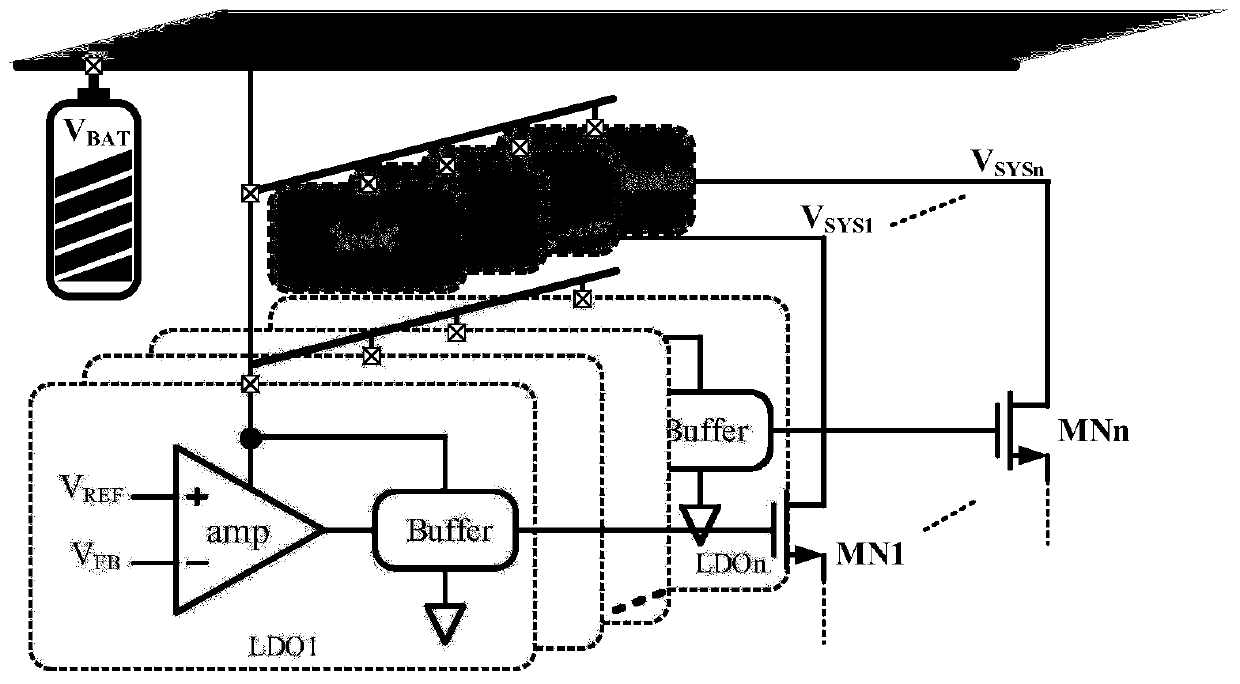

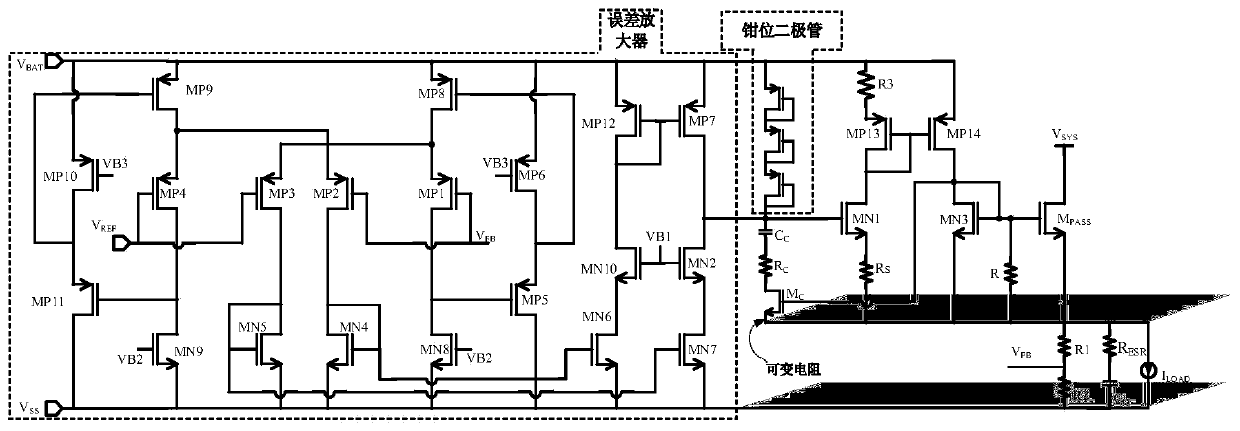

[0038] Such as figure 2 (a) is a topological schematic diagram of a fast load response LDO based on dual power rail power supply proposed by the present invention, including an error amplifier, an output unit, a buffer unit Buffer, a clamp unit and a compensation unit, and the output unit includes a power Tube MPASS , the first voltage dividing resistor R1 and the second voltage dividing resistor R2, the power tube M PASS NMOS tube, power tube M PASS The drain of the sec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More