Programmable super-speed advanced setting type frequency divider

A frequency divider, ultra-high-speed technology, applied in the direction of electrical components, automatic power control, logic circuits with logic functions, etc., can solve the problems of reducing the performance of frequency dividers, large area costs, and large delays, etc., to achieve Ultra-high-speed frequency division, low area overhead, and strong reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

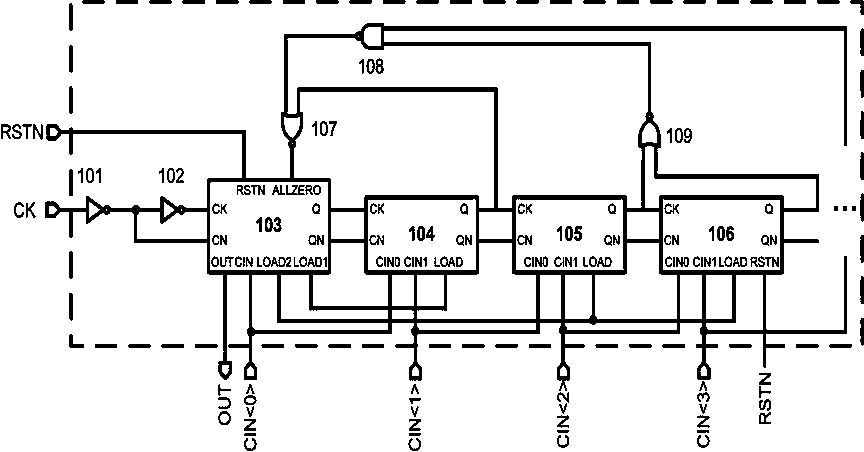

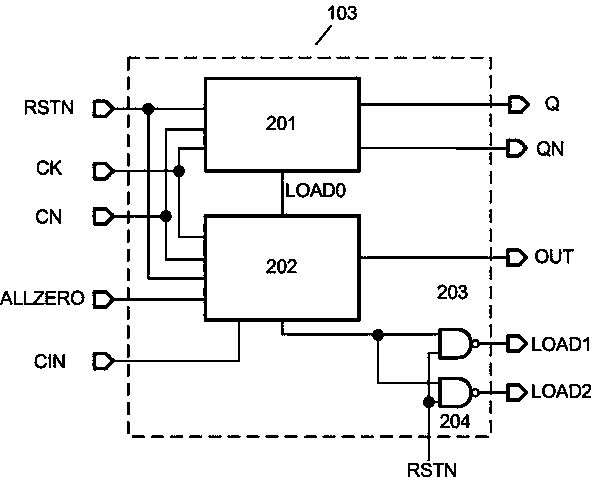

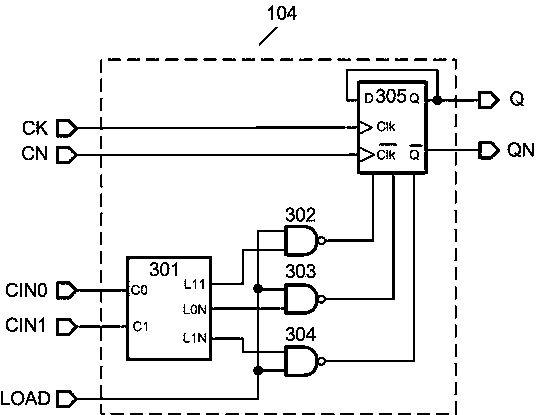

[0035] The programmable ultra-high-speed super-predigital frequency divider of this embodiment is as figure 1 As shown, it includes NOR gate 107, NAND gate 108, NOR gate 109, 0th frequency division module 103, 1st frequency division module 104, 2nd frequency division module 105 and N 3rd frequency division Module 106, N is a positive integer greater than or equal to 1;

[0036] The input terminal CK of the programmable ultra-high-speed super-predigital frequency divider is connected to the input terminal CK of the 0th frequency division module 103 through the first inverter 101 and the second inverter 102 connected in series, and the first inverter The connection node of the second inverter is connected to the input terminal CN of the 0th frequency division module 103; the output terminal OUT of the 0th frequency division module 103 constitutes the output terminal of the programmable ultra-high-speed super-predigital frequency divider OUT;

[0037] The output Q and the outp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More