nor FLASH device structure and its manufacturing method

A technology of device structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of high process cost and process time, and achieve the effect of reducing process cost and process time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

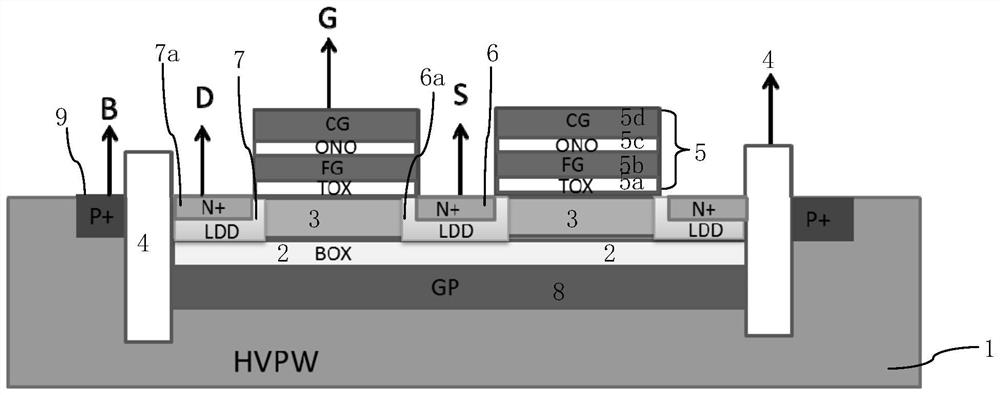

[0057] Such as figure 1 Shown is the device structure diagram of the NOR FLASH device structure of the embodiment of the present invention, and the NORFLASH device structure of the embodiment of the present invention includes:

[0058] An FDSOI substrate formed by sequentially stacking a bottom semiconductor substrate 1 , an insulating buried layer 2 and a top semiconductor substrate 3 .

[0059] In the embodiment of the present invention, the bottom semiconductor substrate 1 is a silicon substrate, the top semiconductor substrate 3 is a silicon substrate, and the buried insulating layer 2 is a buried silicon oxide layer. figure 1 In , the buried insulating layer 2 is also represented by BOX.

[0060] A shallow trench field oxygen 4 is formed on the FDSOI substrate, the shallow trench field oxygen 4 passes through the top semiconductor substrate 3 and the buried insulating layer 2, and the shallow trench field oxygen 4 The bottom enters into said bottom semiconductor substra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More