A wafer level packaging structure of a filter and a process thereof

A wafer-level packaging and filter technology, applied in electrical components, impedance networks, etc., can solve the problems of strict flatness requirements of substrates and sealing covers, inconsistent performance of accurate devices, and high cost of surface sealing covers. Process yield, small warpage, and the effect of reducing difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

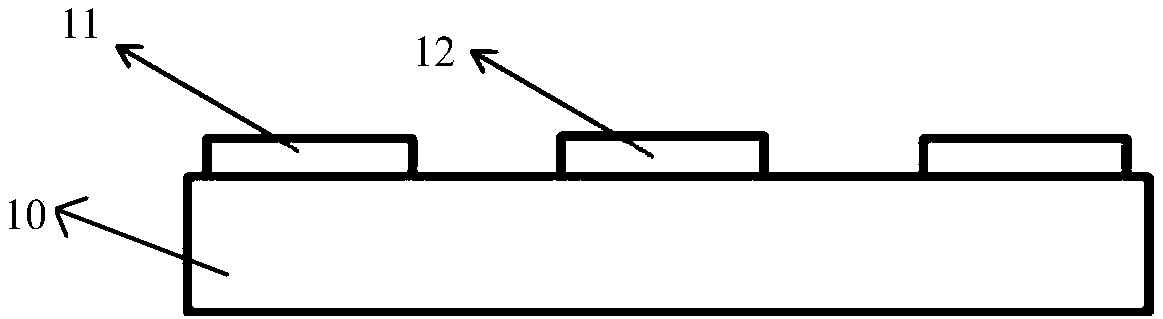

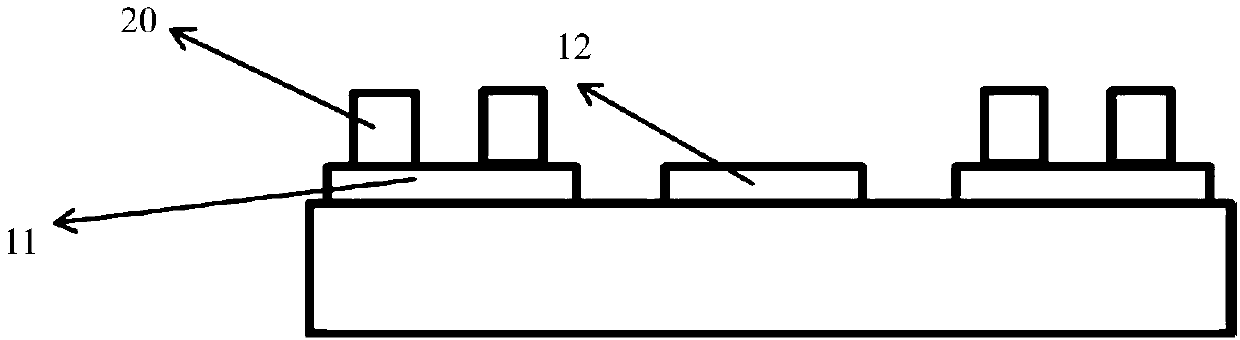

[0039] refer to Image 6 , a filter wafer-level packaging structure of the present invention, which is a thin-film packaging structure, including a chip substrate 10, a first thin-film layer 20, a second thin-film layer 30, and metal connectors 40 and the like. see figure 2 The working surface of the chip substrate 10 is provided with pads 11 and IDT 12, the positions of the pads 11 and IDT12 are not limited, and can be designed according to requirements. For example: for a single chip, its IDT (interdigital transducer) is positioned at the central position of chip substrate 10, and bonding pad 11 is positioned at chip substrate 10 edges, and is spaced certain distance between bonding pad 11 and IDT12, and bonding pad 11 quantity is different Unique, can be two or even more. The chip of the present invention is a surface acoustic wave filter, or other filters with similar functions.

[0040] The first thin film layer 20 is coated on the working surface of the chip substrat...

Embodiment 2

[0052] see Figure 7 , a filter wafer-level packaging structure and its process, its main structure and process are generally the same as in the first embodiment, the difference is that: the metal connector 40 is a hollow connector, and the metal connector 40 is covered Related steps of filling the layer 41 , the filling layer 41 plays a role of protecting the metal connector 40 . The upper surface of the metal connector 40 can be extended according to the welding position, and nickel-palladium-gold, nickel-gold, titanium-copper pads, etc. can be made at any position to form the welding part 40 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More