Packaging structure and packaging method of chip module and wafer level chip

A wafer-level chip and packaging method technology, applied in the structural details of semiconductor lasers, laser components, semiconductor lasers, etc., can solve the problem of inability to meet smaller apertures and high aspect ratios, affecting product conductivity reliability, and limited effective contact area and other problems, to achieve the effect of increasing the effective contact area, shortening the packaging process, and reducing the delamination of edge materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

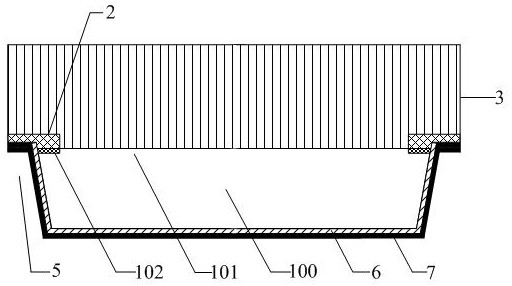

[0044] Such as Figure 1a As shown, a chip module includes a chip unit 100, several metal bumps 2 and optical components 3, the chip unit 100 has a functional surface and a non-functional surface opposite to the functional surface, and the functional surface includes a functional area 101 and a Several welding pads 102 around the functional area; each metal bump 2 is correspondingly formed above each welding pad 102 of the chip unit 100; the optical component 3 and the metal bump 2 and the functional surface of the chip unit 100 not covered by the metal bump 2 Bonding connection: On both sides of the chip unit 100 extending from the non-functional surface to the direction of the metal bump 2, a first opening 5 is formed, the first opening 5 cuts through and exposes the side wall of the solder pad 102, and the bottom of the first opening 5 penetrates to the metal bump 2. The inside of the protrusion 2; the side surface of the first opening 5 and the non-functional surface of th...

Embodiment 2

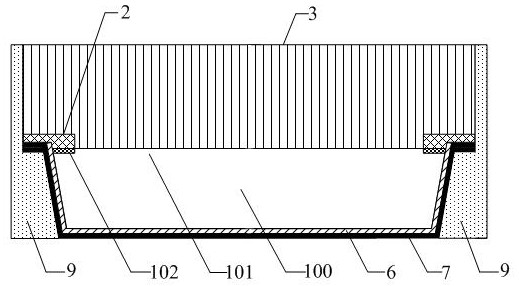

[0052] Such as Figure 2a As shown, a wafer-level chip packaging structure includes a wafer 100', a plurality of metal bumps 2 and a bonding sheet of an embossed element 3'. In this embodiment, the wafer 100' is a VCSEL (Vertical Cavity SurfaceEmitting Laser) wafer.

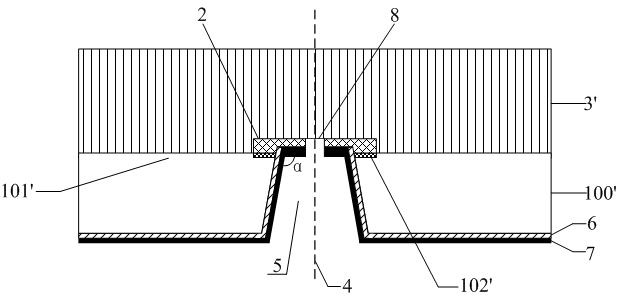

[0053] The wafer 100' has a functional surface and a non-functional surface opposite to the functional surface. The functional surface includes a functional area 101' and a number of pads 102' located around the functional area 101'; the wafer 100' includes a number of chip units. There is a dicing line 4 between two adjacent chip units, and several welding pads 102' of the adjacent two chip units are located on both sides of the dicing line, and the metal bump 2 is formed above the welding pads 102' of the adjacent two chip units. 2 is coaxial with the dicing line 4; the embossing element 3' is bonded to the metal bump 2 and the functional surface of the wafer 100' not covered by the metal bump; the non-functio...

Embodiment 3

[0063] A packaging method for a wafer-level chip, comprising the following steps:

[0064] (1) Wafer preparation: see image 3 , provide a wafer 100' with a plurality of chip units, the wafer 100' has a functional surface and a non-functional surface opposite to the functional surface, the functional surface includes a functional area 101' and several pads 102' located around the functional area.

[0065] (2) Metal bump formation: see Figure 4 , forming a metal bump 2 above the bonding pads 102' of two adjacent chip units. The specific method for forming the metal bump 2 is: first coat a layer of photoresist on the functional surface of the wafer, expose, develop, cover The photoresist in the area of the bonding pads of the two adjacent chip units is developed, and then the metal bump 2 is deposited on the area above the bonding pads 102 ′ of the adjacent two chip units, and finally the remaining photoresist is removed.

[0066] (3) Embossed component bonding: see Figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More