Thin film transistor and manufacturing method thereof, and display substrate, panel and apparatus

A technology of thin film transistors and substrate substrates, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of length reduction, affecting the performance of thin film transistor devices, etc., and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

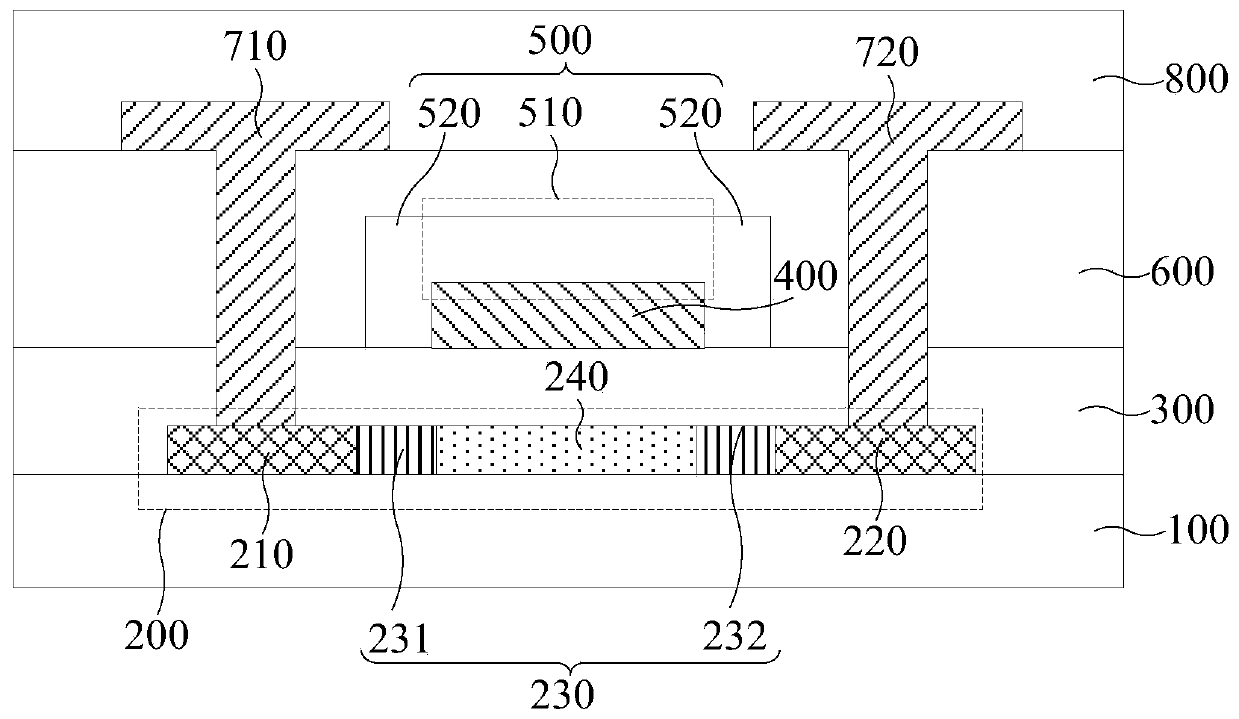

[0061] Figure 5 It is a schematic flowchart of a method for manufacturing a thin film transistor provided by an embodiment of the present invention. The preparation method of the thin film transistor is used for preparing the thin film transistor described in any embodiment of the present invention. like Figure 5 As shown, the preparation method of the thin film transistor may specifically include the following:

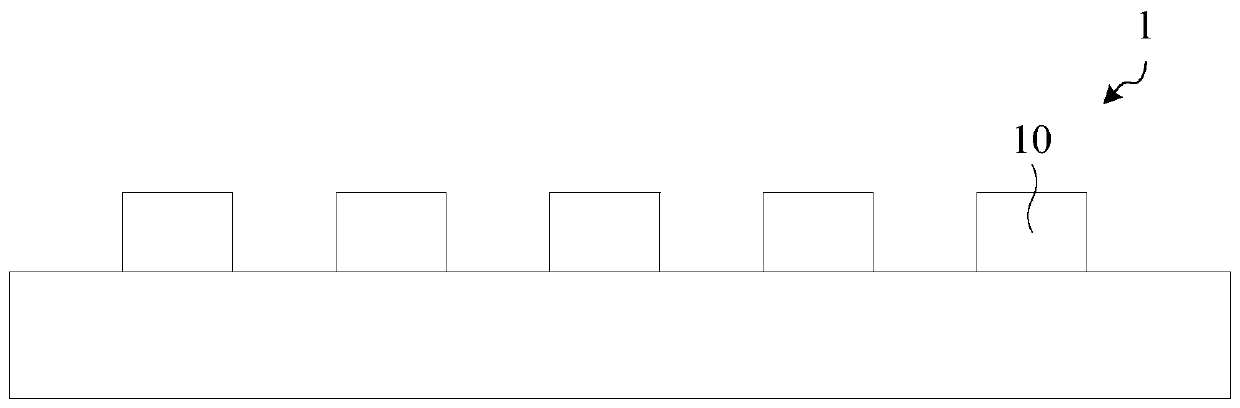

[0062] Step 11, providing a base substrate.

[0063] like Image 6 As shown, a base substrate 100 is provided.

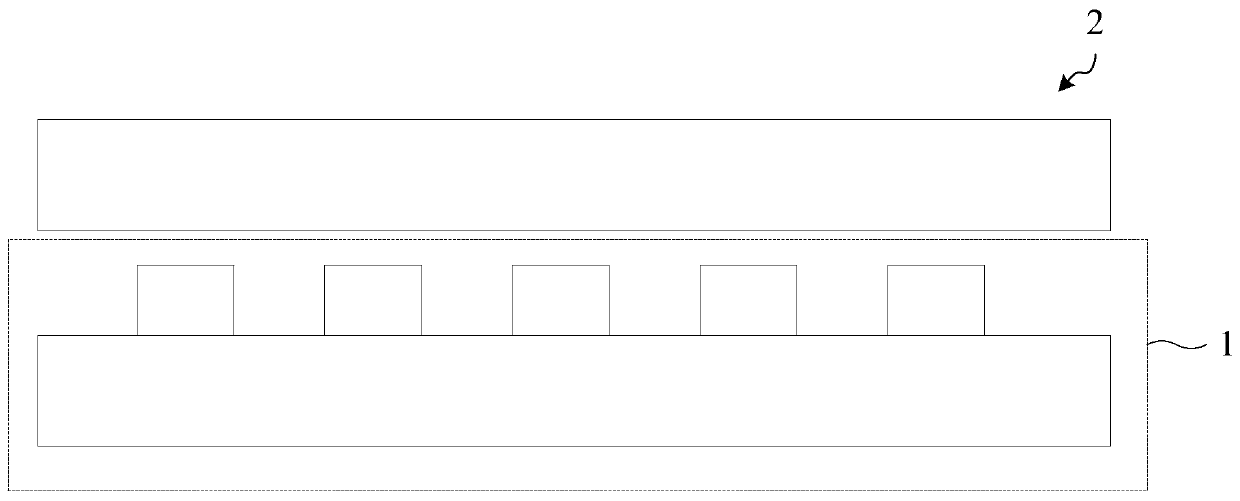

[0064] Step 12, forming a patterned active layer on the base substrate.

[0065] like Figure 7 As shown, a patterned active layer 200 is formed on the base substrate 100 .

[0066] Specifically, the entire active layer 200 may be formed on the base substrate 100 first, and then the active layer 200 may be patterned through a yellow light process. Exemplarily, the host material of the active layer 200 may be a metal oxide semiconductor, the dopan...

example 1

[0094] An active layer is formed on the base substrate, the main material of the active layer is a metal oxide semiconductor, the doping material is tantalum oxide, and the thickness of the active layer is 20nm;

[0095] The gate insulating layer is formed on the substrate and the active layer by PECVD process, and the gate insulating layer is a single layer of SiO 2 Thin film, the thickness is 300nm, the deposition temperature is 230℃, the gas and gas ratio used are SiH 4 / N 2 O=4 / 300sccm;

[0096] The gate is formed on the gate insulating layer by PVD, the material of the gate is Mo, the thickness is 200nm, and the length is 2.5um;

[0097] A protective layer covering the gate and in contact with the gate insulating layer is formed by PECVD process, and the material of the protective layer is SiN x , the thickness is 100nm, the length is 4.0um, the deposition temperature is 350°C, the gas and gas ratio used are SiH 4 / NH 3 / N 2 =20 / 5 / 270sccm, the length of one side of ...

example 2

[0102] An active layer is formed on the base substrate, the main material of the active layer is a metal oxide semiconductor, the doping material is praseodymium oxide, and the thickness of the active layer is 20nm;

[0103] The gate insulating layer is formed on the substrate and the active layer by PECVD process, and the gate insulating layer is a single layer of SiO 2 Thin film, the thickness is 300nm, the deposition temperature is 230℃, the gas and gas ratio used are SiH 4 / N 2 O / Ar=4 / 300 / 300sccm;

[0104] Using PVD to form a gate on the gate insulating layer, the gate is a stacked structure of Mo and Al, wherein the thickness of the Mo layer is 150nm, the thickness of the Al layer is 50nm, and the length is 3.0um;

[0105] A protective layer covering the gate and in contact with the gate insulating layer is formed by PECVD process, and the material of the protective layer is SiO 2 , the thickness is 200nm, the length is 6.0um, the deposition temperature is 350℃, the ga...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More