A high-speed igbt device with ultra-low conduction voltage drop

A technology for conducting voltage drop and device, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of small short-circuit safe working area, large gate drive loss, low turn-off speed, etc., to improve the short-circuit safe working area, Avoid device failure or failure, prevent the effect of high potential

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

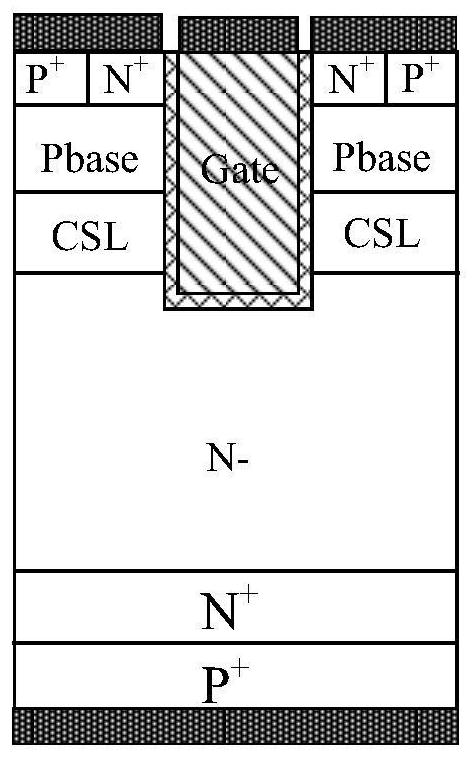

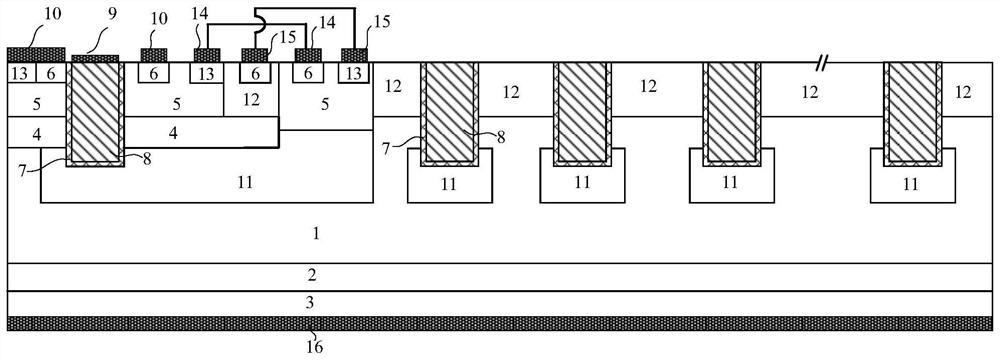

[0027] This embodiment provides a high-speed IGBT device with an ultra-low conduction voltage drop, and its cell structure and junction terminals are as follows image 3 As shown, it includes: a lightly doped N-type withstand voltage region 1, an N-type semiconductor region 2 arranged on the lower surface of the N-type withstand voltage region, forming an electric field termination layer, and a P-type collector region 3 arranged on the lower surface of the N-type semiconductor region 2 , the collector metal 16 covered on the lower surface of the P-type collector region 3, and the cell region and junction terminal region set on the upper surface of the N-type withstand voltage region 1;

[0028] The cell region includes: an epitaxial layer 12 disposed on the upper surface of the N-type withstand voltage region 1, a first P-type base region, a second P-type base region and a third IGBT base region disposed in the epitaxial layer 12. P-type base region, the first N-type carrier s...

Embodiment 2

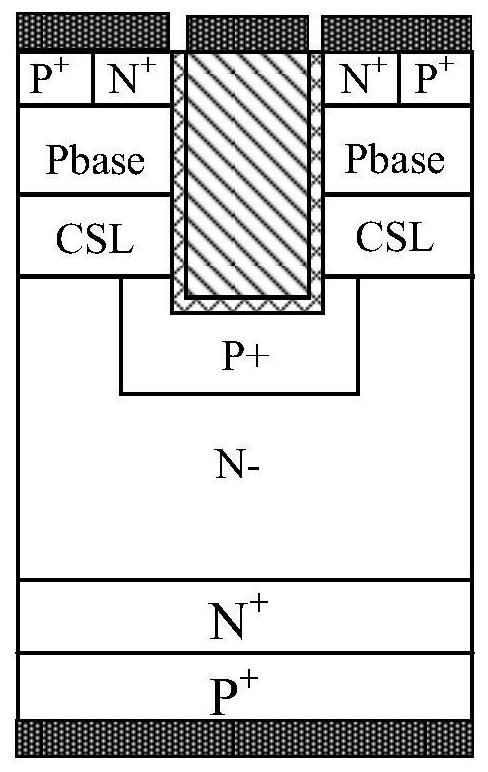

[0031] This embodiment provides a high-speed IGBT device with an ultra-low conduction voltage drop, and its cell structure and junction terminals are as follows Figure 4 As shown, the difference between it and Embodiment 1 is that the deep groove is composed of a filling medium 17 filled in the groove.

Embodiment 3

[0033] This embodiment provides a high-speed IGBT device with an ultra-low conduction voltage drop, and its cell structure and junction terminals are as follows Figure 5 As shown, the difference from Example 1 is that in the cellular region, an isolation region is also provided between the epitaxial layer and the third P-type base region, and the isolation region adopts the same structure as the trench gate , is also composed of a silicon dioxide gate dielectric layer 7 on the groove wall and a polysilicon gate 8 in the groove, and the polysilicon gate 8 is connected to the first connection metal 14, or is connected to the second connection metal 15, or is not connected to any region connected.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More