Laminated inductor and manufacturing method thereof

A manufacturing method and inductor technology, applied in the direction of inductors, circuits, electrical components, etc., can solve the problems of high process cost of laminated inductors, large inductance resistance, etc., to save photomasks and metal deposition processes, reduce resistance, The effect of connecting a low resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to describe in detail the technical content, structural features, achieved objectives and effects of the technical solution, the following detailed description is given in conjunction with specific embodiments and accompanying drawings.

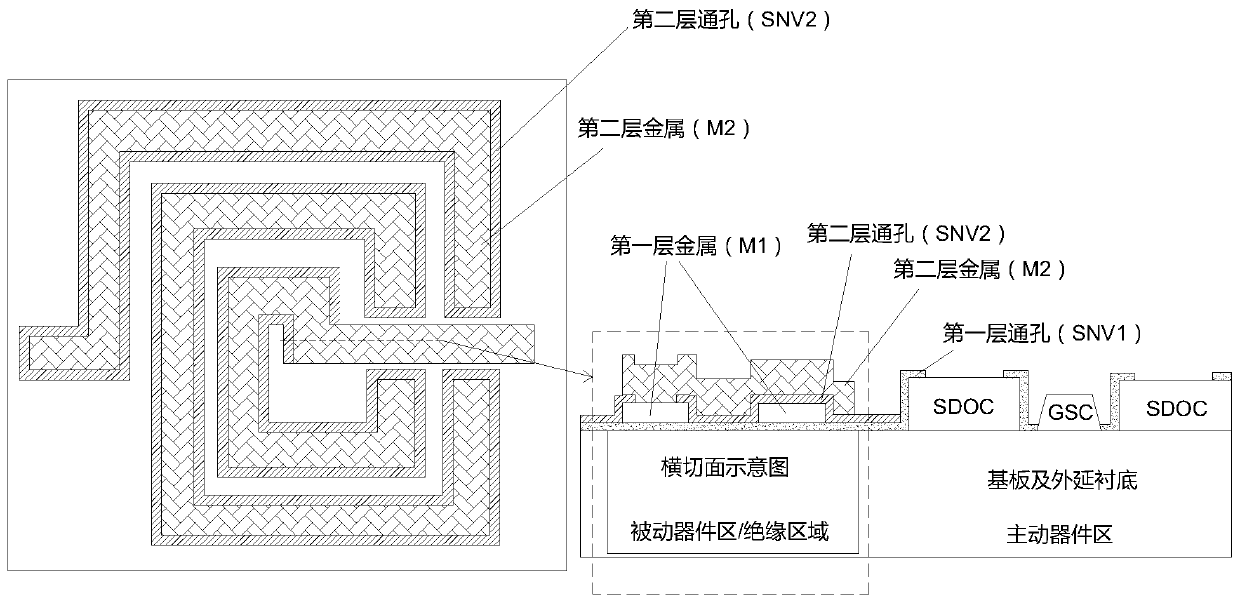

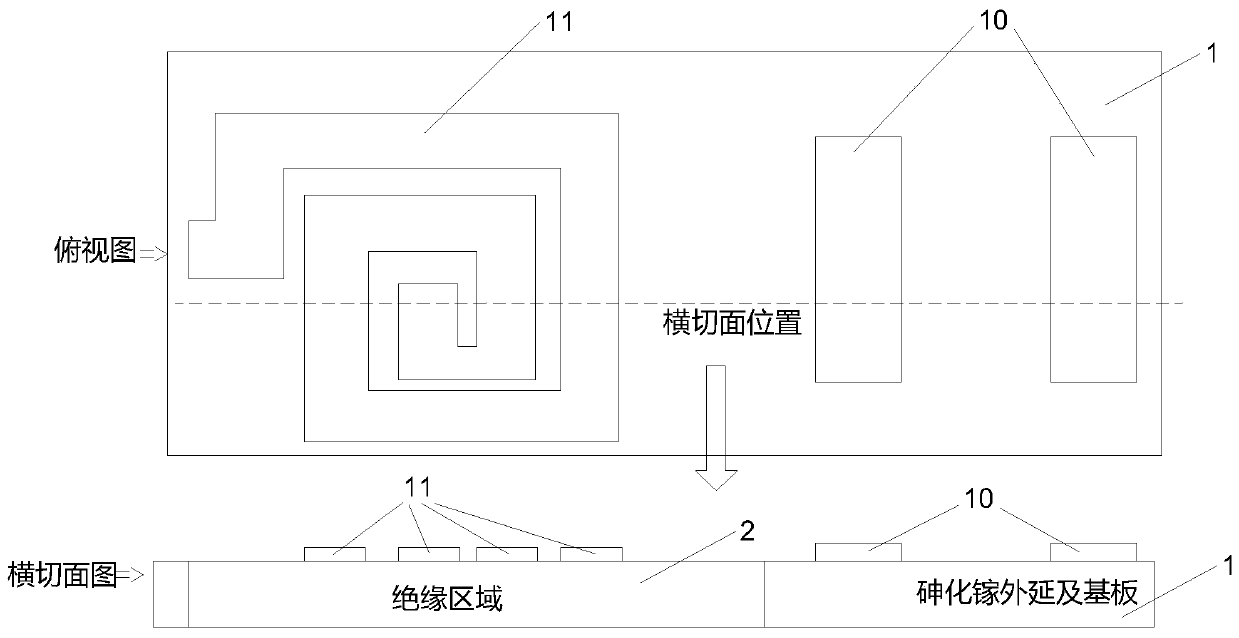

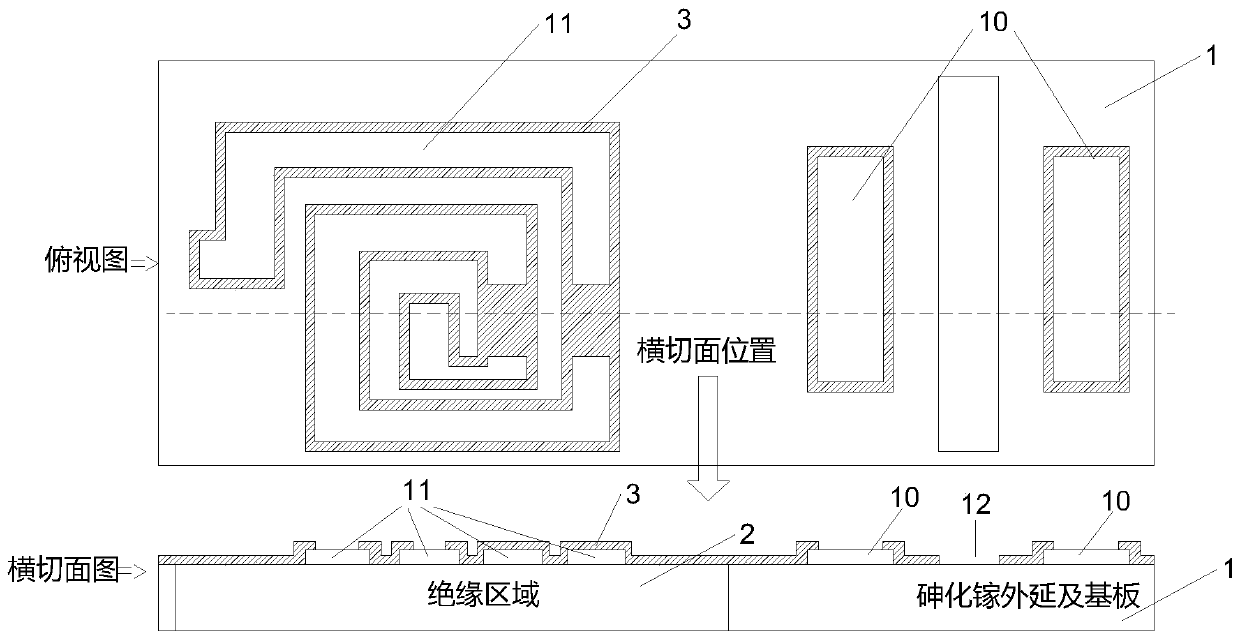

[0044] see Figure 1 to Figure 6 , this embodiment provides a method for fabricating a stacked inductor. This method can be fabricated on a semiconductor device 1. The semiconductor device can be a gallium arsenide epitaxy and a substrate. The semiconductor device includes an active device region and a passive device region, and the active device is not used. For the fabrication of transistors (including source, drain and gate), the passive device region is used to fabricate inductors, and the passive device region is subjected to insulation treatment before fabrication to form an insulating region, which is generally formed by ion implantation. The method includes the following steps: first, a first photoresist layer is fabri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More