Utilizing multilayer gate spacer to reduce erosion of semiconductor fin during spacer patterning

A multi-layer gate and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

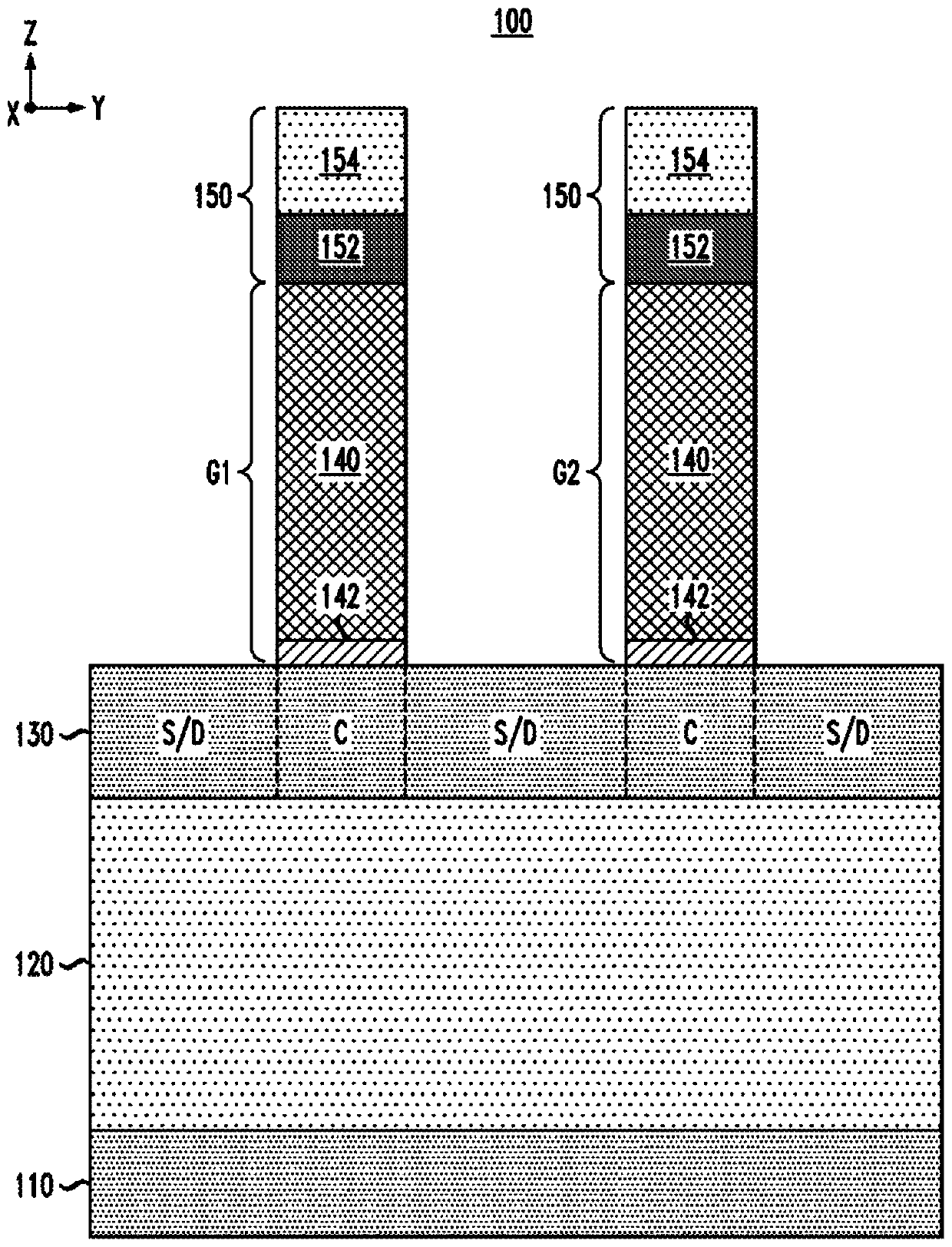

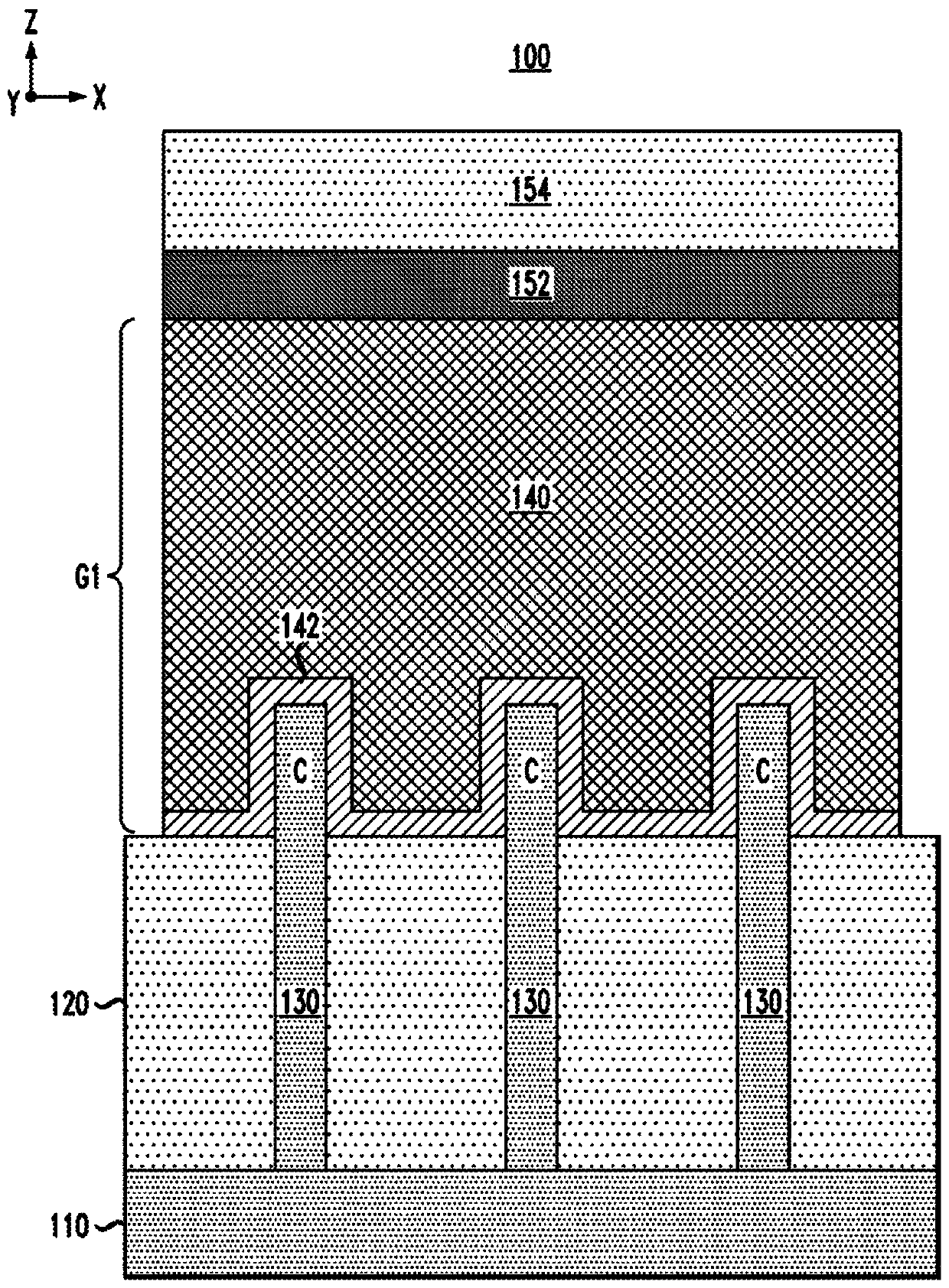

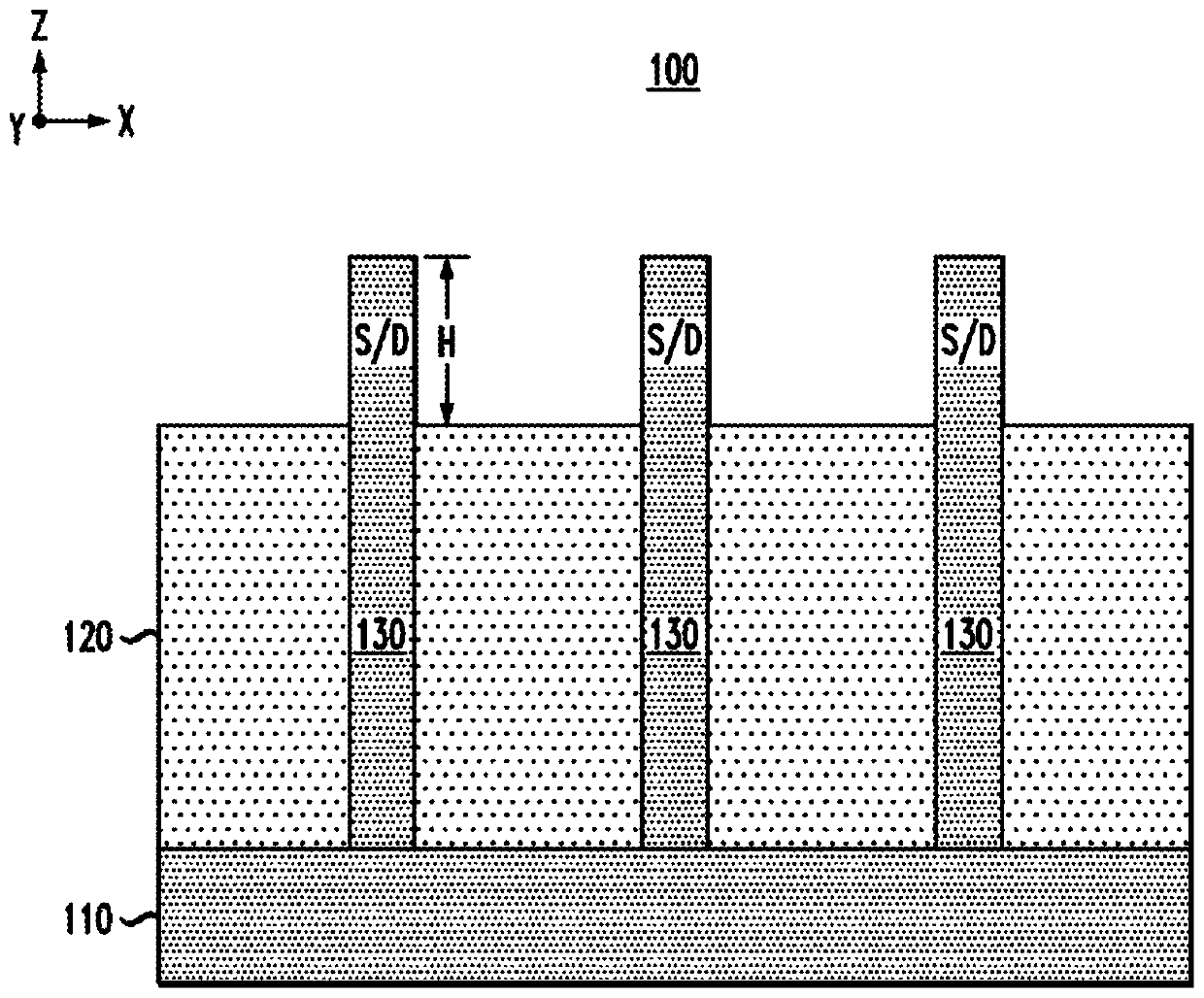

[0015] The embodiments will now be described in further detail with respect to a FinFET device including a multilayer gate isolation and a method for manufacturing a FinFET device, wherein when forming the gate isolation, the multilayer gate isolation is used to prevent or minimize vertical semiconductor fins. corrosion. It should be understood that the various layers, structures and regions shown in the drawings are schematic diagrams that are not drawn to scale. In addition, for ease of explanation, one or more layers, structures, and regions that are commonly used to form semiconductor devices or structures may not be explicitly shown in a given drawing. This does not mean that any layers, structures, and regions that are not explicitly shown are not omitted from the actual semiconductor structure.

[0016] In addition, it should be understood that the embodiments discussed herein are not limited to the specific materials, features, and processing steps shown and described he...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More