A kind of preparation method of Ge-based CMOS transistor

A technology of transistors and metal layers, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems affecting device performance, excessive source-drain contact resistance, low N-type impurity activation concentration, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

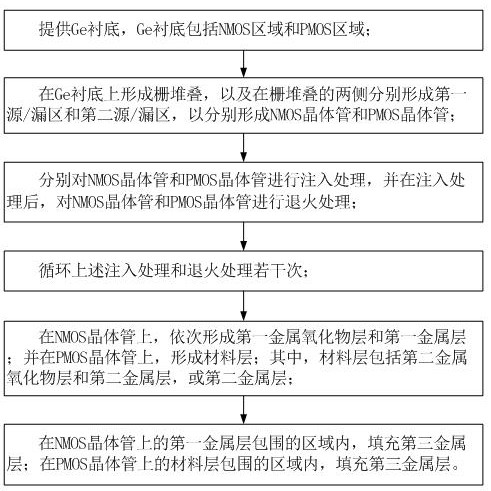

Method used

Image

Examples

Embodiment Construction

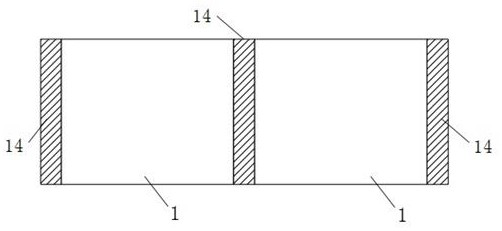

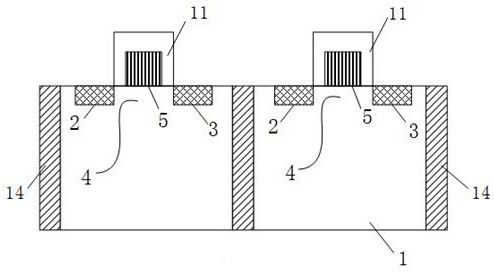

[0043] The specific implementation manners according to the present invention will be described below in conjunction with the accompanying drawings.

[0044] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, therefore, the present invention is not limited to the specific embodiments disclosed below limit.

[0045] Ge material has high and symmetrical carrier mobility, which can provide larger driving current and faster switching speed; at the same time, the forbidden band width of Ge is smaller than that of Si, and the required driving voltage is lower. Advantages, making it one of the most promising development directions for high-performance MOS devices.

[0046] However, there are still many problems to be solved in Ge-based devices, such as: low N-type impurity activation concentration, that is, in the Ge ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More