Method for improving layout photoetching performance, corrected layout and simulation method

A performance and lithography technology, which is applied in the direction of microlithography exposure equipment, originals for photomechanical processing, photolithography process exposure devices, etc., can solve the problem of poor lithography quality, smaller layout process window, and inability to effectively suppress Prohibition of periodical effects, dense periodical lines, mutual restriction and other issues, to achieve the effect of low cost, improved lithography quality, and improved lithography performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] A specific embodiment of the present invention discloses a method for improving photolithography performance by optimizing a one-dimensional line pattern structure in which prohibited periods and dense periods are alternately arranged, including the following steps:

[0055] Step 1: Obtain an optimized free light source considering the global situation. Obtain various types of test patterns as comprehensive as possible from the actual layout as the initial layout input. Initial light source parameters (generally, a ring light source is used as the initial light source) and related simulation parameters include lithography machine model, NA (numerical aperture) value, mask plate parameters (thickness, refractive index, etc.), etc.;

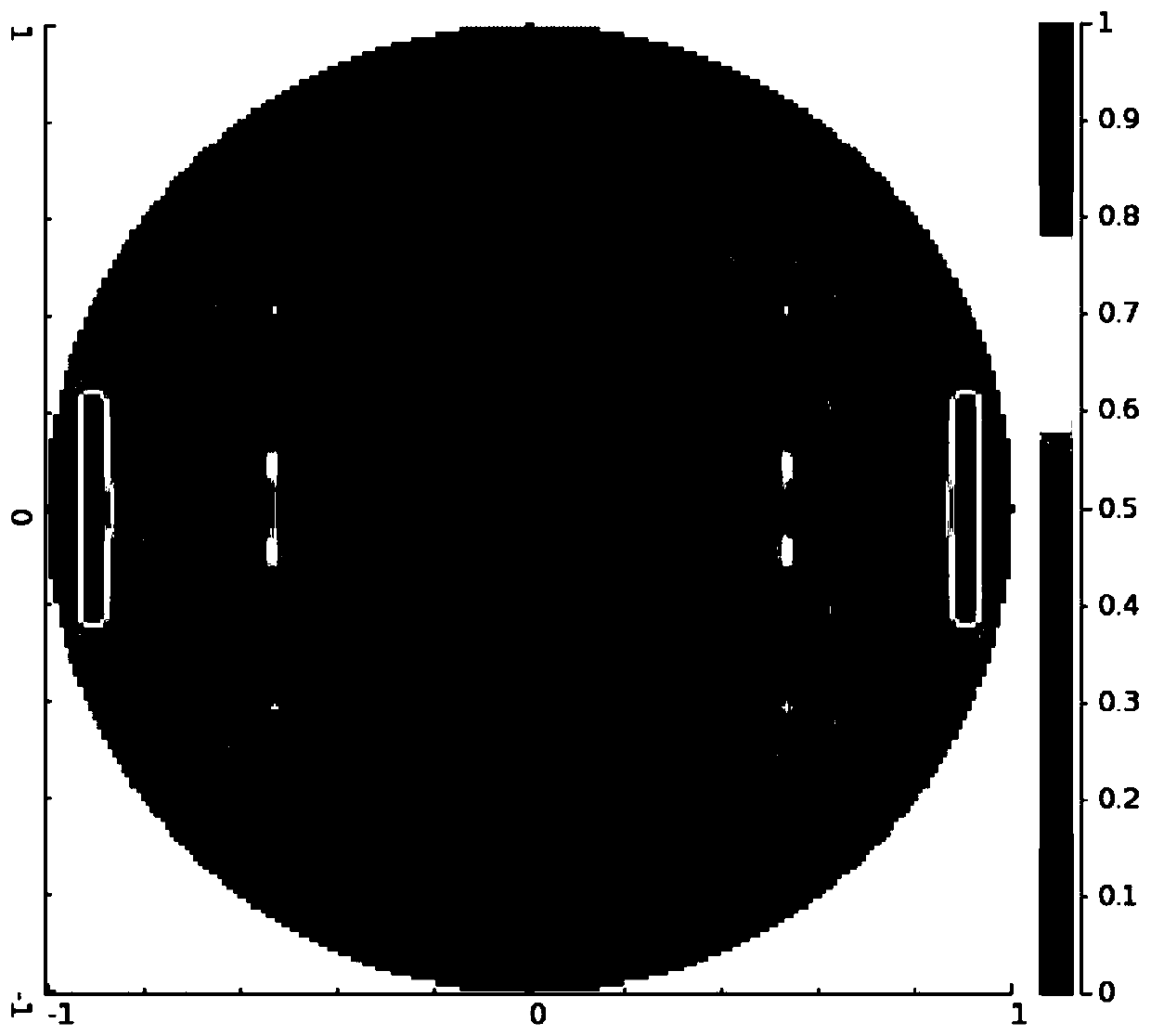

[0056] Step 2: Under the above parameter settings, use professional simulation software to perform collaborative optimization of light source mask (SMO) to obtain the optimized free light source (freeform source1), and analyze the data to fi...

Embodiment 2

[0073] The resolution limit size of the 193nm immersion lithography technology is 76nm, and this embodiment uses a test pattern with a minimum period of 80nm. The simulation software uses the tachyon SMO function of ASML Brion to realize the optimization simulation of the light source mask.

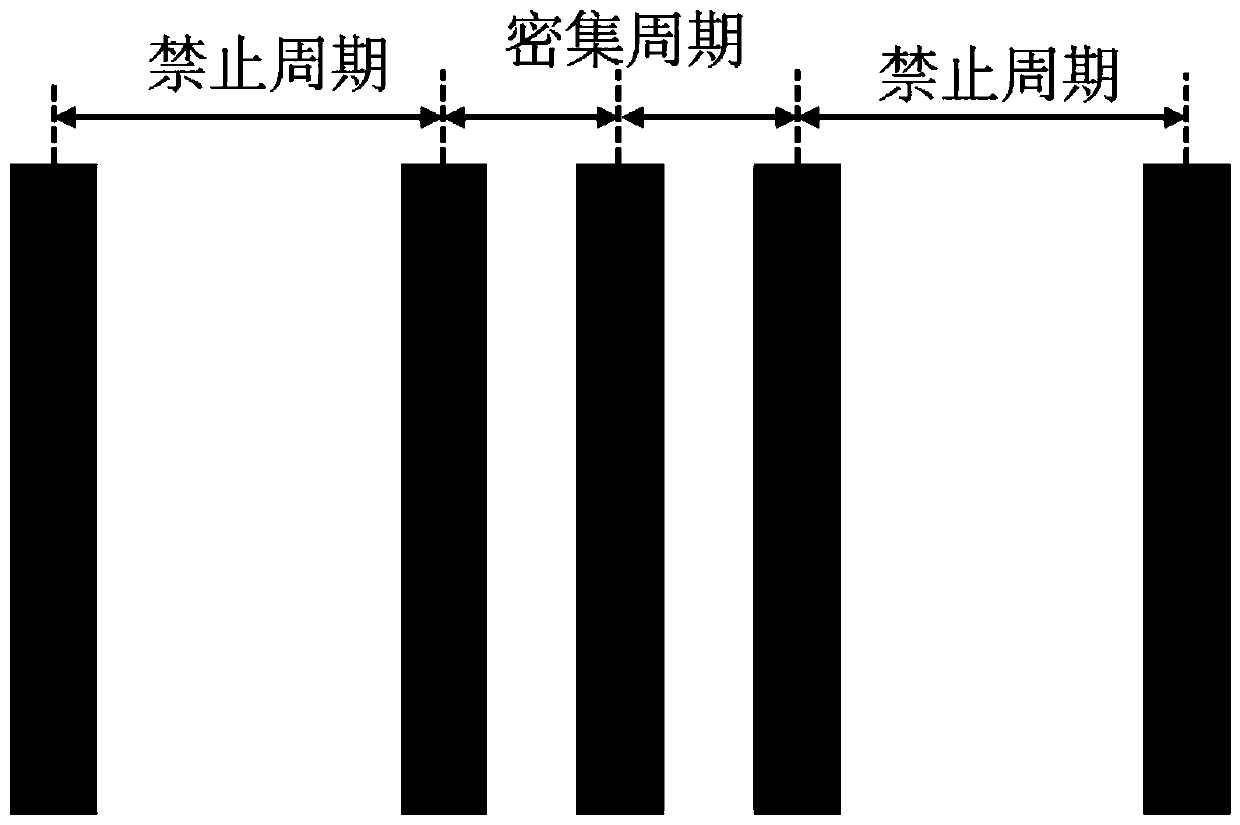

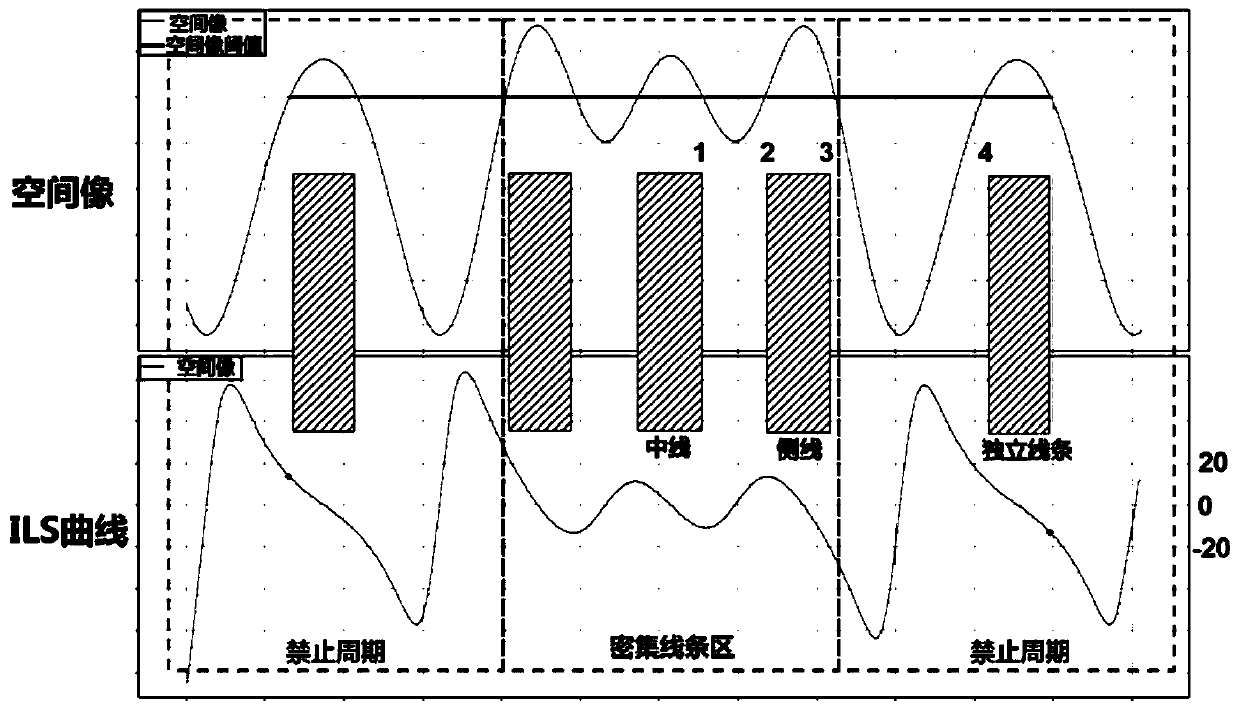

[0074] In the photolithography process, for the forbidden periodic pattern (forbidden pitch, FP), it can be solved by properly reducing the radius of the light source and sacrificing some critical dimensions of the process window. On the contrary, for small-sized key graphics, it can be solved by appropriately increasing the radius of the light source. Therefore, due to the competitive relationship between FP and critical dimension graphics, it is impossible to balance the graphics where the two situations coexist by modifying the light source at the same time, and the graphics that combine dense periodic lines and FP (FDA graphics, such as figure 1 shown) has become an extremely difficu...

Embodiment 3

[0096] A specific embodiment of the present invention discloses a method for finding out the lithography forbidden period (forbiddenpitch, FP) by calculation simulation, such as Figure 14 shown, including the following steps:

[0097] Step 1: Obtain a test pattern (test pattern), mainly a one-dimensional variable-period line (through pitch) pattern within a certain range, and the line width (critical dimension, CD) is the key line width (ie, key dimension) of the lithography node , for example, the actual key line width of the 14nm node is 38nm, and the period (pitch) should include as much as possible;

[0098] Step 2: Set initial simulation light source parameters (for example, a circular light source or a ring light source is used as the initial light source, and a ring light source is used as the initial light source in this embodiment) and related simulation parameters, such as the model of the lithography machine, NA (numerical aperture) value, Reticle parameters and p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More