Array substrate and manufacturing method thereof

A technology of an array substrate and a manufacturing method, applied in the field of panels, can solve the problems of a large area occupied by a driving circuit, reducing the size of a frame of a display panel and a pixel size, etc., and achieve the effect of reducing the size of the occupied area, reducing the size of the frame, the size of the pixel, and reducing the size of the capacitor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

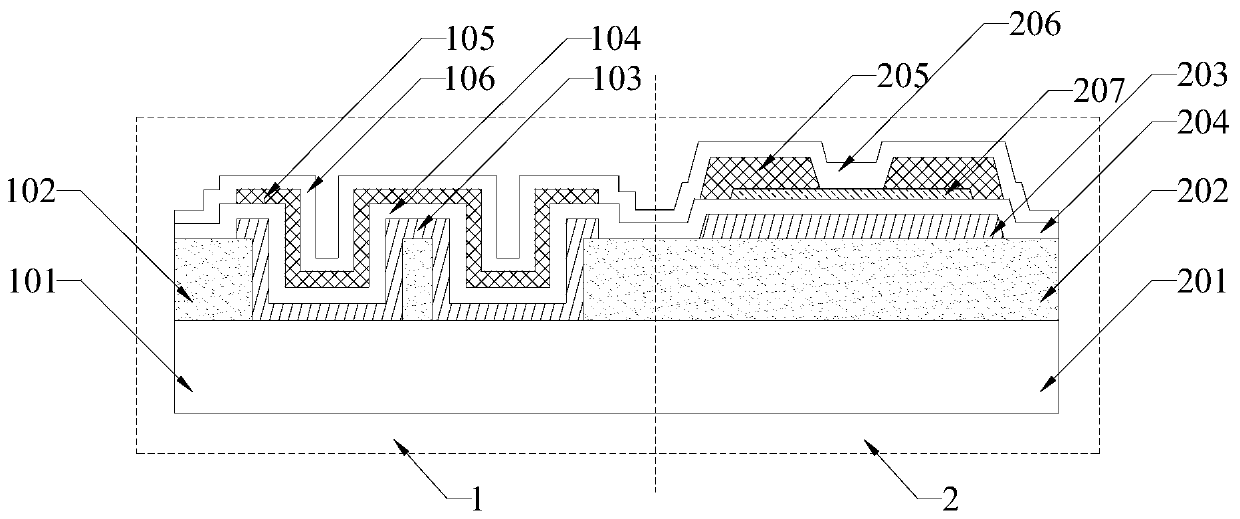

[0056] Please refer to figure 1 , Embodiment 1 of the present invention is:

[0057] An array substrate, comprising a capacitive region structure 1, the capacitive region structure 1 comprising a first substrate 101 and a first buffer layer 102;

[0058] The first buffer layer 102 is provided with two via holes, the two via holes are filled with the first gate metal layer 103, and the first gate metal layer 103 is far away from the first substrate. A first gate insulating layer 104 , a first source metal layer 105 and a first passivation layer 106 are sequentially stacked on one side of the 101 .

[0059] It also includes a TFT regional structure 2, the TFT regional structure 2 includes a second substrate 201, on the surface of the second substrate 201, a second buffer layer 202, a second gate metal layer 203, a second gate An electrode insulating layer 204, an active layer 207, a second source metal layer 205, and a second passivation layer 206, the second gate insulating l...

Embodiment 2

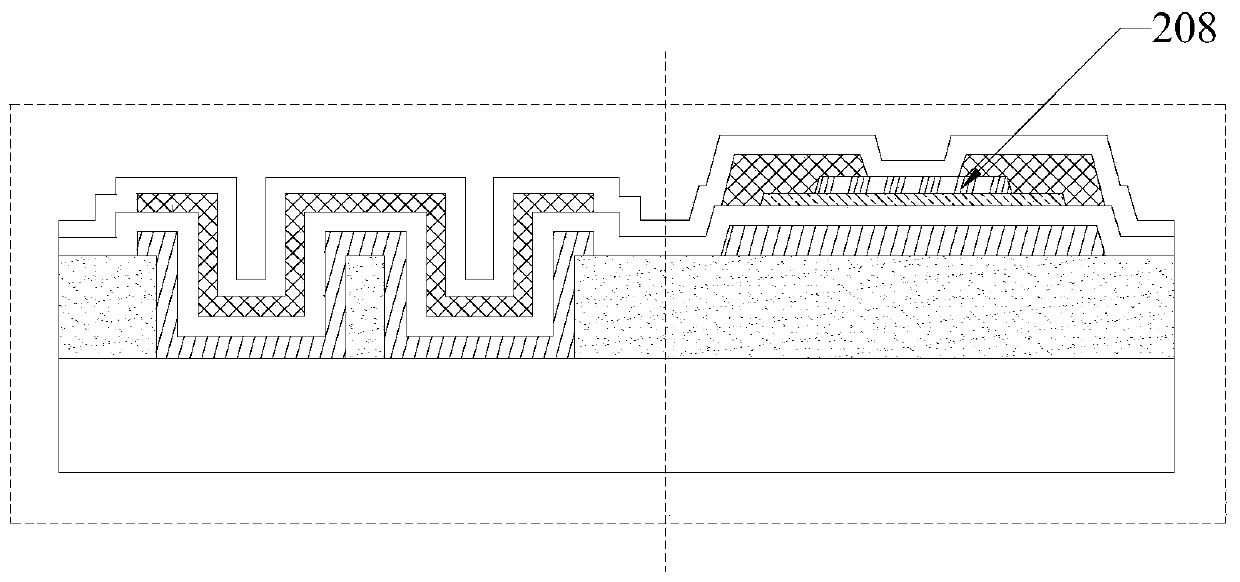

[0064] Please refer to figure 2 , the second embodiment of the present invention is:

[0065] The difference between Embodiment 2 and Embodiment 1 is that: the TFT region structure 2 further includes a second etch barrier layer 208, and the second etch barrier layer 208 is disposed on the second source metal layer 205 and the active layer 207 In between, the second etch barrier layer 208 is in contact with the second source metal layer 205 , the active layer 207 and the second passivation layer 206 respectively.

Embodiment 3

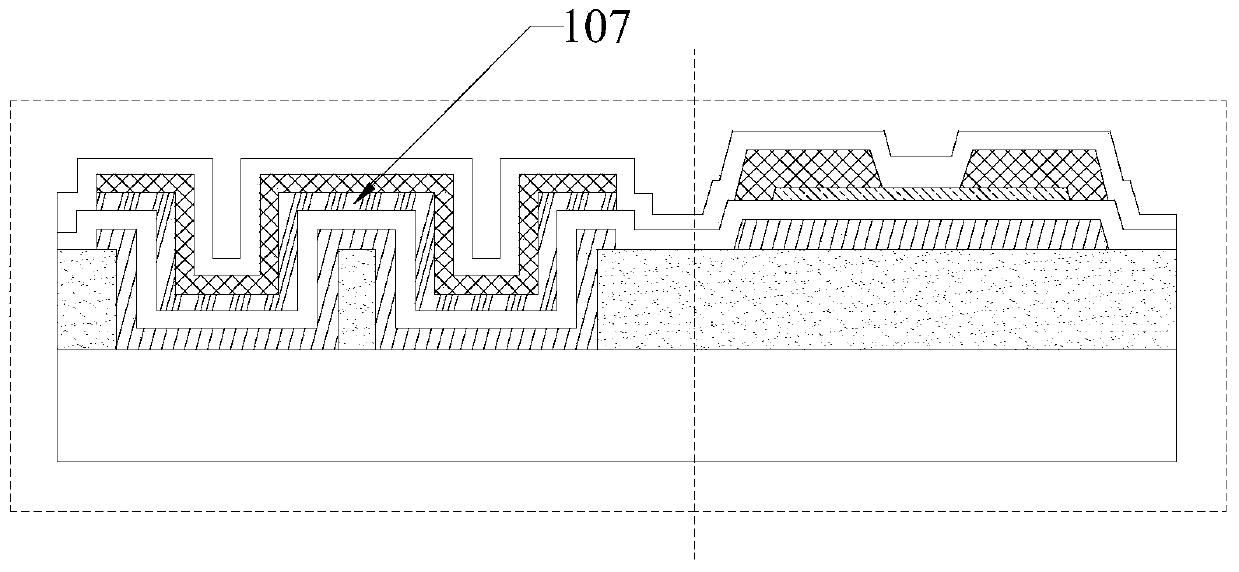

[0066] Please refer to image 3 , Embodiment three of the present invention is:

[0067] The difference between the third embodiment and the first embodiment is that the capacitive region structure 1 further includes a first etch barrier layer 107, and the first etch barrier layer 107 is disposed on the first gate insulating layer 104 and the first source metal The layers 105 are in contact with the first gate insulating layer 104 and the first source metal layer 105 respectively.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More