Semiconductor device prepared by using diffusion type SOI silicon wafer and preparation method thereof

A technology for semiconductors and silicon wafers, which is applied in the field of semiconductor devices and their preparation, and can solve the problems of high requirements for polishing surface control and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

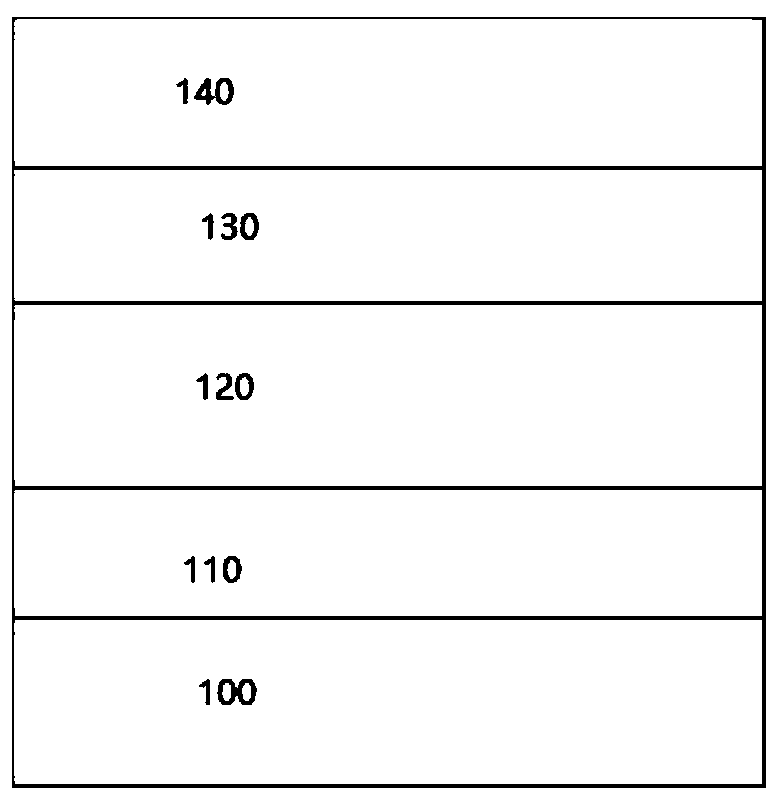

Image

Examples

Embodiment

[0018] Take a single-sided polished N-type single wafer (resistivity 2Ω.cm, thickness 300um), pass POCL3 diffusion source at 1100°C for 30 minutes, oxidize, the oxide layer thickness is 0.5um, and take another N+ type single wafer (thickness 450um) chemical corrosion, RCA cleaning, Boil Concentrated Nitric Acid , spin dry, stick the two pieces together, bake in an oven at 200°C for 2 hours, then put them in a diffusion furnace at 1200°C for 6 hours, thin and polish until the thickness of the N-zone is 8um. The obtained diffusion zone is 13um, and the width of the transition zone 4um. Oxidize the polished surface at 1000°C to a thickness of 1um, photolithographically conduct the channel, etch the oxide layer, pass the POCL3 diffusion source at 1100°C for 30 minutes, and then put it in a diffusion furnace at 1200°C for 5 hours. The resulting diffusion area is 10um, which is the same as the diffusion sheet The N+ regions are connected. The other steps adopt the general planar ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More