A multi-level selection structure applied to antifuse fpga

A technology of selecting structure and anti-fuse, applied in special data processing applications, architecture with a single central processor, electrical digital data processing, etc., can solve problems such as lack of radiation resistance and unsatisfactory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

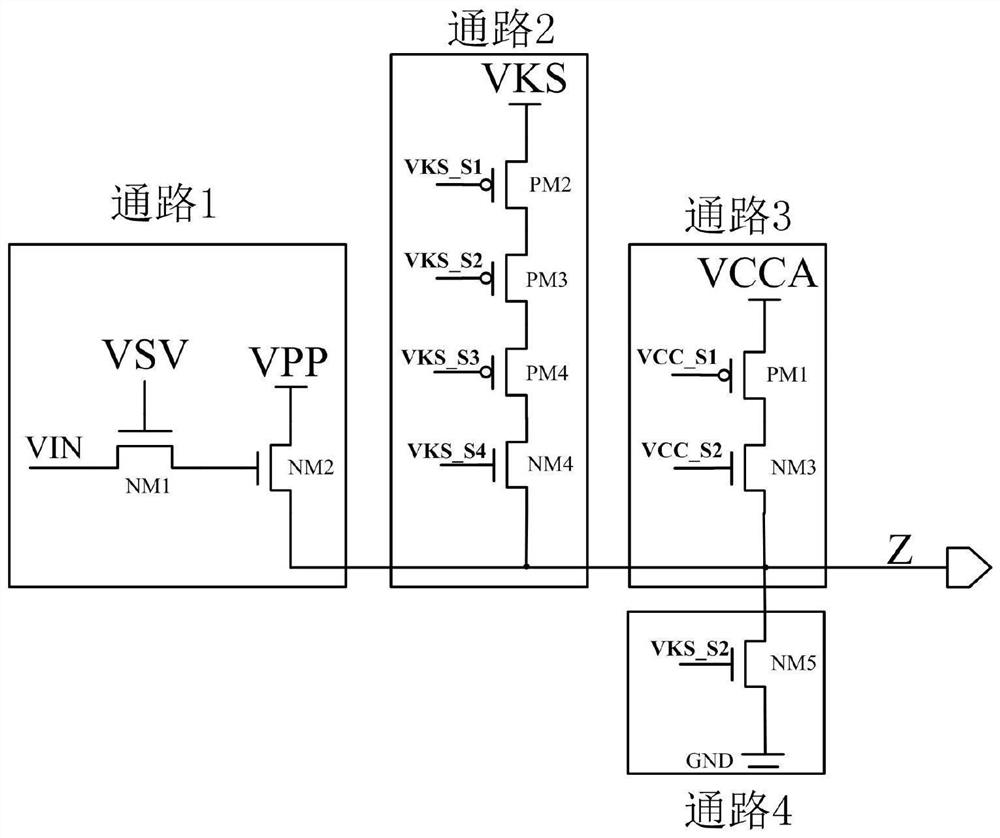

[0031] The invention provides a multi-level selection structure applied to antifuse FPGA. Such as figure 1 As shown, the multi-level selection structure includes 5 types of voltage sources, which are the programming voltage VPP of the antifuse, the voltage VSV for controlling the opening and closing of the programming pass transistor, and the voltage VKS for precharging the antifuse. (1 / 2 VPP, also called half programming voltage), the voltage VCCA used for normal operation after antifuse programming, has a low voltage GND, which provides low voltage for antifuse unit programming.

[0032] read on figure 1 , in the first channel 1, during the programming process of the antifuse, a programming voltage VPP is applied to one end of the antifuse to be programmed for high-voltage programming, and a conductive filament is formed inside the MTM antifuse unit, which can realize permanent conduction. The input signal VIN of the NMOS transistor NM1 comes from the upper level conversi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More