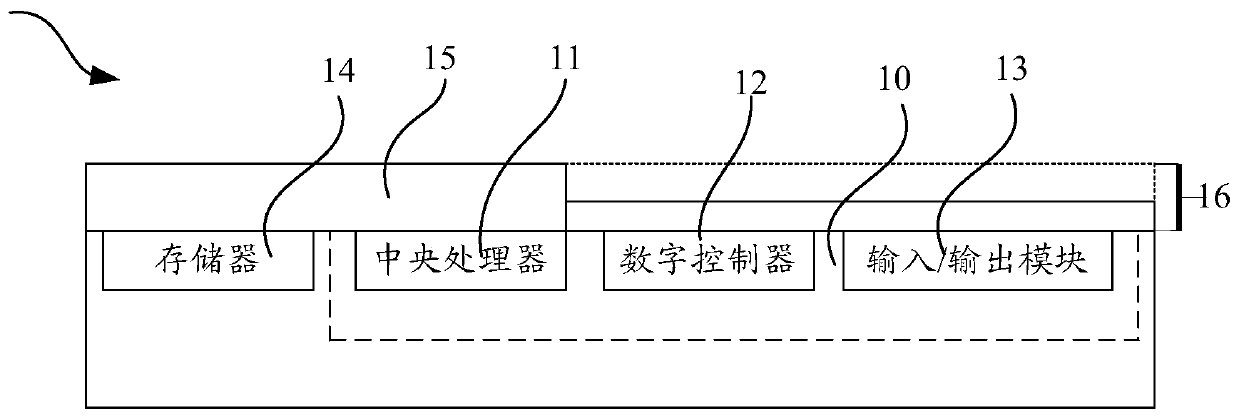

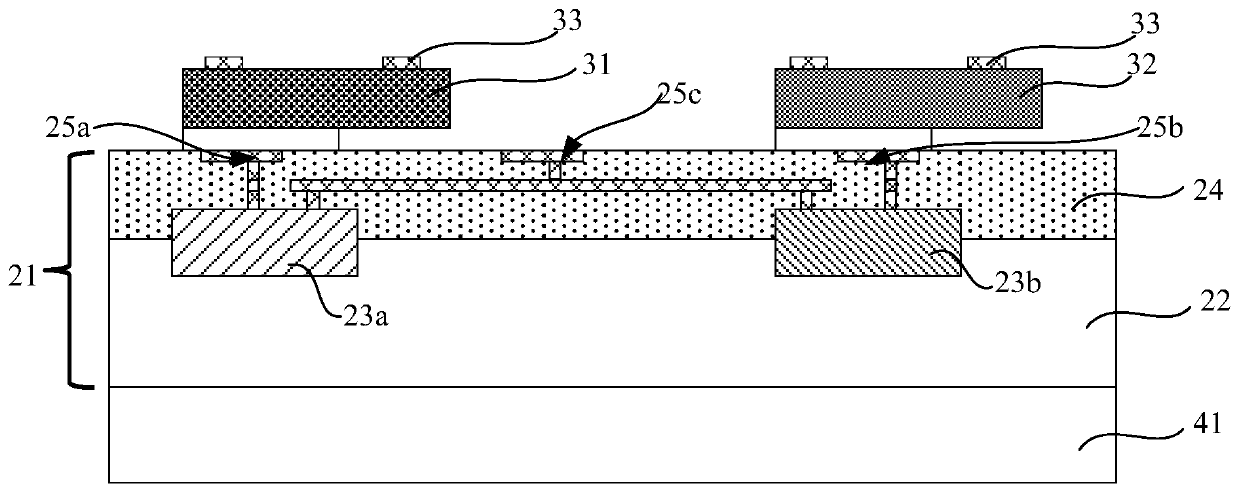

[0005] (1) The SoC process used by the MCU is the result of the process compatibility of the various modules contained in the MCU, but in fact there are great differences in the process of some modules. For details, please refer to Figure 1B , in MCU1, including

central processing unit (logicCore) 11, logic controller (logic controller) 12, input / output module 13 and modules such as various interfaces and control algorithms) etc. logic part (logic) 10 process and

instruction memory The process is very different. When the MCU 1 only has the logic part 10, the number of

layers with the corresponding

layout structure in the MCU1 is 28-30

layers (corresponding to 28-30 masks), and when the MCU 1 except the logic part 10. When there are other non-logic devices or modules, the number of

layers with a corresponding

layout structure in the MCU 1 will increase accordingly (that is, usually correspondingly increase 5 or more photomasks), for example, the logic part 10 After the

instruction memory 14 is compatible, the number of layers with the corresponding

layout structure in the MCU 1 will change from about 30 layers to about 40 layers, and the added additional layer 15 has an electrical interconnection for electrically connecting the

instruction memory 14 and the central

processing unit 11. The connection structure (not shown, it can also be said to be wiring), that is, the number of masks for manufacturing the MCU1 will change from about 30 to about 40, resulting in a sharp increase in plate-making costs

[0006] (2) The layout layer added due to the different processes of some modules objectively leads to the fact that the back-channel layout layer on the top layer of some modules is often meaningless in the back-end interconnection process and does not require wiring, but in order to ensure the consistency of the process stability, it is necessary to add a large number of dummy structures (dummy) in the subsequent layer corresponding to these modules, and these dummy structures themselves are a waste of waste of materials and time, for example Figure 1B As shown, when the MCU1 only has the logic part 10, the number of layers with the corresponding layout structure is 28 layers. After the central

processing unit 11 is compatible with the instruction memory, 5 layers are added in the MCU 1 with the corresponding layout structure of the subsequent process. (that is, the wiring that electrically connects the instruction memory 14 and the central

processing unit 11) of the additional layer 15, at this time, the additional layer 15 (

total thickness is the μm level) that increases is in the logic part 10 of the MCU 1 except the central processing unit 11 The module does not need, but due to the

planar process, that is, additional layers 16 will be formed on the top of the modules other than the central processing unit 11 in the logic part 10, and the additional layers 16 will have the same number of layers and thickness as the additional layers 15 , and a large number of dummy structures (dummy, not shown) need to be placed in the additional layer 1, resulting in waste

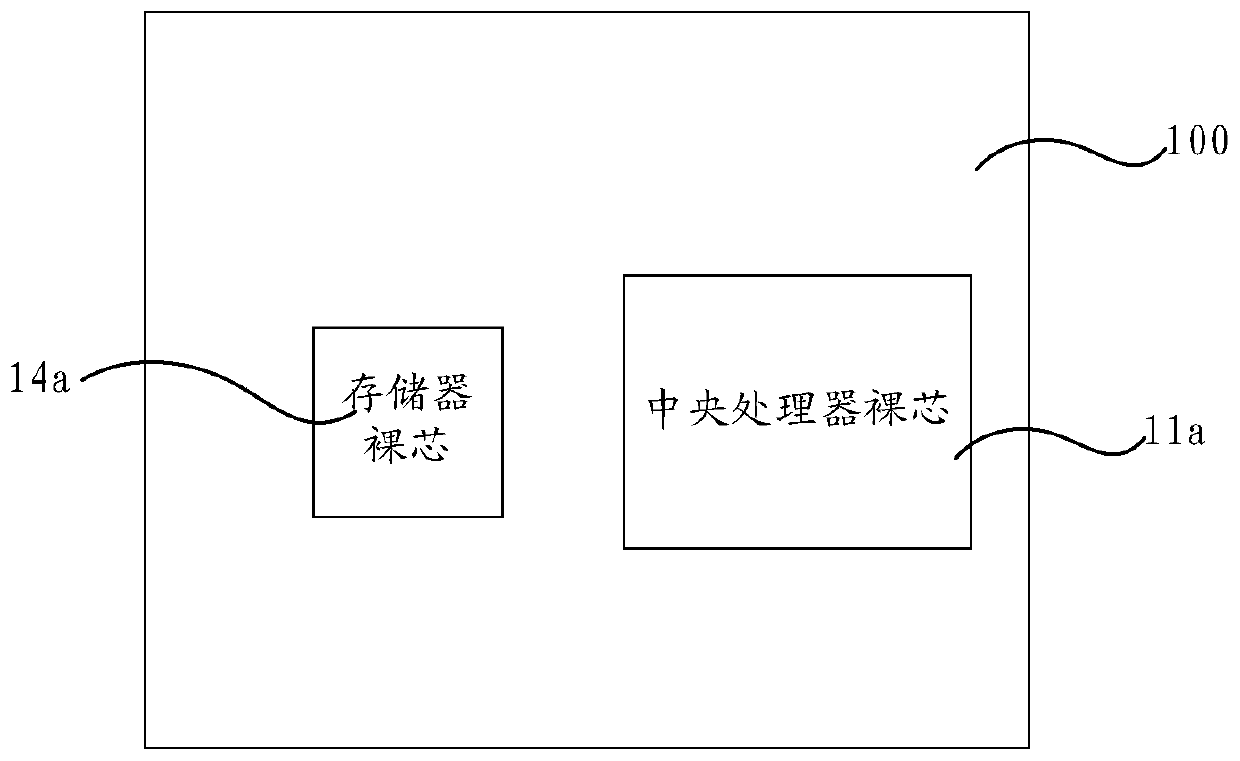

[0007] (3) When the MCU is integrated in SoC mode, the lead wire between the instruction memory and the central processing unit is too long, which limits the improvement of the access speed of the instruction

Specifically, please refer to Figure 1B , because the MCU1 is integrated in an SoC manner, its instruction memory 14 needs to be distributed side by side with the central processing unit 11, that is, the instruction memory 14 is separately packaged outside the central processing unit 11, and then the instruction memory 14, the central processing unit 11, and the logic controller 12 1. On the input / output module 13, an electrical interconnection structure (not shown, usually including conductive contact plugs and

metal interconnection wires) for realizing the

electrical connection between the instruction memory 14 and the central processing unit 11 is manufactured, the electrical interconnection structure That is, it is formed in the additional layer 15. Obviously, the electrical interconnection structure includes a part (not shown) drawn vertically upward from the central processing unit 11, a part (not shown) drawn vertically upward from the instruction memory 14, and connections In the horizontal part (not shown) between these two parts, the length of the electrical interconnection structure is too long relative to the straight

line segment between the two points of the instruction memory 14 and the central processing unit 11, thus causing the simplification of instructions. Read and store speeds are limited and cannot be further improved

Login to View More

Login to View More  Login to View More

Login to View More